-

Изобретение относится к импульсной технике и предназначено для по- с троения цифровых логических уст- . роиств.

Цель изобретения - уменьшение мощности, потребляемой логическим элементом, путем уменьшения тока потребления при трех комбинациях значений входных переменных.

На чертеже представлена принципи альная электрическая схема предлагаемого логического элемента.

Логический элемент содержит первый и второй входные транзисторы 1 и 2, базы которых через первый и второй резисторы 3 и 4 подключены к шине 5 питания, эмиттеры подключены к первому и второму входам 6 и 7 устройства, а коллекторы соединены с базами соответственно первого и второго промежуточных транзисторов

8и 9, коллекторы которых подключе- нь: к входу неинвертирующего выходного каскада 10, и через третий резистор 11 подключены к шине. 5 питани Эмиттер первого промежуточного транзистора 8 через четвертьй резистор

12 подключен к общей шине 13, а эмиттер второго промежуточного транзистора 9 соединен с базой двухэмиттерно- го транзистора 1А, первый и второй эмиттеры которого соединены с базами соответственно первого В и второго

9промежуточных транзисторов, а коллектор подключен к входу инвертирующего выходного каскада 15 и через чевертый резистор 16 к общей шине 13. Неинвертирующий выходной каскад 10 содержит транзистор 17, база которого соединена с входом каскада, коллектор соединен с шиной 5 питания и коллектором выходного транзистора

18, эмиттер которого соединен с выходом 19 неинвертирующего выходного каскада и эмиттером выходного р-п-р- транзистора 20, коллектор которого подключен к общей шине 13, база к катоду диода 21 и через резистор 22 - к общей шине 13. Анод диода 21 соединен с эмиттером транзистора 17, база которого соединена с базой выходного транзистора 18. Инвертирующий выходной каскад 15 содержит первый транзистор 23, база которого соединена с пходом каскада, эмиттер подключен к общей шине 13, коллектор к базе второго выходного транзитора 24 и через резистор 25 - к ши

5

0

5

не 5 питания, а коллектор второго выходного транзистора 24, через резистор 26 соединен с пгиной 5 питания, эмиттер подключен к выходу 27 инвертирующего выходного каскада и соединен с коллектором третьего выходного транзистора 28, база которого соединена с входом каскада, эмиттер подключен к общей шине 13.

Логический элемент работает следующим образом.

Пусть В исходном состоянии на входах 6 и 7 присутствует высокий потенциал, что соответствует значению логических единиц. В этом случае первый и второй входные транзисторы 1 и 2 находятся в инверсном активном режиме и их базовые токи, величина которых определяется номиналами первого и второго резисторов 3 и 4 обусловливает открытое состояние промежуточных транзисторов 8 и 9. При этом на коллекторах промежуточных транзисторов 8 и 9 и входе выходного каскада 10 присутствует низкий потенциал. В результате транзисторы 17 и 18 оказываются в состоянии отсечки, база выходного р-п-р транзистора 20 оказывается соединенной с общей шиной 13 через резистор 22, чем обеспечивается открытое состояние выходного р-п-р транзистора 20, что соответствует состоянию логического О на выходе 19. Для гарантированного состояния выходного кас- када 10 может быть включен дополнительный диод между коллекторами транзисторов 8 и 9 .и входом каскада 10. Следовательно, неинвертирующий выходной каскад 10 повторяет сигнал, поступающий на его вход.

На базах промежуточных транзисторов 8 и 9 присутствует высокий потенциал, что обеспечивает инверсный режим работы двухэмиттерно- го транзистора 14, и на входе инвертирующего выходного каскада 15 присутствует высокий потенциал. В базы транзисторов 23 и 28 поступает ток через коллекторный переход двухэмит- терного транзистора 14, чем обеспечивается открытое состояние транзисторов 23 и 28 и закрытое состояние г ранзистора 24, так как база транзистора 24 соединена с коллектором открытого транзистора 23, имеющим низкий потенциал. Выход 27 подключается через открытый транзистор 28 к

0

5

0

0

5

общей шине 13, что соответствует состоянию логического О,

Если на входах 6 и 7 присутствует низкий потенциал, то первый и второй входные транзисторы 1 и 2 открыты, на их коллекторах низкий потенциал, что обусловливает состояние отсечки промежуточных транзисторов

8и 9.

На коллекторах промежуточных транзисторов 8.и 9 высокий потенциал , неинвертирующий выходной каскад 10 повторяет сигнал, поступающий на его вход, и на выходе 19 присутствует высокий потенциал, т.е. логическая 1.

На эмиттерах промежуточных транзисторов 8 и 9 присутствует низкий потенциал, двухэмиттерный транзистор 14 закрыт, и на входе инвертирующего выходного каскада 15 присутствует низкий потенциал и, следовательно, на выходе 27 присутствует высокий потенциал, т.е. логическая 1.

Если на входах 6 и 7 присутствуют разные потенциалы, то на входе неинвертирующего выходного каскада 10 присутствует низкий потенциал, так как один из промежуточнЬ1х транзисторов 8 и 9 открыт. Неинвертирующий выходной каскад 10 повторяет сигнал, поступающий на его вход, и на выхо- Де 19 присутствует низкий потенциал, т.е. логическая 1. На коллекторе двухэмиттерного транзистора 14 и вхо де инвертирующего каскада 15 присутствует нулевой потенциал, так как если второй промежуточный .транзистор

9закрыт, а первый промежуточный транзистор 8 открыт, то в базу двух- змиттерного транзистора 14 не поступает ток эмиттера второго промежуточного транзистора 9, а когда второй промежуточный транзистор 9 открыт,

а первый промежуточный транзистор 8 закрыт в базу двухэмиттерно.го транзистора 14 поступает ток эьшттера второго промежуточного транзистора 9, который ответвляется через первый эмиттер двухзмиттерного транзистора 14 и открытый первый входной транзистор 1 на первый вход 6 элемента.

На выходе инвертирующего каска- да 15 присутствует высокий потенциал, т.е. логическая 1.

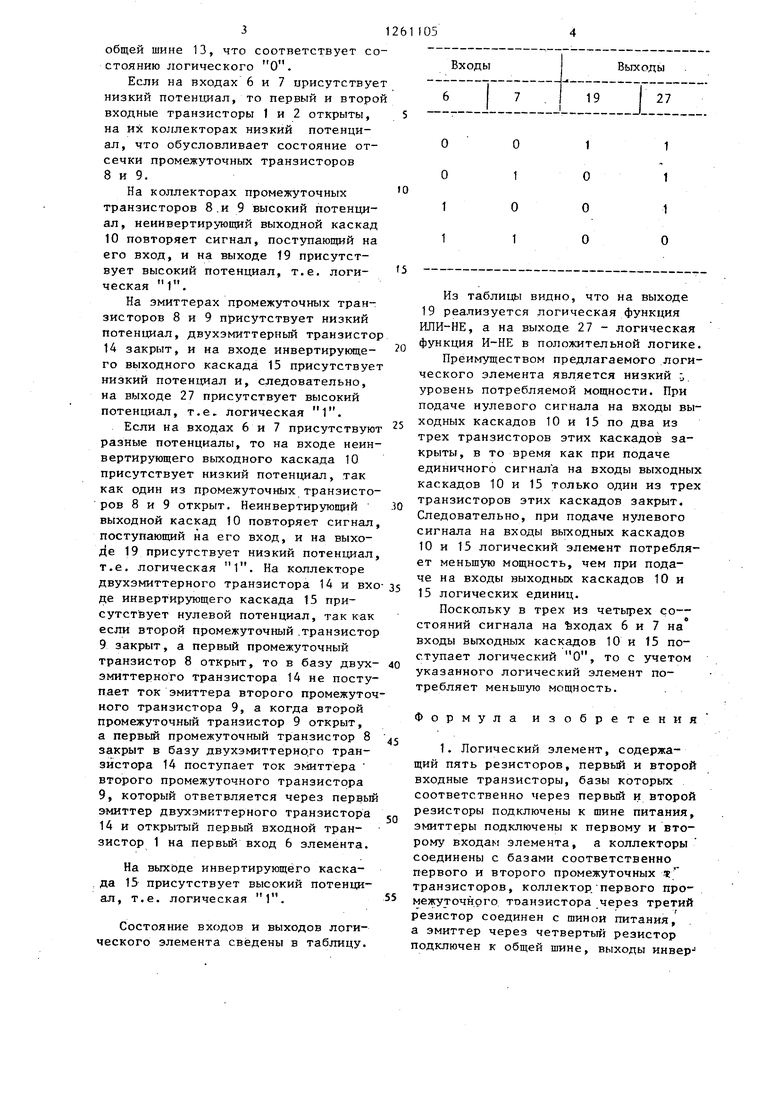

Состояние входов и выходов логического элемента сведены в таблицу.

О О

1 1

О

1 О

1

1

о о о

1 1 1 о

f5

20

5

5

0

0

5

0

5

Из таблицы видно, что на выходе 19 реализуется логическая функция ИЛИ-НЕ, а на выходе 27 - логическая функция И-НЕ в положительной логике.

Преимуществом предлагаемого логического элемента является низкий г,, уровень потребляемой мощности. При подаче нулевого сигнала на входы выходных каскадов 10 и 15 по два из трех транзисторов этих каскадов закрыты, в то время как при подаче единичного сигнала на входы выходных каскадов 10 и 15 только один из трех транзисторов этих каскадов закрыт. Следовательно, при подаче нулевого сигнала на входы выходных каскадов 10 и 15 логический элемент потребляет меньшую мощность, чем при подаче на входы выходных каскадов 10 и 15 логических единиц.

Поскольку в трех из четьфех со- стояний сигнала на входах 6 и 7 на входы выходных каскадов 10 и 15 поступает логический О, то с учетом указанного логический элемент потребляет меньшую мощность.

Формула изобретения

1. Логический элемент, содержащий пять резисторов, первый и второй входные транзисторы, базы которых соответственно через первый и второй резисторы подключены к шине питания, эмиттеры подключены к первому и второму входам элемента, а коллекторы соединены с базами соответственно первого и второго промежуточных че транзисторов, коллектор. первого про- мезкуточнрго тоанзистора через третий резистор соединен с шиной питания, а эмиттер через четвертый резистор подключен к общей шине, выходы инвертирующего и неинвертирующего выходных каскадов подключены соответственно к выходу и дополнительному выходу элемента, отличающий- с я тем, что, с целью уменьшения потребляемой мощности, в него введен двухэмиттерный транзистор, первый и второй эмиттеры которого соединены с базами соответственно первого и второго промежуточных транзисторов, коллектор - с входом инвертирующего выходного каскада и через резистор - с- общей шиной, а база соединена с эмиттером второго промежуточного транзистора, коллектор которого соTJ

единен с коллектором первого проме- жутотного тарнзистора и входом

Редактор С.Лисина

Составитель А.Янов Техред Л.Олейник

Заказ 5244/57 Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб. , д. 4/5

- - - - ..«. -,

.Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

неинвертирующего выходного кас- |Када.

2. Элемент по п.1, о т л и ч а ю- щ и и с я тем, что инвертирующий 5 выходной каскад содержит первый транзистор, база которого соединена с входом каскада, эмиттер подключен к общей шине, коллектор - к базе второго выходного транзистора и че10 рез резистор - к шине питания, коллектор второго выходного транзистора через резистор соединен с шиной питания, эмиттер подключен к выходу каскада и коллектору третьего выход15 ного транзистора, база которого соединена с входом каскада, а эмиттер подключен к общей шине.

Корректор М.Шароши

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент | 1983 |

|

SU1138941A1 |

| Логический элемент | 1988 |

|

SU1529441A1 |

| Логический элемент | 1985 |

|

SU1262717A1 |

| Логический элемент | 1988 |

|

SU1554136A1 |

| Буферное логическое ТТЛ устройство | 1981 |

|

SU993477A1 |

| Логический элемент "запрет" | 1976 |

|

SU587627A1 |

| Устройство согласования | 1983 |

|

SU1138942A1 |

| Цифровая полупроводниковая интегральная схема с тремя состояниями на выходе | 1980 |

|

SU900454A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU978200A1 |

| Триггерный логический элемент И/И-НЕ | 2022 |

|

RU2789166C1 |

Изобретение относится к импульсной технике и предназначено для построения цифровых логических устройств. Цель изобретения - уменьшение мощности, потребляемой логическим элементом, достигается путем уменьшения тока потребления при трех комбинациях значений входных перемен- ньсх. Логический элемент (ЛЭ) содержит входные транзисторы 1 и 2, входы 6 и 7, промежуточные транзисторы 8 и 9, неинвертирующий выходной каскад 10 на транзисторах 17, 18 и 2(7 и диоде 21, инвертирующий выходной каскад 15 на транзисторах 23, 24 и 28. Для достижения поставленной цели в ЛЭ введен двухэмиттерный транзистор 14. Выходом неинвертирующего каскада является клемма 19, инвертирующего - 27. Используемые в ЛЭ восемь резисторов показаны на чертеже. 1 1 з.п. ф-лы. 1 ил. k/) Кл

| Преснухин Л.Н | |||

| и др | |||

| Расчет элементов цифровых устройств | |||

| М.: Высшая школа, 1982, с | |||

| Прибор, автоматически записывающий пройденный путь | 1920 |

|

SU110A1 |

| Логический элемент | 1983 |

|

SU1138941A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-09-30—Публикация

1984-07-13—Подача