315

Изобретение относится к вычислительной технике и может быть использовано для адресации памяти при ускоренной реализации автоматных ото- бражений.

Цель изобретения - расширение функциональных возможностей за счет реализации режима выборочной адресации.

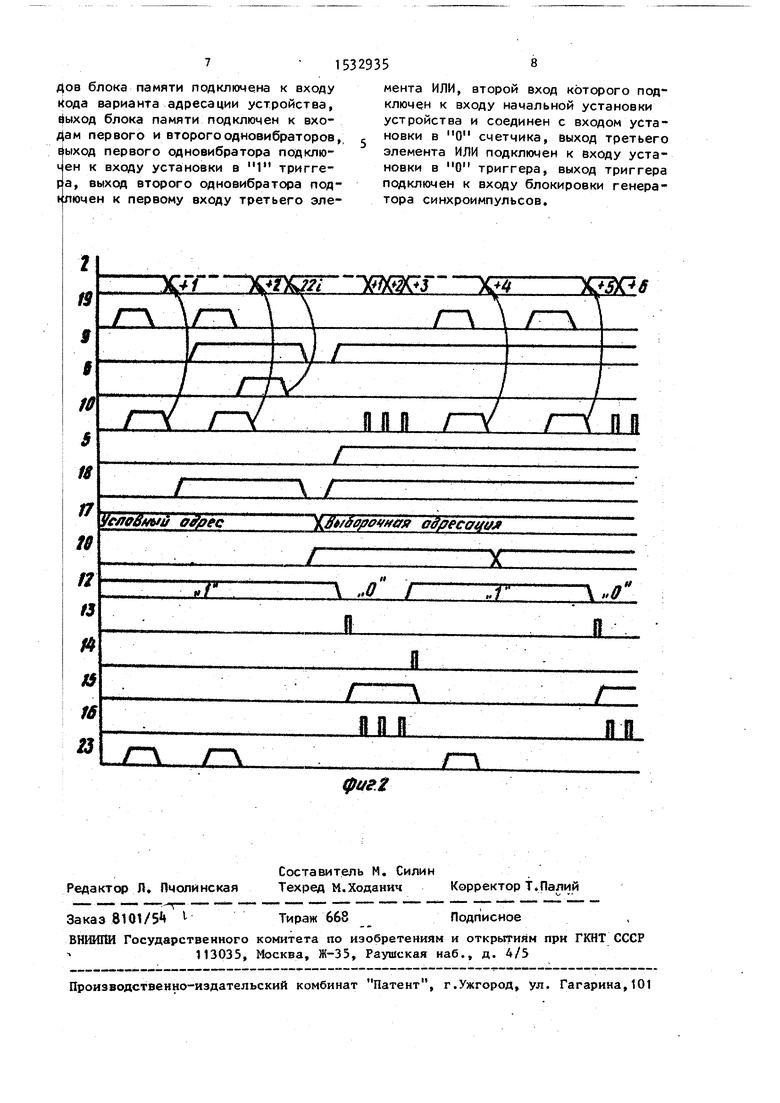

На. фиг. 1 представлена функциональ ная схема устройства; на фиг. 2 - временная диаграмма его работы.

Устройство адресации памяти содержит мультиплексор 1, счетчик 2, группы 3 и элементов И,дешифратор 5, элемент И 6, элементы 7 и 8 задержки, элементы ИЛИ 9-11, блок 12 памяти одновибраторы 13 и 1, триггер 15, генератор 16 синхроимпульсов, группу 17 входов логических условий устройства, входы запроса условного адреса 18,синхроимпульсов 19, кода варианта адресации 20, начальной установки устройства 21, группу 22 входов условных адресов устройства и группу 23 выходов устройства.

При нулевом значении сигнала на входе 18 выход мультиплексора 1 об нуляетсяо

Устройство работает следующим образом.

Обычный режим.

В исходном состоянии в счетчике 2 находится адрес первой ячейки памяти (цепи установки исходного адреса не показаны). По импульсу на входе 19 открывается группа элементов И 4 и адрес из счетчика 2 передается в блок памяти, формирование следующего адреса в этом случае начинается по заднему фронту импульса на выходе элемента 7 задержки, при этом по заднему фронту импульса на выходе элемента ИЛИ 10 содержимое счетчика 2 увеличивается на единицу. Этот код используется в качестве следующего адреса, если не произойдет запись информации а счетчик 2 с выходов мультиплексора 1, После формирования заднего фронта импульса на выходе первого элемента 7 задержки формируется задний фронт импульса на выходе второго элемента задержки 8. Этот импульс проходит через элемент И 6 только в том случае, когда присутствует ненулевой код на выходах мультиплек сора 1, т.е. в случае, если имеется ра зрешакмций сигнал на входе 18, по которому информация с входов 17 пе

,-

15

го

5

-

о

, 30

35

40

45

50

55

редается на адресные входы мультиплексора 1 и он подключает один из входов группы 22 к своим информационным выходам. Вследствие этого появляется сигнал 1 на выходе элемента ИЛИ 9, причем выход дешифратора 5 находится в состоянии О. Поэтому информация с выходов мультиплексора 1 записывается в счетчик 2 по заднему фронту импульса на входе синхронизации, изменяя следующий адрес. Этот адрес выдается на выходы группы 23 при очередном импульсе на входе 19.

Режим выборочной адресации данных,

В этом режиме по входам 17 и 18 выбирается специальный вход из группы 22 (К-й вход группы), который подключается к выходам мультиплексора 1. При этом активизируется вход дешифратора 5, который блокирует по третьему входу элемента И 6 прохождение импульсов на вход синхронизации счетчика 2. Таким образом происходит инициализация режима выборочной адресации данных. При этом при инициализации также предварительно в счетчик 2 по входу синхронизации заносится начальный адрес А0 с входа 22„К (фиг,2) аналогично описанному о В дальнейшем информация, поступающая на выходы 23, зависит от информации, записанной в блоке 12 памяти, на второй группе адресных входов 20 которого установлен некоторый (начальный) код варианта адресации. Вторая группа адресных входов блока 12 памяти адресуется выходами счетчика 2. Поэтому когда активизируется вход выборки блока 12 памяти выходом дешифратора 5, на выходе блока памяти 12 появляется сигнал, нулевое значение которого свидетельствует о необходимости пропуска очередного адреса (маскирование очередного адреса), а единичное значение - о необходимости формирования очередного адреса (в том случае, когда сигнала выборки нет, информационный выход блока 12 находится в состоянии 1).

Таким образом,по заднему фронту импульса на выходе блока памяти ,12 (фиг.2), т.е. при установлении на ее выходе сигнала О формируется импульс первым одновибратором 13, устанавливающий триггер 15. Запускается генератор 16, импульсы на выходе которого, проходя через элемент ИЛИ 10, изменяют состояние счетчика 2 до тех пор, пока его выходные сигналы не выберут из блока 12 памяти очередную ячейку памяти с записанной в ней 1. Причем период импульсов, формируемых генератором 16, много меньше периода тактовых импульсов на входе 22, но больше суммарной задержки элементов ИЛИ 10 и 11, счетчика 2, блока 12 памяти,триггера 16, одновибратора 14. При установлении на выходе блока 12 памяти 1 по переднему фронту этого сигнала одновибратор Ц формирует одиночный импульс, обнуляющий триггер 16. Генератор 16 блокируется нулевым сигналом на выходе триггера 15.

В результате этого в счетчике 2 устанавливается информация о следующем адресе, не замаскированном нулем в соответствующей ячейке блока 12 памяти. Поэтому по импульсу на выходе 19 этот адрес через группу элементов И k передается на выходы 23 устройства. Затем вновь по заднему фронту импульса на выходе элемента задержки 7 изменяется на единицу состояние счетчика 2, в результате чего из блока 12 памяти считывается информация в очередной ячейке. Если она равна единице, состояние устройства не изменяется. Если по следующему импульсу на входе 19 (фиг.2) из блока 12 памяти выбирается ячейка памяти с нулем, одновибратор 13 вновь формирует одиночный импульс, триггер 15 устанавливается и начинается генерация импульсов генератором 16. Снова изменяется состояние счетчика 2 до тех пор, пока из блока 12 памяти не будет считана 1.

Далее устройство работает аналогично. При изменении информации на входах 1 условий снимается активный уровень сигнала на выходе дешифратора 5 и устройство переходит в обычный режим работы, что происходит также при снятии активного сигнала с

входа 18. Далее устройство работает аналогично.

Для смены варианта адресации в режиме выборочной адресации данных изменяется соответствующим образом информация на входах 20.

Формула изобретения

Устройство адресации памяти, содержащее мультиплексор, счетчик, две группы элементов И, элемент И, два элемента задержки, элемент ИЛИ, причем К-й информационный вход мультиплексора подключен к К-му входу условного адреса группы устройства (К 1, М, где М - количество условных адресов), Р - и вход логических условий устройства подключен к первому входу Р-го элемента И первой группы,

5 ( И, где Н - количество логических условий), второй вход и выход которого подключены соответственно к входу запроса условного адреса устройства и к Р-му разряду адресно0 го входа мультиплексора, выход мультиплексора подключен к информационному входу счетчика и к входам первого элемента ИЛИ, выход которого подключен к первому входу элемента

5 И, второй вход которого подключен к выходу первого элемента задержки, вход первого элемента задержки подключен к выходу второго элемента задержки, вход которого подключен к

0 входу синхроимпульсов устройства и соединен с первыми входами элементов И второй группы, выход элемента И подключен к входу синхронизации счетчика, Т-й выход которого подключен к второму входу Т-го элемента И второй группы, (, А, где А - разрядность формируемого адреса), выход которого подключен к Т-му выходу группы устройства, отличаю0 1 е е с я тем, что, с целью расширения функциональных возможностей за счет реализации режима выборочной адресации, в него введены дешифратор, два элемента ИЛИ, блок памяти,

5 два одновибратора, триггер и генератор синхроимпульсов, причем вход дешифратора подключен к выходу мультиплексора, выход дешифратора подключен к инверсному входу элемента И

0 и к входу выборки блока памяти, выход второго элемента задержки под- - ключей к первому входу второго элемента ИЛИ, второй вход которого подключен к выходу генератора синхроимпульсов, выход второго элемента ИЛИ подключен к счетному входу счетчика, первая группа адресных входов блока памяти подключена к выходу счетчика, вторая группа адресных вхо5

5

дов блока памяти подключена к входу Кода варианта адресации устройства, йыход блока памяти подключен к входам первого и второго одновибраторов, ёыход первого одновибратора подключен к входу установки в 1й триггера, выход второго одновибратора подключен к первому входу третьего элемента ИЛИ, второй вход которого подключен к входу начальной установки устройства и соединен с входом установки в О счетчика, выход третьего элемента ИЛИ подключен к входу установки в О триггера, выход триггера подключен к входу блокировки генератора синхроимпульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1989 |

|

SU1633402A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1988 |

|

SU1532939A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1993 |

|

RU2037874C1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| Устройство ввода информации | 1986 |

|

SU1417015A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

Изобретение относится к вычислительной технике и может быть использовано для адресации памяти при ускоренной реализации автоматных отображений. Целью изобретения является расширение функциональных возможностей. Устройство содержит мультиплексор 1, счетчик 2, группы 3, 4 элементов И, дешифратор 5, элемент И 6, элементы задержки 7, 8, элементы ИЛИ 9-11, блок 12 памяти, одновибраторы 13, 14, триггер 15, генератор 16 синхроимпульсов, группу 17 входов логических условий устройства, вход 18 запроса условного адреса, вход 19 синхроимпульсов, вход 20 кода варианта адресации, вход 21 начальной установки устройства, группу 22 входов условных адресов, группу 23 выходов устройства. Цель достигается за счет реализации режима выборочной адресации. 2 ил.

| Авторское свидетельство СССР № , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-12-30—Публикация

1988-05-12—Подача