Изобретение относится к цифровой вычислительной технике и может быть использовано в системах прерывания вы 1ислительных систем, в том числе в управляющих вычислительных нашииах и комплексах.

Цель изобретения - повышение быстродействия устройства.

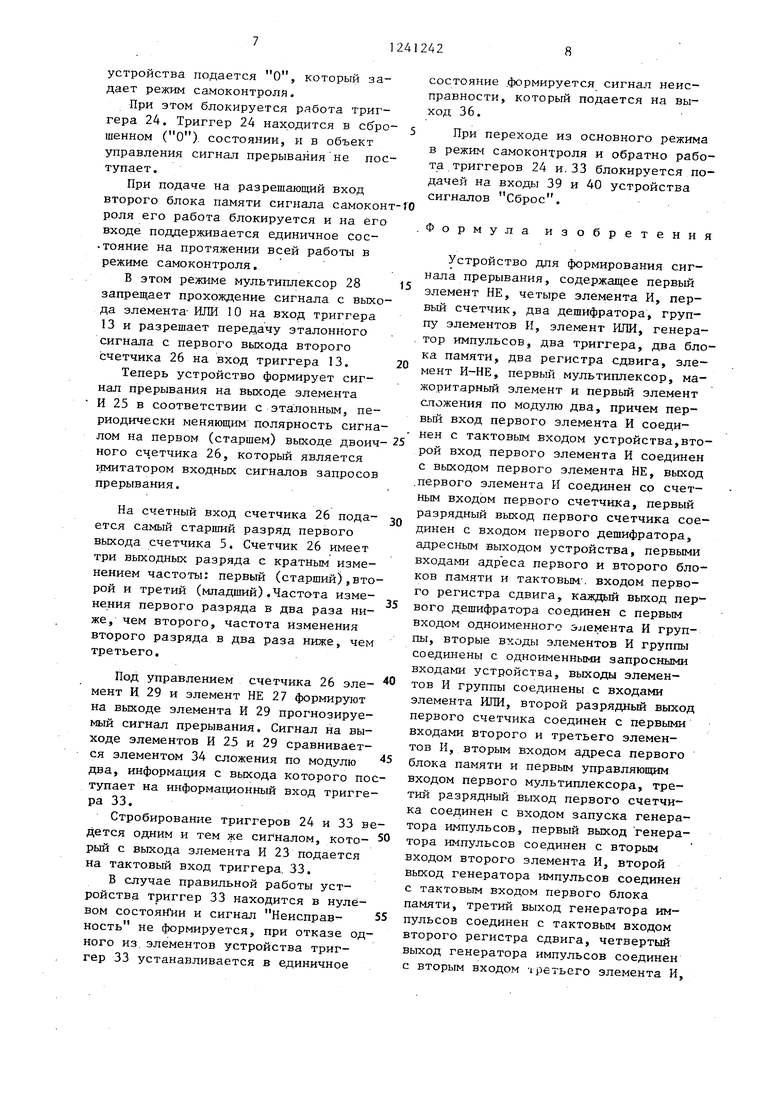

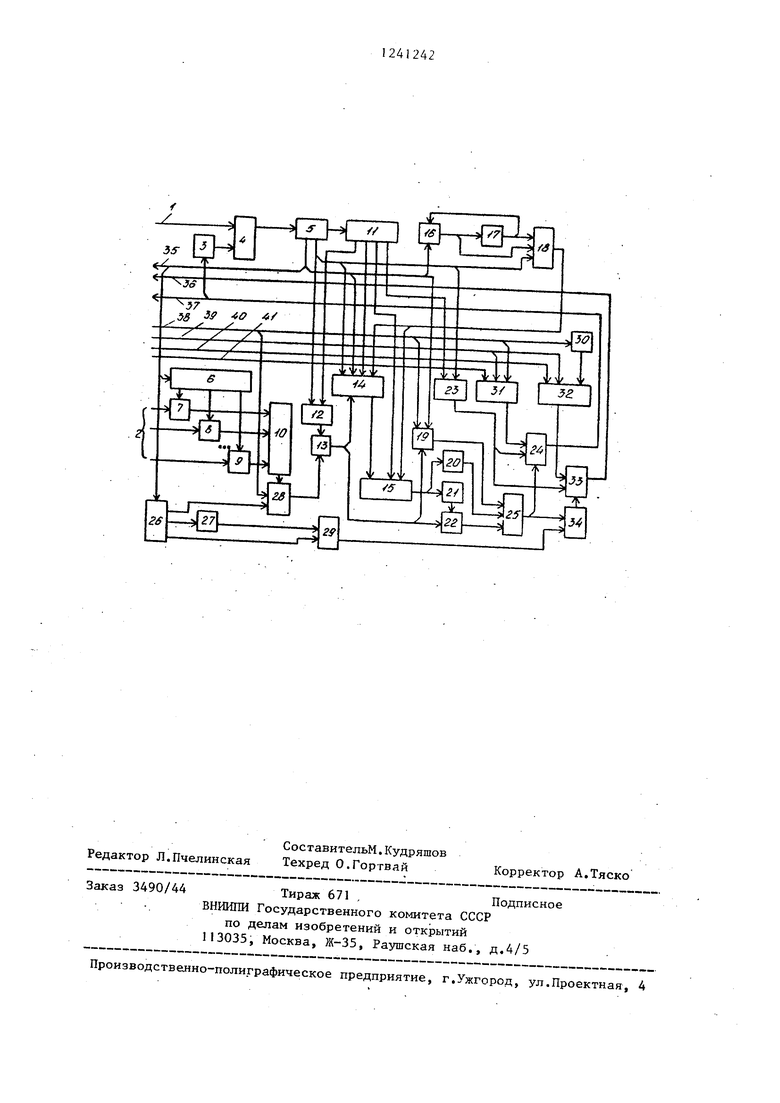

На чертеже приведена структурная схема устройствй.

; :тройство содержит тактовый вхвД 1 устройствам ; группу запросных Входов 2 устройства, элемент НЕ 3, элемент И 4, .ачетчик 5, дешифратор 6 элементы И 7- группы, элемент ИЛИ 10 генератор 11 импульсов, элемент И 12 триггер 13, блок 14 памяти, регистры 15 и 16 сдвига, элемент И-НЕ 17,муль типлексор 18, блок 19 памяти, дешифратор 20, мажоритарный элемент 21, элемент 22 сложения по модулю два, элемент И 23, триггер 24, элемент И 25, счетчик 26, элемент НЕ 27,муль типлексор 28, элемент И 29, элемент НЕ 30, элементы ИЗ и 32, триггер 33, элемент 34 сложения по модулю два, адресный выход 35 устройства, сигнальный выход 36 устройства, выход 37 прерывания устройства,вход 38 режима устройства, вход 39 начального сброса, вход 40 блокировки устройства и ответный вход 41 устройства.

Устройство работает в двух режимах: основной и самоконтроль. Режим работы определяется сигналом, поступающим на вход 38 устройства и далее на разрешающий вход второго блока 19 памяти, управляющий вход второго мультиплексора 28, третий вход шестого элемента И 31 и вход элемен- НЕ 30.

При работе в основном режиме устройство функционирует следующим образом.

Мультиплексор 28 коммутирует сигнал с вьпсода элемента ИЛИ 10 на вход первого триггера 13.

Счетчик 5, на который с некоторой частотой поступают импуЛьсы с входа 1 при помощи первого дещифра- тора 6 и группы элементов И 7-9, в каждом такте проверки наличия запро- са на входах 2 проверяет уровень .прерьшания, номер которого совпадает с. содержимым старших разрядов первого двоичного счетчика 5, поступающим в дешифратор 6 с первого выхода первого двоичного счетчика 5. Эта

41242. 2

проверка уровня прерывания заключается в сравнении значения запросов за три предыдущих периода проверки, хранящихся в блоке памяти 14, с те- 5 кущим.значением запроса и определение факта изменения значения запроса. Если в данном уровне прерывания запрос не изменил значения, то через некоторое время происходит изменение 10 на единицу старших разрядов счетчика 5 и проверяется следующий по порядку уровень прерывания. Если изменяется значе11ие запроса, просмотр прекращается, устанавливается триг- 15 гер 24, с выхода которого на выход 37 подается сигнал прерывания, а содержимое счетчика 5 используется для формирования начального адреса преры- вающей программы на выходе 35. Сиг-- 20 нал с выхода триггера 24 поступает также на элемент НЕ Зи запрещает прохождение импульсов с входа 1 через элемент И 4 на счетный вход счетчика 5, фиксируя его состояние. После 25 передачи управления прерывающей прог- рамме на вход 41 поступает сигнал сбрасывающий триггер 24, и процедура поиска запросов возобновляется. Через некоторое время происходит изменение на: единицу старших разрядов счетчика 5 и проверяется следующий по порядку уровень прерывания.

Проверка уровней прерывания для формирования сигнала прерывания заключается в сравнении значения сигна- ла запроса за три предыдущих периода проверкиJ хранящихся в первом блоке памяти 14 с текущим запроса и определением факта изменения значения запроса. Поясним работу первого блока памяти 14 в составе устройства.

Первый блок памяти 14 - это оперативное запоминающее устройство (ОЗУ).

В первом блоке 14 памяти каждому уровню прерывания отведена зона из четырех одноразрядных слов, идущих подряд одно за другим.- Зона первого блока 14 памяти определяется старшими разрядами первого двоичного счётчика 5, ее номер совпадает с номером уровня прерывания.

В течение периода поиска по всем уровням проверка значения запроса выполняется в стандартном такте проверки. В этот такт проверки выполняется одна операция записи информации в первый блок 14 памяти и три операции считывания информации из перво30

35

40

45

50

55

.3 1

го блока 14 памяти. Обращение к четырем словам зоны первого блока 14 памяти выполняется с помощью двух средних разрядов первого двоичного счетчика 5. Это обращение к словам- блока 14 памяти выполняется по очере ди, т.е. к первому слову зоны, далее к второму, третьему и затем четвертому. Для какого слова выполняется операция записи информации, определяет управляющая информация, поступающая из первого мультиплексора 18 на управляющий первого блока 14 памяти.

Для данного периода поиска по всем уровням прерывания номер слова в зоне первого блока 14 памяти, в ко торое выполняется запись информации, один и тот же. В конце периода поиска этот номер изменяется циклически т.е. в данный период поиска запись выполняется в слово зон первого блока 4 памяти номер четыре, в следующий период запись информации выполняется в слово зон номер один, а по прошествии еще двух периодов поиска - снова в слово номер четыре и т.д.

Номер слова зон первого блока памяти 14, в которое выполняется запись информации, формируется совместной работой регистра 16 сдвига,элемента И-НЕ 17 и мультиплексора 18. На тактовый вход регистра сдвига 16 поступает самый старший разряд, первого двоичного счетчика 5, по заднему фронту этого разряда выполняется операция записи информации в регистр 16 сдвига. Все выходы регистра 16 сдвига соединяются между собой через элемент И-НЕ 17, выход которб- го подключен к управляющему.входу (данных) регистра 16 сдвига. Поэтому до тех пор, пока на одном их выходов регистра 16 сдвига имеется О, в не го записываются сигналы 1. После трех периодов поиска по всем уровням прерывания элемент Й-НЕ-17 переключа ется, после чего в течение периода поиска на управляющем входе первого регистра 16 сдвига присутствует О, в результате чего О находится только на одном выходе регистра сдвига 16 или на выходе элемента И-НЕ 17 .- Выходу элемента И-НЕ 17 поставлены в соответствие все первые слова зон первого блока 14 памяти. Трем выходам регистра 16 сдвига поставлены в

412424

соответствие все вторые, третьи и четвертые слова зон первого блока памяти 14 соответственно. Опрос зна- чений выходов регистра 16 сдвига и 5 выхода элемента fi-HE 17 выполняет

мультиплексор 18, на управляющий вход которого поступают два средних разряда первого двоичного счетчика

5, на выходе мультиплексора 18 появля- to ется признак, указывающий, выполнять nepBOMj - блоку 14 памяти операцию записи или операц11ю считывания данного слова.

Адрес обращения к слову в первом 15 блоке 14 памяти образуется объединением старших и средних разрядов

счетчика 5, присутствующих на его первом и втором выходах.

Такт проверки изменения значения 20 запроса в данном уровне прерывания одинаков для всех зон первого блока 14 памяти и состоит из подачи кода уровня прерывания на дешифратор 6 и второй адресный вход первого блока 25 памяти 14, операции записи текущего значения запроса с вькода элемента ИЛИ 10 через мультиплексор 28 в первый триггер 13, четырех операций об- . ращения к блоку памяти 14, трех опе- 30 раций записи значения запроса за три предыдущих периода проверки регистр сдвига 15 и операции записи сигнала прерывания с выхода элемента И 25 в триггер 24. Способ записи информации в триггер 13 формируется элементом И i 2 по совпадению двух инверсных значений средних разрядов первого двоичного счетчика 5 и строба, присутствующего на первом выходе генератора 11 и щyльcoв. С выхода -элемента И 12 строб поступает на тактовый вход триггера 13. При этом триггер 13 фиксирует значение запроса, поступившее на его информационный вход, на весь такт поиска. Это обеспечивает возможность асинхронной работы источника запросов прерываний по отношению к устройству. Значение запроса с выхода триггера 13 поступает на информационный вход блока памяти 14. Эта информация записьшается в блок 14 памяти тогда, когда с выхода мультиплексора 18 поступает приз- - нак записи.

55 После записи значения запроса в триггер 13 выполняются четыре операции обращения к первому блоку 14 памяти, каждая из которых сопровож35

40

45

дается признаком записи или считывания, поступающим из мультиплексора 18. Этот признак поступает и на управляющий вход регистра 15 сдвига, ксторьш во время операции записи в блок памяти 1А пропускает такт записи информации. Операции записи значения запроса.с выхода блока памяти 14 в регистр сдвига 15.выполняются во время трех операций считывания информации из блока 14 памяти.

Синхронизацию работы блока 14 памяти, триггера 13 и регистра 15 сдвига выполняет генератор II импуль сов.

В блоке 14 памяти .значение запро са записывается с выхода тригтера 13, что обеспечивает использование значение запроса в следующие перио- ды проверки.

После четьфех операций обращения к блоку 14 памяти в регистре 15 сдвига имеют трехразрядное слово, содержащее значение за три предьщущих периода проверки. Информация с выхода регистра 15 сдвига параллельным трехразрядным кодом поступает на дешифратор 20 и мажоритарный элемент 21..

С выхода мажоритарного элемента 21 сигнал поступает на второй вход .элемента 22 сложения по модулю два.

Элемент 22 сложения по модулю два сравнивает состояние триггера 13, равное текущему значению запроса, с сигналом с выхода мажоритарного элемента 21 и на выходе сигнал разрешения (1) в случае несовпадения сигналов на его входах и сиг нал запрета (О) в случае совпадения.

Блок 19 памяти - это ПЗУ с организацией 1 разряд X Р слов. Этот блок содержит признаки разрешения формирования прерьтания по появлению и/или по снятию запроса.

Адрес обращения к слову блока 19 памяти образуется слиянием старших разрядов первого двоичного счетчика 5 и информации на выходе триггера 13. В блоке 19 памяти в слове,соответствующем данной зоне первого блока 14 памяти и значению запроса, поступающему из триггера 13, хранится информация Разрешено (1, если разрешено формирование сигнала прерывания по снятию запроса) и Запрет (О в противном случае).

Второй дешифратор 20 является ПЗУ с организацией 1 разряд на 8 слов. Он формирует на выходе сигнал Запрет - (О) при наличии всех нулевых сигналов на его входе или при наличии всех единичных сигналов на его входе и сигнал Разрешено (1) во всех остальных случаях.

Элемент И 25 формирует значение сигнала прерывания I при появлении трех сигналов Разрешено на выходах второго блока 19 памяти, второго дешифратора 20 и элемента 22 сложения по модулю два и значение О в противном случае.

Инфор1мация с выхода элемента И 25 поступает на информационный вход триггера 24. Строб записи информации в триггер 24 поступает на его тактовый вход и формируется элементом И 23 по совпадению двух прямых значений разрядов первого двоичного счетчика 5 и строба, присутствующего на четвертом выходе генератора 11 импульсов .

Запись информации во второй регистр сдвига 15 выполняется по стробу, присутствзтощему на третьем выходе генератора И1у1пульсов 11,

Генератор 11 импульсов обеспечивает синхронную работу узлов устройства, вырабатывая на своих выходах импульсы так, что импульс на первом выходе начинается раньше, чем на втором, на втором выходе раньше, чем на третьем и на третьем выходе раньше, чем на четвертом. Генератор 11 импульсов построен па основе регистра сдвига, управляемого двумя младшими разрядами двоичного счетчика 5.

При включении питания узлы устройства находятся в неопределенном состоянии. Поэтому на вход 39 поступает сигнал Сброс по включению питани51,

В основном регжиме работа триггера 33 блокируется, поскольку сигнал на входе 38 устройства равен 1.

При работе в режиме самоконтроля устройство функционирует следующим образом.

На разрешающий вход второго блока памяти, управляющий вход мульти- sineKCopa 28 третий вход элемента И 31, вход элемента НЕ 30 с входа 38

устройства подается О, который задает режим самоконтроля.

При этом блокируется работа триггера 24. Триггер 24 находится в сбро шейном (О), состоянии, и в объект управления сигнал прерывания не поступает.

При подаче на разрешающий вход второго блока памяти сигнала самокон роля его работа блокируется и на его входе поддерживается единичное сос- тояние на протяжении всей работы в режиме самоконтроля.

В этом режиме мультиплексор 28 запрещает прохождение сигнала с выхода элемента- ИЛИ 10 на вход триггера 13 и разрешает передачу эталонного сигнала с первого выхода второго счетчика 26 на вход триггера 13.

Теперь устройство формирует сигнал прерывания на выходе элемента И 25 в соответствии с эталонным, периодически меняющим полярность сигналом на первом (старшем) выходе двоич кого счетчика 26, который является рсмитатором входных сигналов запросов прерывания.

На счетный вход счетчика 26 пода- ется самый старший разряд первого вькода счетчика 5. Счетчик 26 имеет три выходных разряда с кратным изменением частоты: первый (старший),второй и третий (младший).Частота изменения первого разряда в два раза ниже, чем второго, частота изменения второго разряда в два раза ниже, чем третьего.

Под управлением счетчика 26 эле- мент И 29 и элемент НЕ 27 формируют на выходе элемента И 29 прогнозируемый сигнал прерывания. Сигнал на выходе элементов К 25 и 29 сравнивается элементом 34 сложения по модулю два, информация с выхода которого потупает на информационный вход триггера 33.

Стробирование триггеров 24 и 33 вдется одним и тем же сигналом, кото- рый с выхода элемента И 23 подается на тактовый вход триггера. 33.

В случае правильной работы устройства триггер 33 находится в нулевом состояН ии и сигнал Неисправ- ность не формируется, при отказе одного из. элементов устройства триггер 33 устанавливается в единичное

5

10

15 20

25

Q

0

5

5

состояние .формируется сигнал неисправности, который подается на выход 36.

При переходе из основного режима в режим самоконтроля и обратно работа триггеров 24 и.33 блокируется подачей на входы 39 и 40 устройства сигналов Сброс.

Формула изобретения

Устройство для формирования сигнала прерывания, содержащее первый элемент НЕ, четыре элемента И, первый счетчик, два дешифратора, группу элементов И, элемент ИЛИ, генератор импульсов, два триггера, два блока памяти, два регистра сдвига, элемент И-НЕ, первый мультиплексор, мажоритарный элемент и первый элемент сложения по модулю два, причем первый вход первого элемента И соединен с тактовым входом устройства,второй вход первого элемента И соединен с выходом первого элемента НЕ, выход .первого элемента И соединен со счетным входом первого счетчика, первый разрядный выход первого счетчика соединен с входом первого дешифратора, адресным выходом устройства, первьми входами адреса первого и второго блоков памяти и тактовым-, входом первого регистра сдвига, каждый выход пер - вого д.ешифратора соединен с первым входом одноименного элемента И группы, вторые входы элементов И группы соединены с одноименными запросными входами устройства, выходы элементов И группы соединены с входами элемента ИЛИ, второй разрядный выход первого счетчика соединен с первыми входами второго и третьего элементов И, вторым входом адреса первого блока памяти и первым управляющим входом первого мультиплексора, третий разрядный выход первого счетчика соединен с входом запуска генератора импульсов, первый выход генератора импульсов соединен с вторым входом второго элемента И, второй выход генератора импульсов соединен с тактовым входом первого блока памяти, третий выход генератора импульсов соединен с тактовым входом второго регистра сдвига, четвертый выход генератора импульсов соединен с вторым входом третьего элемента И,

выход второго элемента И соединен с тактовым входом первого тригг.ера, выход первого триггера соединен с информационным входом первого блока памяти, вторым входом адреса второго блока памяти и первым входом первого элемента сложения по модулю два, выход первого блока памяти соединен с информационным входом второго ре- гистра сдвига, выходы первого регистра сдвига соединены с входами .элемента И-НЕ и группой входов первого мультиплексора, выход элемента И-НЕ соединен с входом управления сдвигом первого регистра сдвига и вторым управляющим входом первого мультиплексора,выход первого мультиплексора соединен с входом управления записью первого блока памяти и входом управ- ления сдвигом второго регистра сдвига, выходы второго регистра сдвига соединены с входом второго дешифратора и входом мажоритарного элемента, выход мажоритарного элемента сое динен с вторым входом элемента сложения по модулю два, выход второго блока памяти соединен с первым вхо- до четвертого элемента И, выход второго дешифратора соединен с вторьм входом четвертого элемента И, выход первого элемента сложения по модулю два соединен с третьим входом четвертого элемента И, выход четвертого элемента И соединен с информационным входом второго триггера, выход третьего элемента И соединен с тактовым входом второго триггера, выход второго триггера соединен с входом первого элемента НЕ и является выходом прерывания устройства, о т - личающе.еся тем, что, с целью повышения быстродействия устройства, в него введены второй счетчик, второй элемент НЕ, второй мультиплексор, пятый, шестой и седь.мой элементы И, второй элемент сложения по модулю два, третий элемент НЕ и .третий триггер, причем первый раз

5 0 5 о 0

5

рядный выход первого счетчика соединен со счетным входом второго счетчика, разрешающий вход второго блока памяти, управляющий вход второго мультиплексора, первый вход пятого элемента И и вход второго элемента НЕ соединены с входом задания режима устройства, первый разрядный выход второго счетчика соединен с первым информационным входом второго мультиплексора, выход элемента HJlIi соединен с вторым информационным входом второго мультиплексора, выход второго мультиплексора соединен с инфор- мационньш входом первого триггера, второй разрядный выход второго счетчика соединен с входом третьего эле- мента НЕ, третий разрядный выход второго счетчика соединен с первым входом; шестого элемента И, вьгход третьего элемента НЕ соединен с вторым входом шестого элемента И, выход шестого элемента И соединен с первым входом второго элемента сложения по модулю два, вькод четвертого элемента И соединен с вторым входом второго элемента сложения по модулзо -два/ выход второго элемента сложения по модулю два соединен с информационным- входом третьего триггера, второй вход пятого элемента И соединен с ответным входом устройства, первый вход седьмого элемента И соединен с входом блокировки устройства, третий вход пятого элемента И и второй вход седьмого элемента И соединены с входом начального сброса устройства, выход второго элемента НЕ соединен с третьим входом седьмого элемента И, вьо:од пятого элемента И соединен с входом сброса второго триггера, выход седьмого элемента И соединен с входом сброса третьего триггера, выход третьего элемента И соединен с тактовым входом третьего триггера, выход третьего триггера является сигнальным выходом устройства.

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования сигнала прерывания | 1985 |

|

SU1290327A1 |

| Устройство формирования сигнала прерывания | 1983 |

|

SU1112365A1 |

| Устройство формирования сигнала прерывания и обмена | 1985 |

|

SU1269133A1 |

| Устройство для формирования сигнала прерывания | 1987 |

|

SU1432522A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для приема информации | 1988 |

|

SU1552216A1 |

| Устройство для приема дискретной информации | 1989 |

|

SU1619326A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| БОРТОВОЙ СПЕЦВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2522852C1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано в системах прерывания вычислительных систем, в том числе в управляющих вычислительных машинах и комплексах. Целью изобретения является повышение качества за счет введения средств самоконтроля, охватывающих контролем основные узлы устройства. В устройство дополнительно введены второй двоичный счетчик, второй инвертор, второй мультиплексор, пятый, П1естой и седьмой элементы И, второй элемент сложения по модулю два, третий инвертор, третий триггер, соединенные определенным образом. 1 ил. ю li irc 4 to

Редактор Л.Пчелинская

СоставительМ.Кудряшов Техред О.ГорТВаи

Заказ 3490/44Тираж 671 ,Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор А.Тяско

| Каган Б.М | |||

| Электронные вычислительные машины и системы | |||

| - М.: Энергия, с.298, рис.8-16 | |||

| Устройство формирования сигнала прерывания | 1983 |

|

SU1112365A1 |

Авторы

Даты

1986-06-30—Публикация

1984-12-10—Подача