дов маски соединен с вторыми входами третьего блока элементов И, выходы которого подключены к входам дешифратора состояния, выходы которог соединены с входами первого элемент ИЛИ, блока элементов задержки, втор ми входами блоков элементов И первой группы, первым входом блока обнаружения окончания- микропрограмм, первым управляющим входом блока проверки логических условий и первым входом четвертого блока элементов И второй вход которого соединен .с нулевым выходом триггера режима, выходы блока элементов .задержки подключены к первым входам блоков элементов И второй группы, выходы которых соединены с вторыми входами е5локов элементов ИЛИ группы, выход первого элемента И соединен с вторым управляющим входом блока проверки логических условий, третий управляющий вход которого соединен с вторым управляющим входом устройства, первый адресный, второй адресный выходы и выход лог-ических условий блока памяти микропрограмм подключены соответственно к паровому адресному, второму адресному и четвертому управляющему входам блока проверки логи.ческих условий, адресный выход которого соединен с вторыми входами блоков элеме 5тов И второй группы, выходы четвертого блока элементов И соединены с единичными входами соответствующих разрядов регистра теку-, щей микропрограммы, выход которого соединен с вторым входом в.торого блока элементов И и входами второго элемента .ИЛИ, выходы второго блока элементов И соединены с нулевыми входами соответствующих разрядов регистра текущей микропрограммы и входами третьего элемента ИЛИ, выход которого подключен к -нулевому входу триггера режима, единичный вход которого Соединен с выходом второго элемента ИЛИ, выход тупика блока проверки логических условий соединен с входами второго элемента И, выход которого соединен с единичным входом триггера фиксации тупика и третьим . входом первого элемента И. ;.- .

2. Устройство по п. I, о т.л.и-. .4 а ю щ е ее я тем,- что.блок проверки, логических условий содержит дешифратор, первую и вторую группы блоков элементов И, сумматор по модулю два, первый, второй и третий блоки триггеров, первый.и второй блоки элементов И, причем первый выход дешифратора соединен с первьлии входами блоков элементов И первой группы, второй выход дешифратора соединен с первыми входами блоков элементов И второй группы, выходы которых соединены р первым входом сумматора по модулю два, второй вход которого

подключен к второму адресному входу блока проверки логических условий, а выход - к адресному выходу и первому адресному входу блока проверки логических условий, четвертый управляющий вход блока проверки логических условий соединен с входом дешифратора, первый управляющий вход блока проверки логических условий соединен с вторыми входами блоков элементов И второй группы, третий управляющий вход блока проверки логических условий подключен к нулевым входам первого блока триггеров и вторым входам блоков элементов И первой группы, выходы которых соединены с единичными входами блока триггеров, единичные выходы которого соедин1ены с выходом тупика блока проверки логических условий и единичными входами второго блока триггеров нулевые выходы первого блока триггеров соединены с единичными входами хретЫего блока триггеров, единичные выходы второго блока триггеров подключены к первым входам первого блока элементов И, выходы которого соединеньа с выходом начала ожидания блока проверки логических условий и . нулевыми входами второго блока триггеров; , единичные выходы третьего блока триггеров соединены с первыми входами второго блока элементов И, выход которого соединен с выходом .окончания ожидания блока проверки логических условий и нулевыми входами третьего блока триггеров, второй управляющий вход блока проверки логических условий соединен с вторыми входами.первого и второго блоков элементов- И. - .

3. Устройство по.п. 1, о т л ич а.ющ .е .ё с- я .тем, что блок обнаружения окончания микропрограмм со.держит элемент И и блок элементов И, причем первый вход блока обнаружения окойчания микропрограмм соединен с входами элемента И, выход которого соединен с .первым входом блока элементов .И, второй вход блока обнаруженйя окончания микропрограмм подключен., к второму входу блока элементов И, выход которого соединен с выходом блока обнаружения окончания микропрограмм. 4. Устройство по п. 1, о т л ич а ю щ а е с я тем, что коммутатор кодов операций содержит дешифратор и группу блоков элементов И, причем вход коммутатора кодов операций соединен с входом дешифратора и первыми входами блоков элементов И группы, вторые входы которых подключены к выходам дешифрато эа и управляющему выходу коммутатора кодов операций, выходы блоков элементов И группы соединены с адресным выходом коммутатора кодов операций. Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных ЭВМ с параллельным выполнением микропрог рамм. Известно устройство программного управления для системы дгшьней телефонной связи, которое содержит входные регистры/ дешифраторы, блок ти микропрограмм, элементы И, элемент ИЛИ, генератор импульсов tl. Недостатком этого устройства является низкая производительность, обусловленная значительными потерями времени на анализ состояния устройства с целью выбора микропрограмм на выполнение. Наиболее близким к изобретению по технической сущности и достигаемо му положительному эффекту решением является мультимикропрограммное устройство управления, содержащее коммутатор кода операции, первый блок элементов И, группу блоков элементов ИЛИ, группу блоков элементов И, первый блок элементов ИЛИ, генератор тактовых импульсов,, элемент ИЛИ, эле мент И, триггер пуска и блок памяти микропрограмм, выход микроопераций которого соединен с управляющим выходом устройства, первый управляющий вход устройства соединен через первый блок элементов И, управляемый триггером пуска, с входом коммутатора кода операций, адресный выход которого подключен к первому входу группы блоков элементов ИЛИ, выход группы блоков элементов ИЛИ соединен с входом группы регистров адресов, выход которой подключен к первому входу группы блоков элементов И, выход группы блоков элементов И соединен с входом блока элементов ИЛИ, выход которого соединен с адресным входом блока памяти, управляющий вход которого соединен с выходом пер вого элемента И, второй вход которого подключен к выходу генератора импульсов, вход пуска устройства соеди нен с единичным входом триггера пуска 2. Недостатками известного устройства являются низкая производительност и узкая область применения. Узость области применения устройства обусловлена заранее предопределенным делителями частоты порядком включения микропрограмм, а также закреплением за микропрограммами определенных приоритетов. В устройстве невозможно реализовать в общем случае планирование с относительными приоритетами. Это при водит к тому, что среднее время ожидания заявок на выполнение микропрог рамм не зависит от приоритета. Причиной низкой производительности является простой устройства в режимах ожидания текущей микропрограммы. Цель изобретения - расширение области применения и повышение производительности устройства. Поставленная цель достигается тем, что мультимикропрогргилмнре устройство управления, содержащее ком- . Мутатор кода операции, первый блок элементов И, группу блоков элементов ИЛИ, группу блоков элементов И, первый блок элементов ИЛИ, генератор тактовых импульсов, элемент ИЛИ,элемент И, триггер пуска и блок памяти микропрограмм, выход микроопераций которого соединен с управляющим выходом устройства, первый управляющий вход устройства соединен с первым входом первого блока элементов И, второй вход которого соединен с единичным выходом триггера пуска, а выход - с входом коммутатора кода операций , адресный выход которого подключен к первым входам блоков элементов ИЛИ группы, выходы которых соединены с входами регистров адресов группы, выходы которых подключены к первым входам блоков элементов И группы, выходы которых соединены с входами блока элементов.ИЛИ, выход которого соединен с адресным входом блока памяти микропрограмм, вход считывания которого соединен с выходом первого элемента И, выход первого элемента ИЛИ .соединен с первым входом первого элемента И, второй вход которого подключен к выходу генератора тактовых импульсов, вход пуска-устройства соединен с единичным входом триггера.пуска, дополнительно содержит второй и третий блоки элементов ИЛИ, первый, второй, третий и четвертый блоки элементов И, блок элементов задержки, первый и второй блоки одновибраторов, вторую группу блоков элементов И, второй и третий элементы ИЛИ, второй элемент И,.регистр состояния микропрограмм, дешифратор состояния, регистр текущей микропрограммы, формирователь кодов маски, триггер режима, блок обнаружения окончания микропрограмм, блок проверки логических условий и триггер фиксации тупика, единичный выход кото-, рого соединен с вторым управляющим выходом устройства и нулевым вkoдoм . (Триггера пуска, управляющий выход коммутатора кода операций соединенс первым входом второго блока элементов ИЛИ, второй вход которого через первый блок одновибраторов соединен с выходом окончания ожидания блока проверки логических условий, выход начала ожидания блока проверки логических условий соединен через второй блок одновибраторов с первым входом третьего блока элементов ИЛИ,второй вход которого подключен к выходу блока обнаружения окончания микропрограмм и первому входу второ го блока элементов И, выходы второго блока элементов ИЛИ соединены с единичными входами соответствующих разрядов регистра состояния микропрограмм, выходы третьего блока эле ментов ИЛИ соединены с нулевыми вхо дами соответствующих разрядов регистра состояния микропрограмм, выходы которого соединены с первыми входами третьего блока элементов И, выход формирователя кодов маски сое динен с вторыми входами третьего бп ка элементов И, выходы которого под ключены к входам дешифратора соетояния, выходы которого соединены с входами первого элемента ИЛИ, бло ка элементов задержки, вторыми входами блоков элементов И первой груп пы, первым входом блока обнаружения окончания микропрограммы, первым уп равляющим входом блока проверки логических условий и первым входом четвертого блока элементов И, второ вход которого соединен с нулевым выходом триггера режима, выходы бло ка элементов задержки подключены к первым входам блоков элементов И второй группы, выходы -которых соединены с вторыми входами блоков эле ментов ИЛИ группы, выход первого элемента И соединен с вторым управляющим входом блока проверки логических условий, третий управляющий вход которого соединен с вторым управляющим входом устройства, первый адресный, второй адресный выходы и выход логических условий блока памя ти микропрограмм подключены соответственно к первому адресному,второму адресному и четвертому управляющему входам блока проверки логических условий, адресный выход кото рого соединен с вторыми входами бло ков элементовИ второй группы, выходы четвертого блока элементов И соединены с единичными входами соответствующих разрядов регистра текущей микропрограммы, выход которого соединен с вторым входом второго блока элементов И и входами второго элемента ИЛИ, выходы второго блока элементов И соединены с нулевыми входами соответствующих разрядов регистра текущей микропрограммы и входами третьего элемента ИЛИ, выход которого подключен к нулевому эходу триггера режима, единичный вход которого соединен с выходами второго элемента ИЛИ, выход тупика блока проверки логических условий соединен с входами второго элемента И, выход которого соединен с единичным входом триггера фиксации тупика и третьим входом первого элемента И того, блок проверки логичес ких условий содержит дешифратор,первую и вторую группы блоков элементов И, сумматор по модулю два, первый, второй и третий блоки триггеров первый и второй«блоки элементов И, причем первый выход дешифратора соединен с первыми входами блоков элементов И первой группы, второй выход дешифратора соединен с первыми входами блоков элементов И второй 1руппы, ёыходы которых соединены с первым входом сумматора по модулю два, второй вход которого подключен к второму адресному входу блока проверки логических условий, а выход к адресному выходу и первому адресному входу блока проверки логических условий, четвертый управляющий вход блока проверки логических условий соединен с вторыми входами блоков элементов И второй группы, третий управляющий вход блока проверки логических условий подключен к нулевым входам первого блока триггеров и вторым входам блоков элементов И первой группы, выходы которых соединены с единичными входами первого блока триггеров, единичные выходы которых соединены с выходом тупика блока проверки логических условий и единичными входами второго блока триггеров, нулевые выходы первого блока триггеров соединены с единичными входами третьего блока триггеррв, единичные выходы второго блока триггеров подключены к первым входам первого блока элементов И, выходы которого соединены с выходом начала ожидания блока проверки логических условий и нулевыми входами второго блока триггеров, единичные выходы третьего блока триггеров соединены с первьт1И входами второго блока элементов И, выход которого соединен с выходом окончания ожидания блока проверки логических условий и нулевыми входами третьего блока триггеров, второй управляющий вход блока проверки логических условий соединен р вторыми входами- первого и второго блоков элементов И. При этом блок обнаружения окончания микропрограмм содержит элемент И и блок элементов И, причем первый вход блока обнаружения окончания мик-г ропрограмм соединен с входами элемента И, выход которого соединен с первым входом блока элементов И, второй вход блока обнаружения окончания микропрограмм подключен к второму входу блока элементов И, выход которого соединен .с выходом блока обнаружения окончания микропрограмм. Кроме того,коммутатор кодов операций содержит дешифратор и группу блоков элементов И, причем вход коммутатора кодов операций соединен с входом дешифратора и первыми входами блоков элементов И группы, вторые

входы которых подключены к выходам дешифратора и управляющему выходу коммутатора кодов операций, выходы блоков элементов И группы соединены с адресным выходом коммутатора кодов операций.

Все микропрограммы в устройстве могут находиться в следующих состояниях: готовая (ожидающая) - есть заявка на выполнение данной микропрограммы и она не находится (находится) в состоянии ожидания; текущая -.с приходом заявки на выполнение микропрограммы последняя запускается и до своего окончания считает ся текущей микропрограммой, а после завершения текущей микропрограммы в соответствии с относительными приоритетами выбирается на обслуживание готовая микропрограмма с наибольшим приоритетом, которая становится текущей до своего окончания; выполняемая - в данный момент физически выполняется устройством.

.Если, текущая микропрограмма не находится в ожидании, она является одновременно и выполняемой микропрограммой, если текущая микропрограмма пере.ходит в ожидание, выполняемой становится готовая микропрограмма с ближайшим большим приоритетом. Если переходит в ожидание выполняемая микропрограмма, выполняемой станрвитря готовая микропрограмма с наибольшим приоритетом из подмножества заявок с приоритетом меньше или равным, чем у выполняемой микропрограммы, перешедшей в ожидание.

Сущность новой дисциплины обслуживания заявок на выполнение микропрограмм состоит в следующем.

Выбор выполняемой микропрограммы среди готовых осуществляется в соответствии с наибольшим приоритетом (без прерывания выполняемой микропрограммы) . ПРИ переходе в ожидание текущей микропрограммы выполняемой становится готовая микропрограмма, приоритет которой является наибольшим среди готовых заявок с приоритетом ниже. Все выполняемые микропрограммы с приоритетом ниже или равным приоритету текущей микропрограммы обслуживаются в соответствии с абсолютными приоритетами. При переходе в состояние готовности по окончании ожидания микропрограммы с высшим приоритетом выполняемая микропрограмма прерывается. Дообслуживание любой микропрограммы осуществляется с точки последнего прерывания, т.е. результаты выполнения микропрограмма в режимах ожидания микропрограмм высших приоритетов сохраняются.

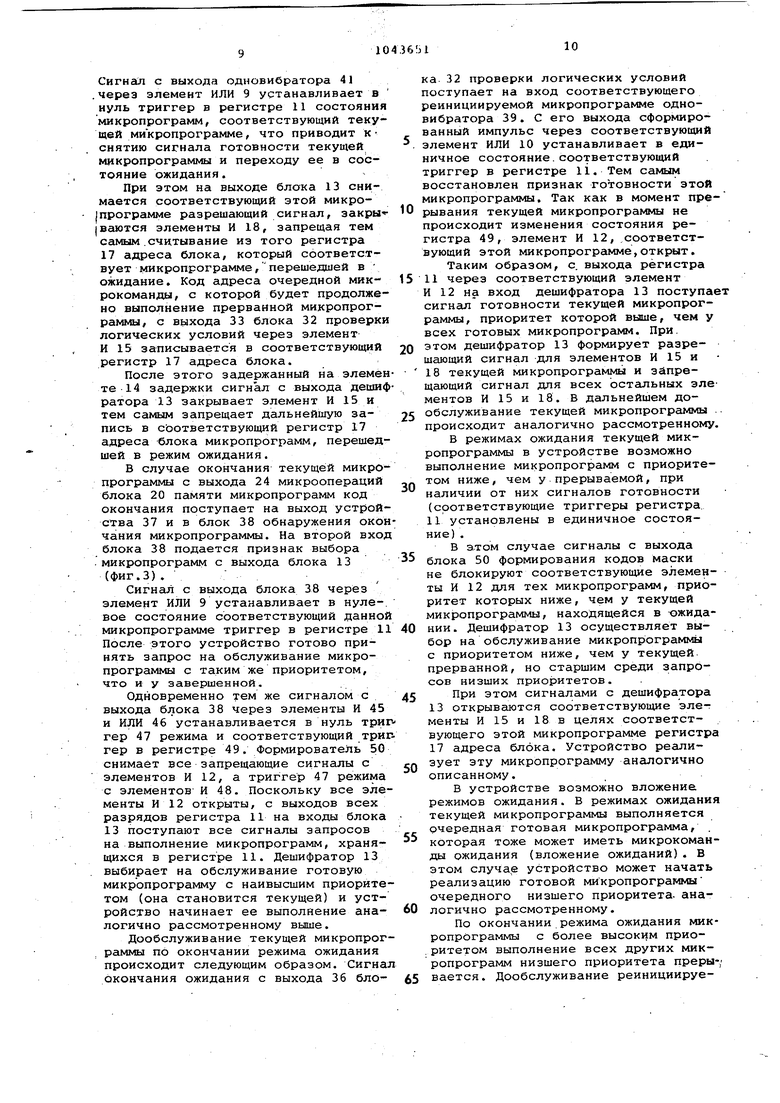

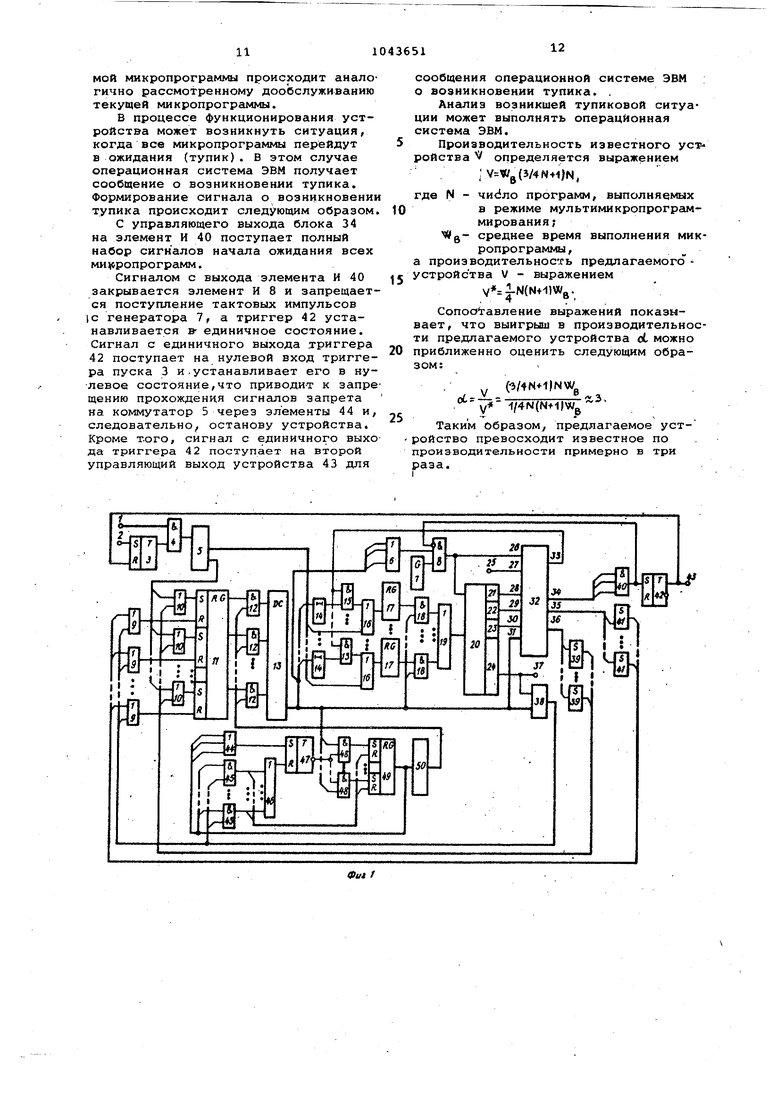

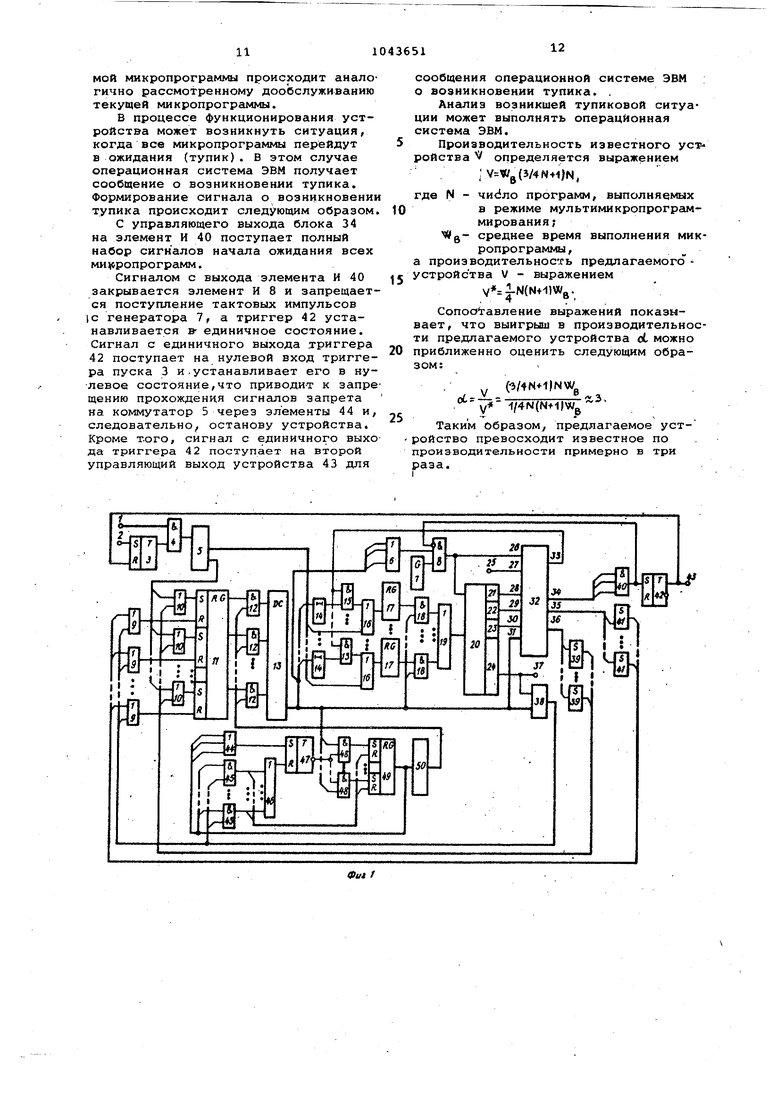

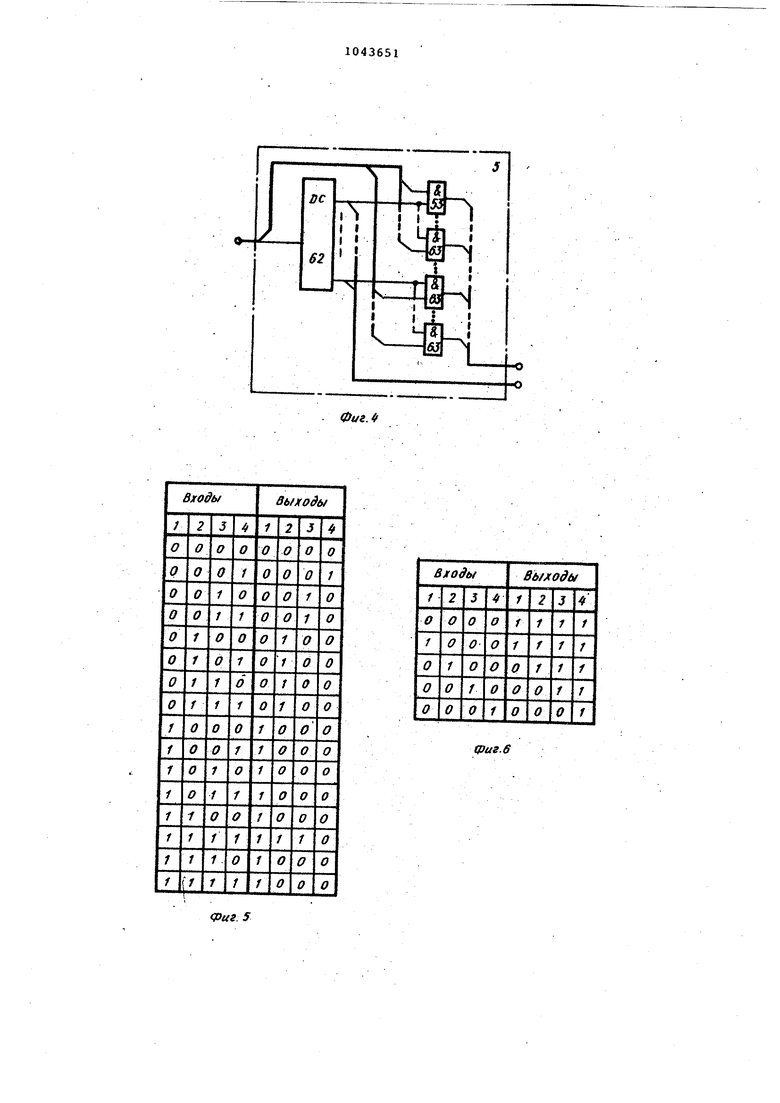

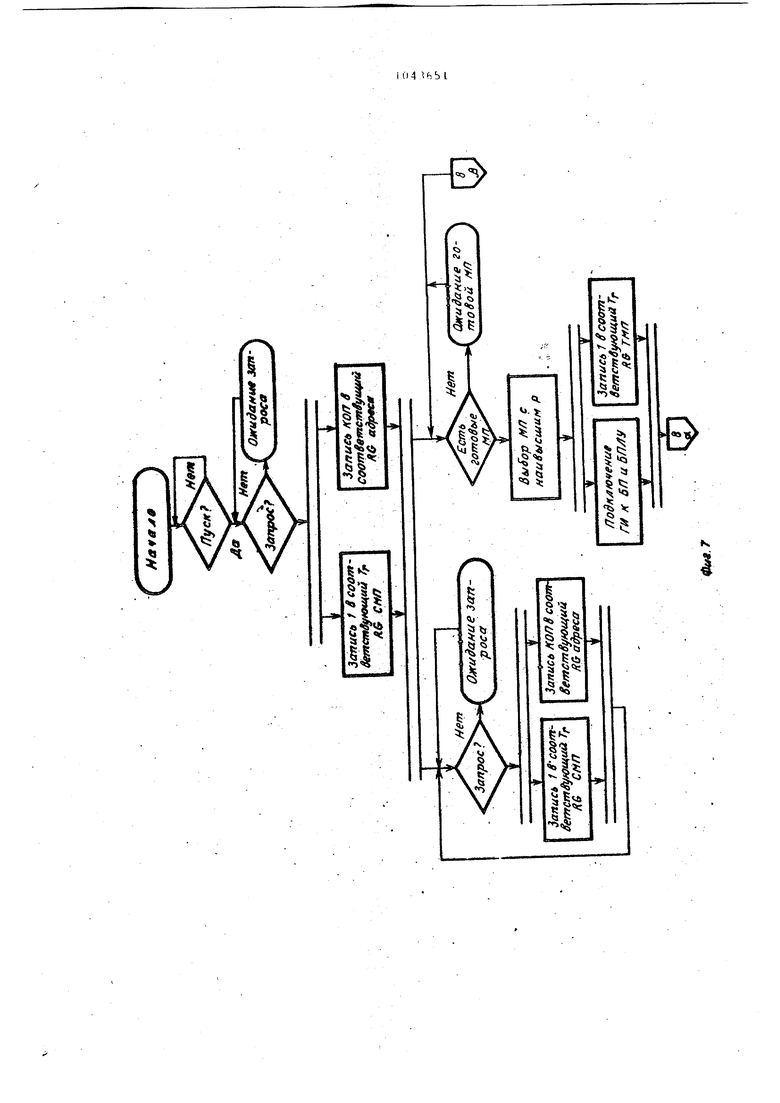

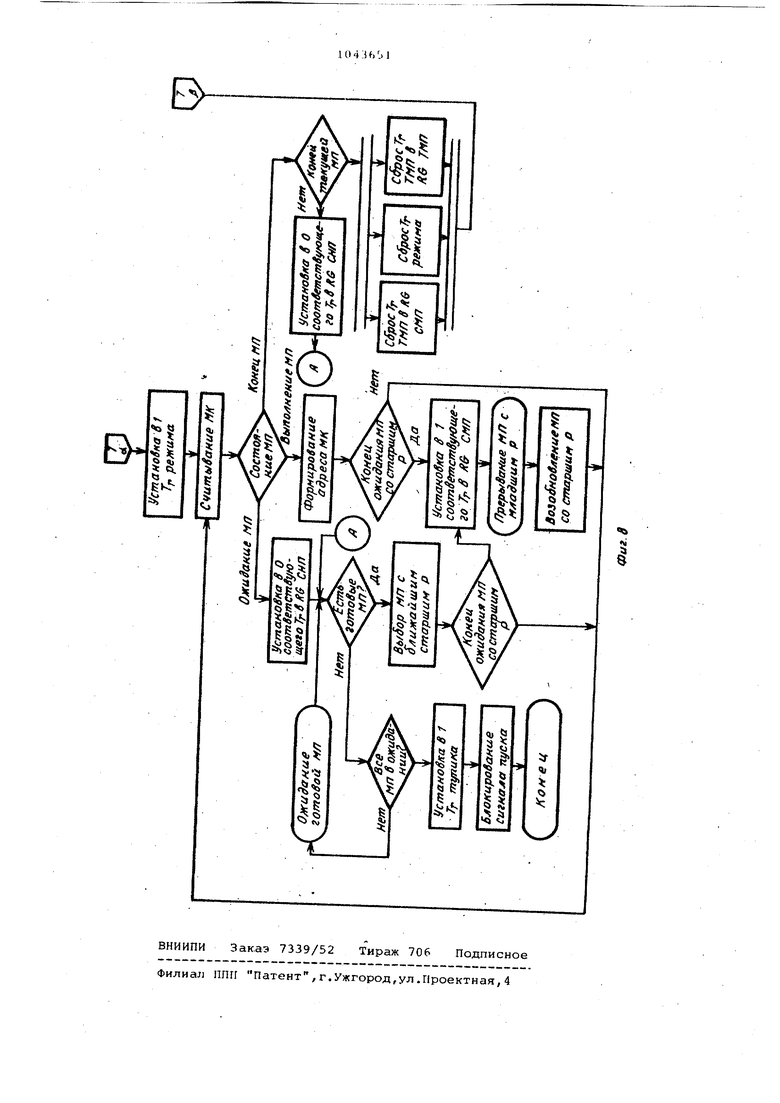

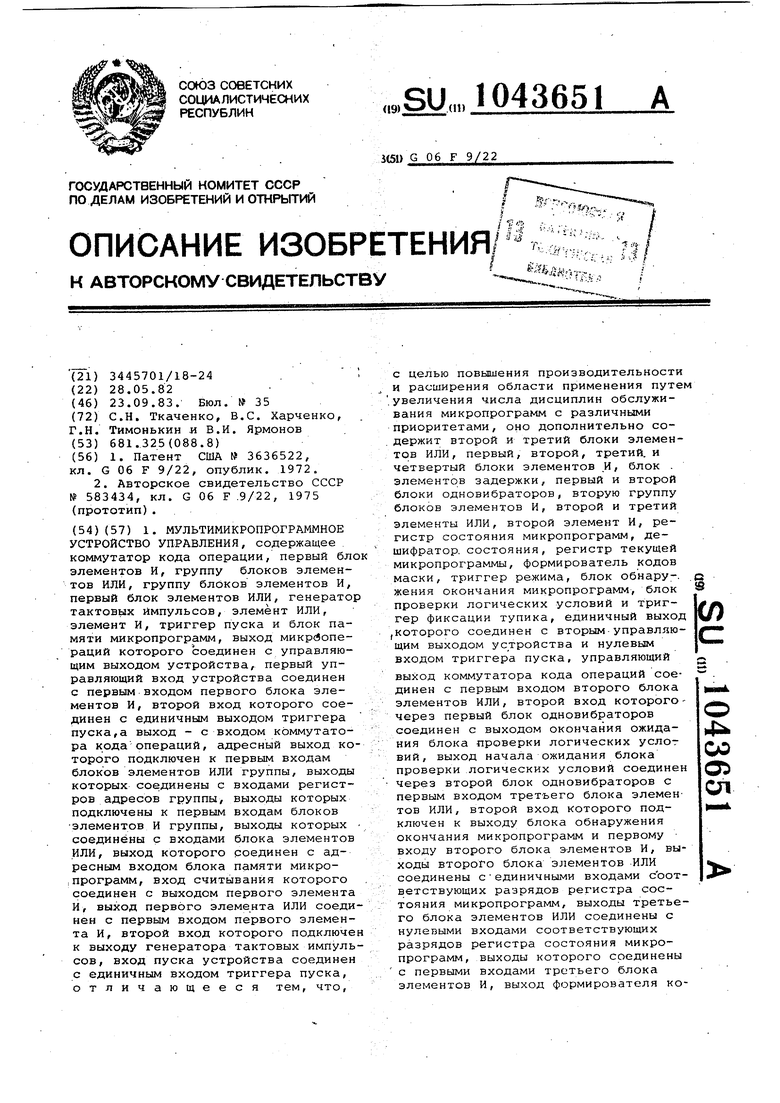

На фиг.1 представлена функциональная схема предлагаемого устройства; на фиг.2 - функциональная схема блока проверки логических условий; на

%.

1043651

фиг.З - функциональная схема блока обнаружения окончания микропрограмм на фиг.4 - схема коммутатора кодов ; операций; на фиг.5 - пример таблицы соответствия дешифратора состояний

микропрограмм; на фиг.6 - пример таблицы соответствия формирователя кодов маски; на фиг. 7 и 8 - схема ешгоритма Функционирования устройства.

0 Устройство содержит (фиг.1) пер: вый управляющий вход 1 устройства,

. вход 2 пуска устройства, триггер 3

пуска, первый блок 4 элементов И,

коммутатор 5 кодов операций, первый

5 элемент ИЛИ 6, генератор 7 тактовых, импульсов, первый элемент И 8, третий блок 9 элементов ИЛИ, второй блок 10 элементов ИЛИ, регистр 11 состояния микропрограмм, третий блок

Q 13 элементов И, дешифратор 13 состоя: ния микропрограмм, блок 14 элементов 14 задержки, вторую группу 15 блоков элементов И, группу блоков 16 элементов ИЛИ, группу регистров 17

5 адресов микропрограмм, первуй группу блоков 18 элементов И, первый блок 19 элементов ИЛИ, блок 20 памяти микропрограмм, первый 21 и второй 22 адресные выходы, выход 23 логи-. ческих условий, выход 24 микроопераций, блок 20 памяти микропрограмм.

первый 25, второй 26 и третий 27 управляющие входы, первый 28 и вто, рой 29 адресные входы, четвертый 30 и первый 31 управляющие входы

5 блока 32 проверки логических условий, который имеет адресный вы5сод 33, выход 34 тупика, выход 35 начала ожидания, выход 36 окончания ожидания блока 32, первый управляющий

0 выход 37 устройства, блок 38 обнаружения окончания микропрограмм, первый блок 39 одновибраторов, второй элемент И 40, второй блок .41 одновибраторов, триггер 42 тупика, второй управляющий выход 43 устройства, второй элемент ИЛИ 44, второй блок 45 .элементов И, третий элемент ИЛИ 46 триггер режима, четвертый блок 48 элементовИ, регистр 49 текущей

л микропрограммы и формирователь 50кодов маски..

Блок 32 (фиг.2) содержит дешифратор 51, первую группу 52-блоков элементов И, блок 53 сумматоров по модулю два, вторую группу 54 блоков элементов И, первый 55, второй 56 и третий 57 блоки триггеров, первый 58 и второй 59 блоки элементов И,

Блок 38 (фиг.З) содержит элементИ 60 и блок 61 эЛгментов И.

0 Коммутатор 5 кодов операций содержит дешифратор 62 и группу 63 блоков элементов И.

На схеме алгоритма функционирования (фиг.7 и 8) устройства приняты

5 следующие условные обозначения и

сокращения: RG - регистр; Tr - триггер; КОП - код операции; МП - микропрограмма; МК - микрокоманда; RG 1СМП - регистр состояния микропрограмм; RG ТМП - регистр текущей микропрограммы; Р - приоритет; ГИ - генератор импульсов; БП - блок памяти микропрограмм и БПЛУ - блок проверки логических условий.

Устройство работает следующим образом.

В исходном состоянии все элементы памяти находятся в нулевом состоянии.

На вход 2 устройства поступает сигнал пуска, который -открывает эле-, менты И 4 и разрешает прохождение сигнала запроса на коммутатор 5 кодов операций (фиг.4). Сигнал запроса поступает на вход 1 устройства и определяет код операции и приоритет микропрограмм. Поскольку поток поступления запросов на выполнение микропрограмм ординарный,- запросы на входы устройства приходят поочередно.

С адресного выхода коммутатора 5 через элементы ИЛИ 16 код операции записывается в регистр 17 адреса блока, соответствующий приоритету микропрограммы и определяет начальный адрес этой микропрограммы. Одновременно сигналом с управляющего выхода коммутатора 5 через элементы ИЛИ 10 в единичное состояние устанавливается соответствующий триггер в регистре 11. Тем самым определяется наличие запроса на выполнение микропрограммы и ее приоритет. При этом наивысшему приоритету микропрограммы соответствует установка в единичное состояние триггера с наименьшим номером в регистре 11.

С выхода регистра 11 через открытые элементы И 12 сигналы готовности микропрограмм поступают на входы дешифратора 13, который выбирает для обслуживания микропрограмму с наи-высшим приоритетом.

Далее устройство параллельно обрабатывает поступающие запросы и выбранную на обслуживание дешифратором 13 микропрограмму. При этом по сигналам запроса может производиться заполнение регистра 11 и запись кодов операций, соответствующих микропрограмм в регистры 17, как было описано. ,

Очередной запрос на выполнение .--шкропрограммы данного приоритета может поступить только после завершения выполнения предыдущей микропрограммы этого же приоритета.

Для обеспечения дисциплины обслуживания микропрограмм по относительным приоритетам сигнал с выхода дешифратора 13 поступает на вход соответствующего разряда регистра 49 текущей микропрограммы через открытые

элементы И 48. При этом триггер в

регистре 49, соответствующий запускаемой на обслуживание микропрограмме, устанавливается в единичное состояние. Сигналы с выхода регистра 5 49 поступают на вход блока 50 формирования кодов маски.

Формирователь 50 Маскирует сигналами со своих выходов на элементах И 12 прохождение сигналов запросов 10 на выполнение микропрограмм, приоритет которых выше, чем у текущей микропрограммы после получения ею управления.

Тем же сигналом с выхода регистра 15 49 через элемент ИЛИ 44 устанавливается в единичное состояние триггер 47 режима, сигнал с нулевого выхода которого закрывает элементы И 48. Таким образом, блокируется изменение 20 состояния регистра 49 и, следовательно, кода маски до окончания выполнения текущей микропрограммы. Это позволяет обеспечить абсолютный приоритет дообслуживания текущей микропрограммы.

Одновременно соответствующим сигналом с выхода дешифратора 13 открываются элементы И 18, а через элементы 14 задержки - элементы И 15 ,-. в цепи соответствующей выбранной микропрограмме, этим же сигналом через .элемент ИЛИ 6 открывается элемент И 8 и разрешается прохождение тактовых импульсов с выхода генератора 7 на вход считывания блока 20 5 памяти микропрограмм и на вход 26 блока 32 проверки логических условий (фиг.2).

Код адреса микрокоманды текущей микропрограммы из соответствующего

0 регистра 17 адреса блока, через соответствующие открытые элементы И 18 и ИЛИ 19 считывается в блок 20 памяти микропрограмм. С первого 21, второго 22 и третьего 23 выходов блока

5 20 памяти микропрограмм в блок прове.рки логических условий поступают коды неизменяемой части адреса, модифицируемой сигналами логических условий части адреса микрокоманды

п и коды логических условий соответственно. С адресного выхода 33 блока 32 код адреса очередной микрокоманды текущей микропрограммы через открытые элементы И 15 и ИЛИ 16 записывается в соответствующий регистр

17 адреса блока. Выполнение текущей микропрограмму продолжается до нача- , ла режима ожидания текущей микропрограммы или до окончания выполнения текущей микропрограммы.

0 в случае обнаружения микрокоманды ожидания текущей микропрограммы сигнал с управляющего выхода 35 блока 32 проверки логических условий поступает на вход соответствующего данной микропрограмме одновибратора 41

Сигнал с выхода одновибратора 41 через элемент ИЛИ 9 устанавливает в нуль триггер в регистре 11 состояния микропрограмм, соответствующий текущей микропрограмме, что приводит кснятию сигнала готовности текущей микропрограммы и переходу ее в состояние ожидания.

При этом на выходе блока 13 снимается соответствующий этой микропрограмме разрешающий сигнал, закрываются элементы И 18, запрещая тем самым .считывание из того регистра 17 адреса блока, который соответствует микропрограмме,перешедшей в ожидание. Код адреса очередной микрокоманды, с которой будет продолжено выполнение прерванной микропрограммы, с выхода 33 блока 32 проверки логических условий через элемент И 15 записывается в соответствующий регистр 17 адреса блока.

После этого задержанный на элементе -14 задержки сигнал с выхода дешифратора 13 закрывает элемент И 15 и тем самым запрещает дальнейшую запись в соответствующий регистр 17 адреса блока микропрограмм, перешедшей в режим ожидания.

В случае окончания текущей микропрограммы с выхода 24 микроопераций блока 20 памяти микропрограмм код окончания поступает на выход устройства 37 и в блок 38 обнаружения окончания микропрограммы. На второй вход блока 38 подается признак выбора микропрограмм с выхода блока 13 (фиг.З).

Сигнал с выхода блока 38 через элемент ИЛИ 9 устанавливает в нуле-. вое состояние соответствующий данной микропрограмме триггер в регистре 11 После этого устройство готово принять запрос на обслуживание микропрограммы с таким же приоритетом, что и у завершенной.

Одновременно тем же сигналом с выхода блока 38 через элементы И 45 и ИЛИ 46 устанавливается в нуль триргер 47 режима и соответствующий триггер в регистре 49. Формирователь 50 снимает все запрещающие сигналы с элементов И 12, а триггер 47 режима с элементов И 48. Поскольку все элементы И 12 открыты, с выходов всех разрядов регистра 11 на входы блока 13 поступают все сигналы запросов на выполнение микропрограмм, хранящихся в регистре 11. Дешифратор 13 выбирает на обслуживание готовую микропрограмму с наивысшим приоритетом (она становится текущей) и устройство начинает ее выполнение аналогично рассмотренному выше.

Дообслуживание текущей микропрограммы по окончании режима ожидания происходит следующим образом. Сигнал окончания ожидания с выхода 36 блока 32 проверки логических условий поступает на вход соответствующего реинициируемой микропрограмме одновибратора 39. С его выхода сформированный импульс через соответствующий элемент ИЛИ 10 устанавливает в единичное состояние.соответствующий триггер в регистре li. Тем самым восстановлен признак готовности этой микропрограммы. Так как в момент пре0рывания текущей микропрограммы не происходит изменения состояния регистра 49, элемент И 12, соответствующий этой микропрограмме,открыт.

Таким образом, с. выхода регистра

5 11 через соответствующий элемент И 12 на вход дешифратора 13 поступает сигнал готовности текущей микропрограммы, приоритет которой выше, чем у всех готовых микропрограмм. При. этом дешифратор 13 формирует разре0шающий сигнал для элементов И 15 и 18 текущей микропрограммы и запрещающий сигнал для всех остсшьных элементов И 15 и 18. В дальнейшем дообслуживание текущей микропрограммы .

5 происходит аналогично рассмотренному.

В режимах ожидания текущей микропрограммы в устройстве возможно выполнение микропрограмм с приоритетом ниже, чем у прерываемой, при

0 наличии от них сигналов готовности (соответствующие триггеры регистра, 11 установлены в единичное состояние) .

В этом случае сигналы с выхода

5 блока 50 формирования кодов маски не блокируют соответствующие элементы И 12 для тех микропрограмм, приоритет которых ниже, чем у текущей микропрограммы, находящейся в хэжида0нии. Дешифратор 13 осуществляет выбор на обслуживание микропрограммы с приоритетом ниже, чем у текущей прерванной, но старшим среди запросов низших прио зитетов.

При этом сигналами с дешифратора

5 13 открывс1ются соответствующие эле-т менты И 15 и 18 в целях соответствующего этой микропрограмме регистра 17 адреса блока. Устройство реализует эту микропрограмму аналогично

0 описанному.

в устройстве возможно вложение режимов ожидания. В режимах ожидания текущей микропрограммы выполняется очередная готовая микропрограмма,

5 которая тоже может иметь микрокоманды ожидания (вложение ожиданий). В этом случае устройство может начать реализацию готовой микропрограммы очередного низшего приоритета- ана0логично рассмотренному.

По окончании режима ожидания микропрограммы с более высоким приоритетом выполнение всех других микропрограмм низшего приоритета преры-/ вается. Дообслуживание реинициируе5

мой микропрограммы происходит аналогично рассмотренному дообслуживанию текущей микропрограммы.

В процессе функционирования устройства может возникнуть ситуация, когда все микропрограммы перейдут в ожидания (тупик). В этом случае операционная система ЭВМ получает сообщение о возникновении тупика. Формирование сигнала о возникновении тупика происходит следующим образом.

С управляющего выхода блока 34 на элемент И 40 поступает полный набор сигналов начала ожидания всех ми poпpoгpaмм.

Сигналом с выхода элемента И 40 закрывается элемент И 8 и запрещается поступление тактовых импульсов 1C генератора 7, а триггер 42 устанавливается в- единичное состояние. Сигнал с единичного выхода триггера 42 поступает на нулевой вход триггера пуска 3 и.устанавливает его в нулевое состояние,что приводит к запрещению прохождения сигналов запрета на коммутатор 5 через элементы 44 и, следовательно, останову устройства. Кроме того, сигнал с единичного выхо да триггера 42 поступает на второй управляющий выход устройства 43 для

сообщения операционной системе ЭВМ о возникновении тупика. .

Анализ возникшей тупиковой ситуации может выполнять операционная система ЭВМ.

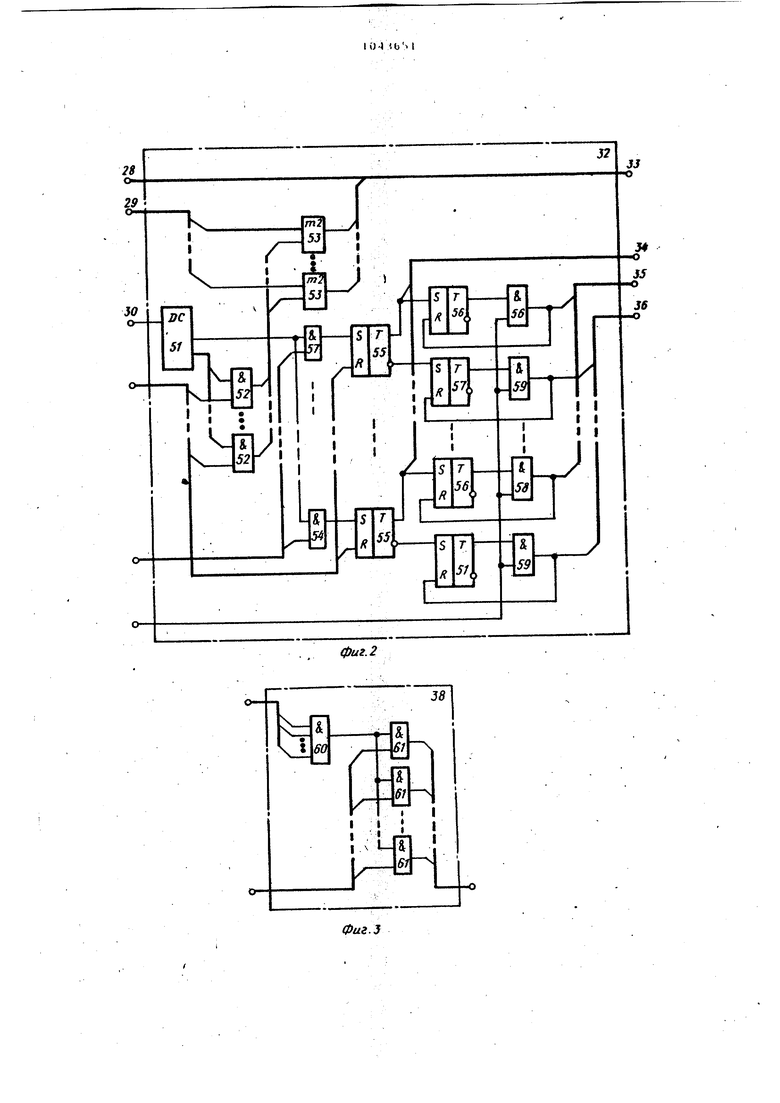

5 Производительность известного усрройства V определяется выражением

; (3/4NH)N,

где N - программ, выполняемых O в режиме мультимикропрограммирования;

NOg- среднее время выполнения микропрограммы,

а производительность предлагаемого г устройства V - выражением (N+1)We.

Сопоставление выражений показывает, что выигрыш в производительности предлагаемого устройства d, можно 0 приближенно оценить следующим образом:

У (3/4N 1|NWg -(/4N(N+-(

Таким образом, предлагаемое устройство превосходит известное по производительности примерно в три раза.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1982 |

|

SU1043653A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Мультимикропрограммное устройство управления | 1982 |

|

SU1042017A1 |

| Устройство для моделирования дискретных систем | 1985 |

|

SU1295411A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134936A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1092505A1 |

| Микропрограммное устройство управления | 1979 |

|

SU857995A1 |

| Микропрограммное устройство управления | 1980 |

|

SU955055A1 |

1. МУЛЬТИМИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее коммутатор кода операции, первый блок элементов И, группу блоков элементов ИЛИ, группу блоков элементов И, первый блок элементов ИЛИ, генератор тактовых импульсов, элемент ИЛИ, элемент И, триггер пуска и блок памяти микропрограмм, выход микр операций которого соединен с управляющим выходом устройства, первый управляющий вход устройства соединен с первым входом первого блока элементов И, второй вход которого соединен с единичным выходом триггера пуска,а выход - с входом коммутатора кода операций, адресный выход которого подключен к первым входам блоков элементов ИЛИ группы, выходы которых соединены с входами регистров адресов группы, выходы которых подключены к первым входам блоков элементов И группы, выходы которых соединены с входами блока элементов ИЛИ, выход которого соединен с адресным входом блока памяти микропрограмм, вход считывания которого соединен с выходом первого элемента И, выход первого элемента ИЛИ соединен с первым входом первого элемента И, второй вход которого подключен к выходу генератора тактовых импульсов, вход пуска устройства соединен с единичным входом триггера пуска, отличающееся тем, что. с целью повышения производительности И расширения области применения путем .увеличения числа дисциплин обслуживания микропрограмм с различными приоритетами, оно дополнительно со. держит второй и третий блоки элементов ИЛИ, первый, второй, третий, и четвертый блоки элементов И, блок . элементов задержки, первый и второй блоки одновибраторов, вторую группу блоков элементов И, второй и третий Элементы ИЛИ, второй элемент И, регистр состояния микропрограмм, дешифратор, состояния, регистр текущей микропрограммы, формирователь кодов маски, триггер режима, блок обнару-. i жения окончания микропрограмм, блок проверки логических условий и триггер фиксации тупика, единичный выход (Которого соединен с вторым-управляющим выходом устройства и нулевым входом триггера пуска, управляющий выход коммутатора кода операций соединен с первым входом второго блока элементов ИЛИ, второй вход которогочерез первый блок одновибраторов 4 соединен с выходом окончания ожидания блока проверки логических услог ОО № ВИЙ, выход начала ожидания блока проверки логических условий соединен через второй блок одновибраторов с сл первым входом третьего блока элементов ИЛИ, второй вход которого подключен к выходу блока обнаружения окончания микропрограмм и первому входу второго блока элементов И, выходы второго блока элементов ИЛИ соединены сединичными входами соответствующих разрядов регистра состояния микропрограмм, выходы третьего блока элементов ИЛИ соединены с нулевыми входами соответствующих разрядов регистра состояния микропрограмм, выходы которого соединены с первыми входами третьего блока элементов И, выход формирователя ко

38

TFih

I I

I .

62

Фиг 5

m«

Ъ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3636522, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микропрограммное устройство управления | 1975 |

|

SU583434A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-09-23—Публикация

1982-05-28—Подача