Изобретение относится к вычислительной технике.

Целью изобретения является расширение функциональных возможностей за счет расширения класса программируемых микросхем.

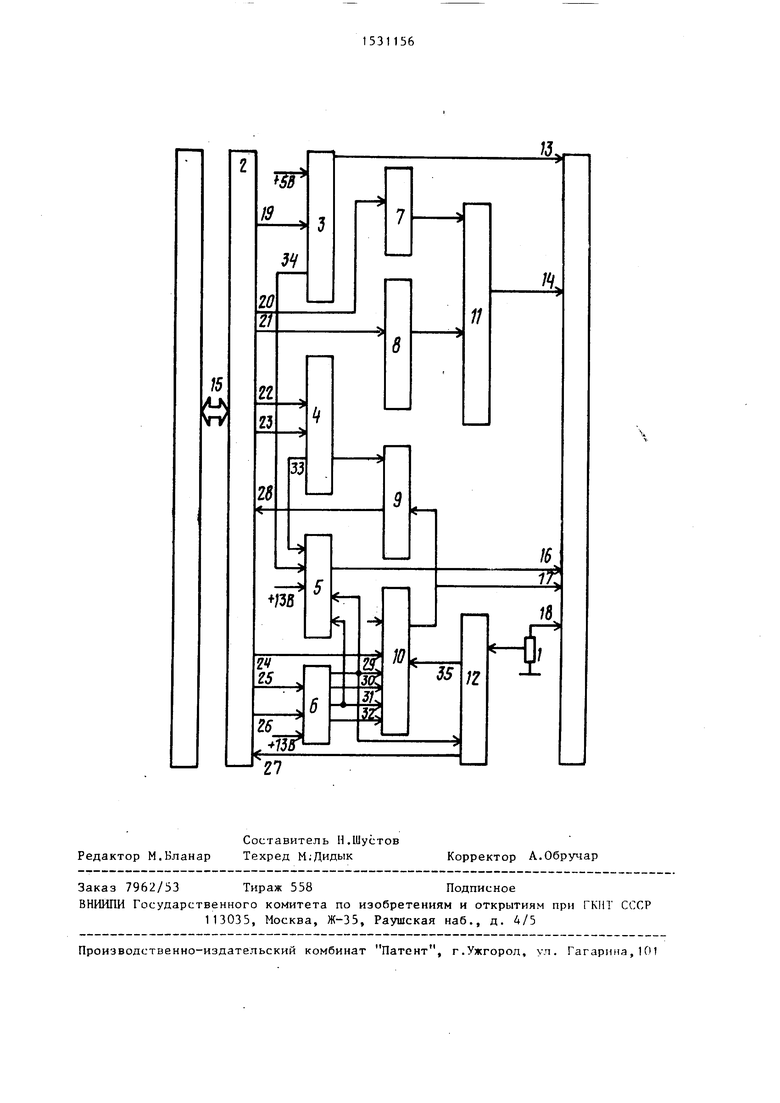

На чертеже представлена функциональная схема программатора.

Программатор содержит датчик 1 тока, блок 2 сопряжения, первый программируемый источник 3 напряжения, блок 4 управления регистром, второй 5 и первый 6 блоки управления, декодер 7 адреса, декодер 8 напряжения, регистр 9, третий 10 блок управления, второй программируемый источник 11 напряжения, формирователь 12 длительности импульса программирования, выход 13 напряжения питания программатора, выход 14 адреса, информационные выходы 15 и 16 программатора, выход 17 управления программатора, вход 18 датчика тока, первый 19, второй 20,

третий 21, четвертый 22, пятый 23, шестой 24, седьмой 25, восьмой 26 выходы блока 2 сопряжения, информационные входы 27 и 28 блока 2, первый 29, второй 30, третий 31, четвертый

32выходы блока 6 управления, третий

33выход блока 4 управления регистром, второй 34 выход источника 3, второй 35 выход формирователя 12.

Программатор логического массива с памятью (ПАЛ) работает следующим образом.

Программатор ПАЛ позволяет работать в двух режимах: Программирование и Чтение.

Режим Программирование осуществляется при уровне Лог.1 на выходе 22, режим Чтение - при уровне Лог. О на выходе.22. : Программируемый источник 3 шггания формирует на выходной шине 13 напряжение питания -t-5 В в режиме Чтение при логических уровнях

i

СП

СО

ел

05

о на ры.холс

3 1

19, при логических уровнях 1 на выходе 19, на выходе 13 формируется + 13 В в режиме Программирование.. И блока 2 сопряжения по второму выходу 20 подаются коды на декодер 7 адреса для выбора одного из восьми адресных входов. На выходе декодера 7 формируется информация на выходе 14 адреса, поступающая в источник 11 напряжения По третьему выходу 21 блока 2 П(дают ся крды в декодер 8 напряжения, с выхода которого информация поступает на второй вход задания режима источнка 11. На невыбранных входах ПАЛ ис- точника 11 уровень напряжения формируется с второго и третьего выходов блока 2. Особенностью программрования IIAJ1 является изменение входо стробирования и разрешения ПАЛ в за- висимости от номера программируемой строки.

При программировании строк с О по 31 эти входы имеют первоначальное значение, при программировании строк с 32 по 63 эти входы меняются местами. Выбор входов ПАЛ выполняет второй блок 5 управления. Информация о .выборе номера строки передается по седьмому выходу 25 блока 2. С выхода 25 информация поступает на вход блока 6, где объединяется по И с импульсом программирования и поступает на выход 30 блока 6. Инверсный сигнал о логического уровня с выхода 25 объединяется по И с импульсом программи- фования и поступает на выход 32 блока 6. Инверсный сигнал от логического уровня с выхода 25 объединяется по И с импульсом программирования и поступает на выход 32 блока 6.

Усиленный сигнал, поступивший с выхода 25, подается на вход 29, а на выходе 32 формируется его инверсный сигнал.

На выходе 13 блока 3 формируется инверсный сигнал функции логического умножения управляющих сигналов с выхода 19. При выборе режима Програм

мирование на выходе 13 формируется уровень Лог.О.

На выходе 33 блока 4 в режиме Программирование формируется уровень Лог.1.

При программировании строк с О

40 31, жогда выход 25 установлен в Лог.О, на вход блока 5 подаются с выходов 29, 31, 33, 34 соответственно логические уровни О, 1, 1, О.

При этом в блоке 5 на выходах 16 формируются уровень Лог.О и уровень напряжения В.

При программировании строк с 32 по 63 на выходе 25 устанавливается уровень Лог.1, на входах блока 5 (с выходов 29, 31, 33, 34) соответственно 1, О, 1, О. При этом на выходах 16 блока 5 И 1формац11я изменяется на противоположную, т.е. шина стробирования становится шиной разрешения и на ней ч-1 ар|аш1ивается напряжение В, а шина разрешения становится шиной стробирования и на ней установится уровень Лог.О. Выбор выходов ПАЛ на выходах 17 осуществляется с помощью блока 10 управления. Второй особенностью программирования ПАЛ является изменение значений выходов l7 в зависимости от номера программируемой строки.

При программировании с О до 31 строки выходы 17 установлены в заданном значении, при программировании строк с 32 по 63 назначения выходов изменяются .

Управление информацией по выходам 24 осуществляется программно и обеспечивает требуемые уровни на выводах ПАЛ и подачу на них импульса программирования ,

Выход 26 служит для управления формированием импульса программирования в блоке 6 управляющих импульсов. Уровнем Лог.О запрещается формирование импульса программирования, уровнем Лог. Г разрешается формирование импульса программирования в блоке 6.

Формирователь 12 длительности импульса (ФДИП) коммутирует на выходе 35 напряжение программирования. Когда перемычка пережигается, датчик 1 тока снимает токовую информацию на вход ФДИП. С выхода 27 ФДИП в микро- ЭВМ поступает информация о пережоге перемычки, а на выходе 35 отключается напряжение программирования.

Режим Чтение осуществляется формированием на выходах 22 и 23 блока 4 уровней Лог.1, которые поступают на вход блока 4 управления регистром, на выходе которого формируется импульс сброса и поступает на вход регистра 9. -После сброса выходного регистра 9 на его вход поступает сигнал Чтение.

Одновременно осуществляется тактирование ПАЛ. С выхода 33 блока 4 уровень Лог.О поступает на вход блока 5 управления, где на выходе 16 форми- руется сигнал стробирования, а также сигнал разрешения,

С регистра 9 информация поступает на вход 26 блока 2 сопряжения и с выхода 15 в его микроэвм. Формула изобретения

Программатор, содержащий блок сопряжения, первый блок управления, декодер адреса, декодер напряжения, первый и второй программируемые источНИКИ напряжения, блок управления регистром, регистр, датчик тока, формирователь длительности импульса программирования, первый выход блока сопряжения соединен с входом задания режи ма работы первого программируемого источника напряжения, первый выход которого является выходом напряжения питания программатора, второй, третий выходы блока сопряжения соединены с соответствующими информационными входами декодера адреса и декодера напряжения соответственно, выходы которых соединены с входами задания режима работы второго программируемого источ- ника напряжения, .выходы которого являются адресными выходами программатора, четвертый, пятый, седьмой и восьмой выходы блока . сопряжения соединены соответственно с первым и вторым входами задания режима работы блока управления регистром и блока управления , девятый и десятый выходы блока сопряжения являются информационными выходами программатора, первый и вто- рой выходы блока управления регист- ром соединены соответственно с входами начальной установки и записи регистра, выходы которого соединены с одиннадцатым информационным входом блока сопряжения, вход датчика тока является входом контроля режима про

г 0 5 о ..

5

566

граммирования программатора, выход датчика тока соединен с первым входом формирователя длительности импульса программирования, первый выход которого соединен с двенадцатым входом блока сопряжения, первый выход блока сопряжения соединен с входом разрешения работы формирователя длительности импуль- .а программирования, отличающийся тем, что, с целью расширения функциональных возможностей, за счет расширения класса программируемых микро- , схем, в него введены второй и третий блоки управления, первый выход первого блока управления соединен с первыми входами разрешения работы второго и третьего блоков управления, второй и четвертый выходы первого блока управления соединены соответственно с входами разрешения работы и стробирования третьего блока управления, третий выход первого блока управления соединен соответственно с вторыми входами, разрешения работы ,третьего и второго блоков управления, второй выход формирователя длительности импульса программирования соединен с третьим входом разрешения работы третьего блока управления, выходы которого соединены с информационными входами регистра и являются информационными выходами первой группы программатора, второй выход перво- го программируемого источника напря- жения соединен с первым входом зада- : НИН режима второго блока управления, третий выход блока управления регистром соединен с вторым входом задания режима работы второго блока управления, выходы которого являются информационными выходами второй группы программатора, выходы шестой группы блока сопряжения соединены с информационными входами третьего блока уп- .равления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программирования микросхем постоянной памяти | 1987 |

|

SU1564689A1 |

| Программатор | 1987 |

|

SU1654869A1 |

| Устройство для ввода информации | 1988 |

|

SU1589265A1 |

| Программатор | 1986 |

|

SU1439677A1 |

| Устройство для формирования импульсов | 1985 |

|

SU1292168A1 |

| Программатор | 1987 |

|

SU1541669A1 |

| Устройство для формирования импульсов | 1987 |

|

SU1497724A1 |

| Устройство для программирования микросхем постоянной памяти | 1982 |

|

SU1134964A1 |

| Устройство для отображения символьной информации на экране видеоконтрольного блока | 1991 |

|

SU1836678A3 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММИРОВАНИЯ МИКРОСХЕМ ПОСТОЯННОЙ ПАМЯТИ | 1989 |

|

RU2047920C1 |

Изобретение относится к вычислительной технике и может быть использовано для программирования микросхем с программируемой логикой. Целью изобретения является расширение функциональных возможностей за счет расширения класса программируемых микросхем. Для этого в программатор введены второй и третий блоки управления, обеспечивающие формирование управляющих сигналов для программирования логических массивов с памятью. 1 ил.

| Устройство для программирования микросхем постоянной памяти | 1982 |

|

SU1134964A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Программатор для записи информа-ции B пОлупРОВОдНиКОВыЕ элЕМЕНТыпАМяТи | 1979 |

|

SU809355A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-12-23—Публикация

1986-09-10—Подача