Изобретение относится к импульсной технике и предназначено для формирования сигналов управления програматором интегральных схем.

Цель изобретения - расширение . функциональных возможностей путем обеспечения работы в автоматическом режиме.

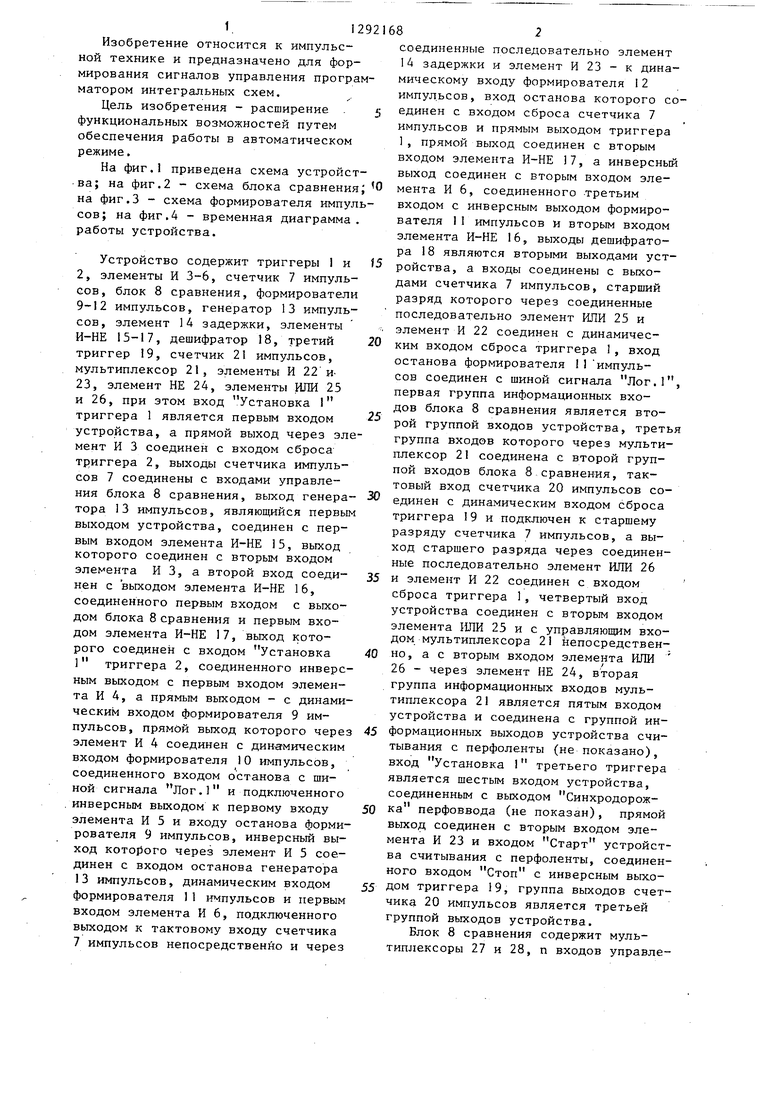

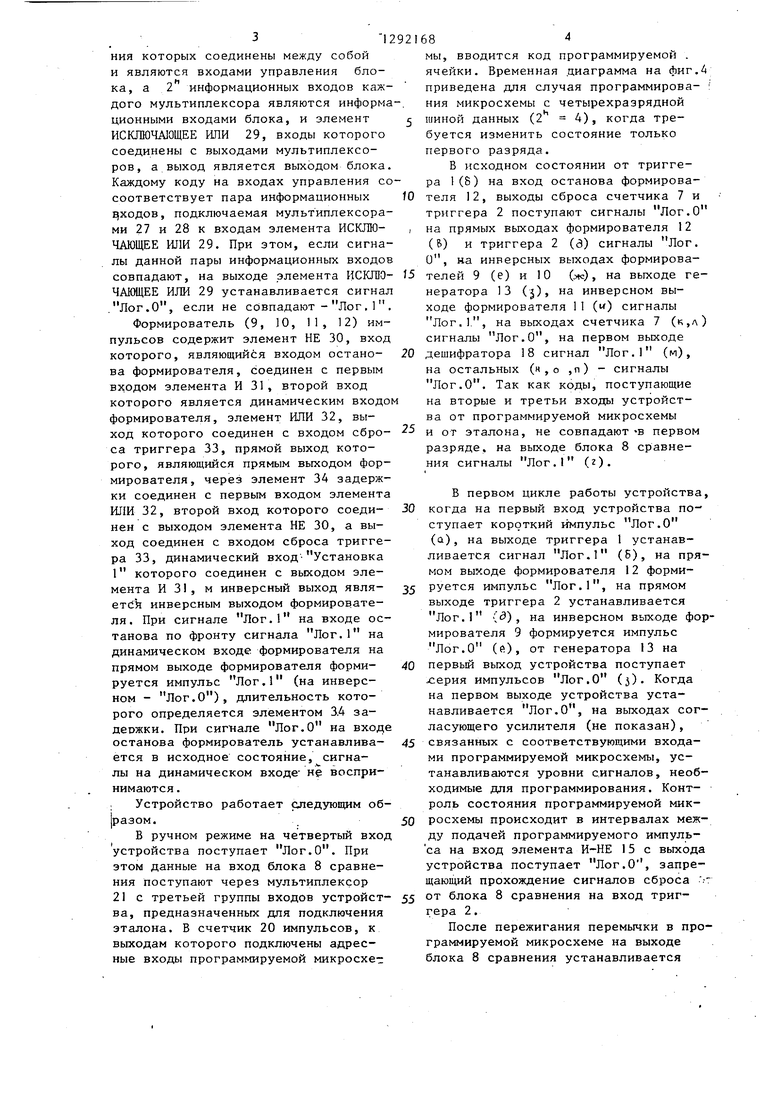

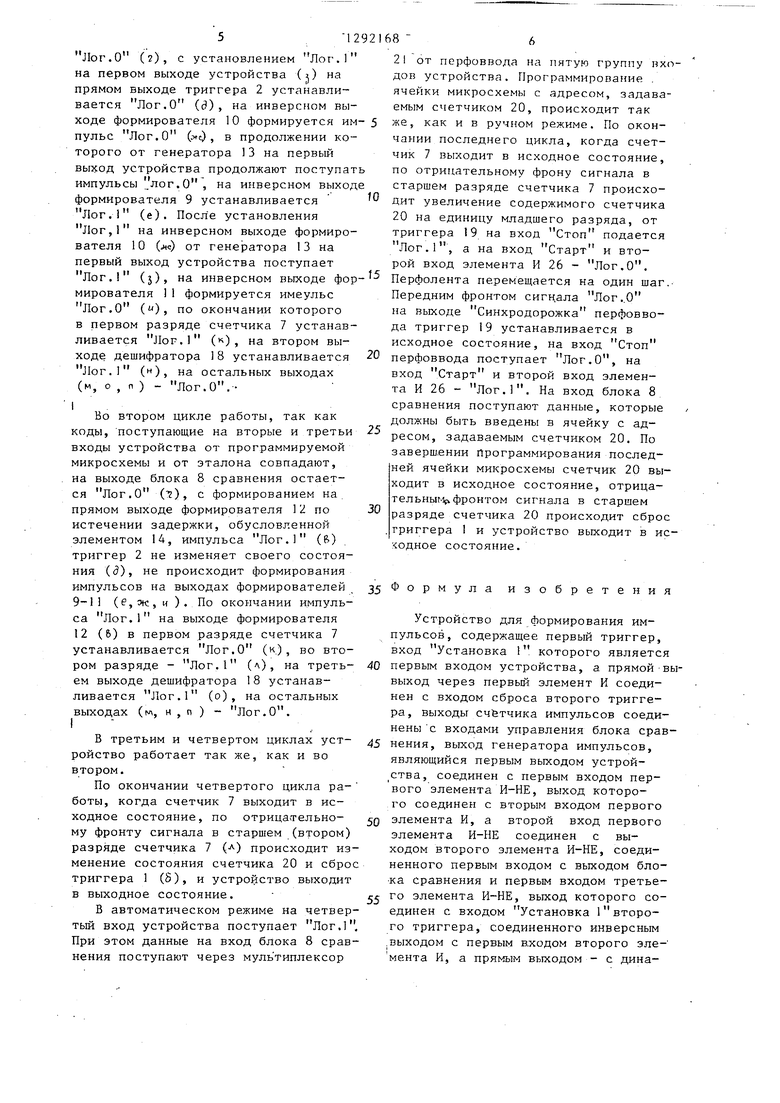

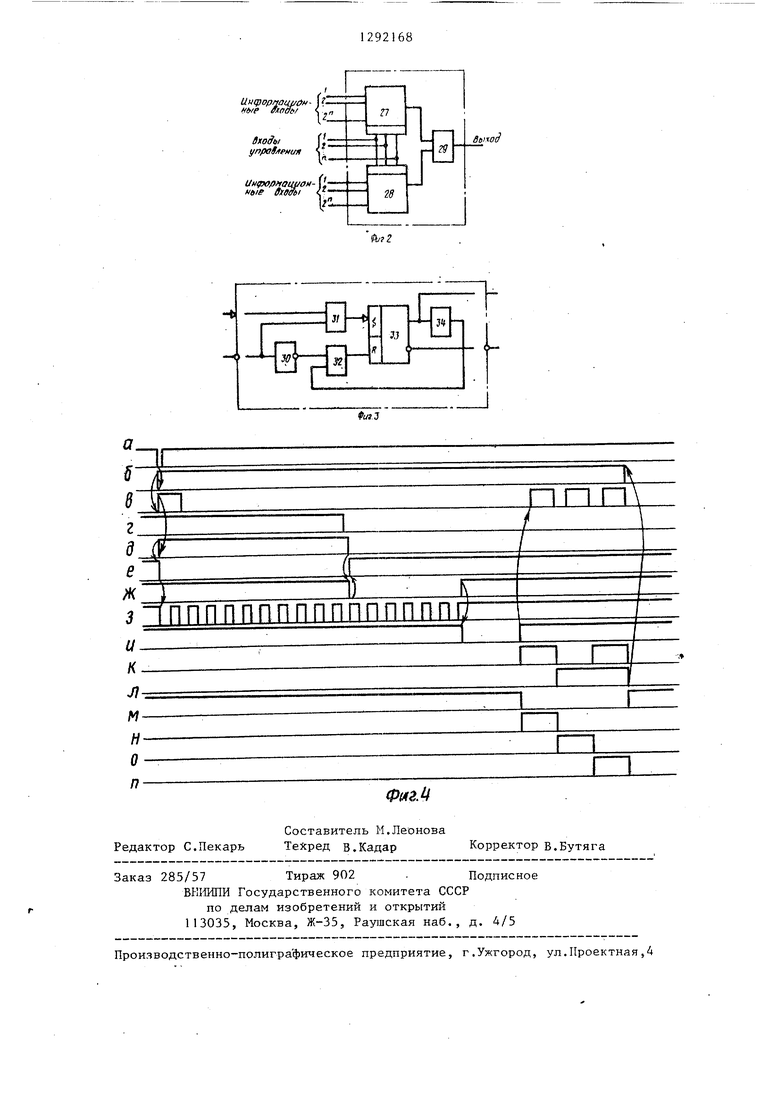

На фиг.1 приведена схема устройства; на фиг.2 - схема блока сравнения на фиг.З - схема формирователя импулсов; на фиг.4 - временная диаграмма, работы устройства.

Устройство содержит триггеры 1 и 2, элементы И 3-6, счетчик 7 импульсов, блок 8 сравнения, формирователи 9-12 импульсов, генератор 13 импульсов, элемент 14 задержки, элементы И-НЕ 15-17, дешифратор 18, третий триггер 19, счетчик 21 импульсов, мультиплексор 21, элементы И 22 и- 23, элемент НЕ 24, элементы .ИЛИ 25 и 26, при этом вход Установка 1 триггера 1 является первым входом устройства, а прямой выход через элемент И 3 соединен с входом сброса триггера 2, выходы счетчика импульсов 7 соединены с входами управления блока 8 сравнения, выход генера- тора 13 импульсов, являющийся первым выходом устройства, соединен с первым входом элемента И-НЕ 15, выход которого соединен с вторым входом элемента ИЗ, а второй вход соеди- нен с выходом элемента И-НЕ 16, соединенного первым входом с выходом блока 8 сравнения и первым входом элемента И-НЕ 17, выход которого соединен с входом Установка 1 триггера 2, соединенного инверсным выходом с первым входом элемента И 4, а прямым выходом - с динамическим входом формирователя 9 импульсов, прямой выход которого через элемент И 4 соединен с динамическим входом формирователя 10 импульсов, соединенного входом о станова с шиной сигнала Лог.1 и подключенного , инверсным выходом к первому входу элемента И 5 и входу останова формирователя 9 импульсов, инверсный выход KOTOjioro через элемент И 5 соединен с входом останова генератора 13 импульсов, динамическим входом формирователя 11 импульсов и первым входом элемента И 6, подключенного выходом к тактовому входу счетчика 7 импульсов непосредственно и через

соединенные последовательно элемент 14 задержки и элемент И 23 - к динамическому входу формирователя I2 импудьсов, вход останова которого соединен с входом сброса счетчика 7 импульсов и прямым выходом триггера 1, прямой выход соединен с вторым входом элемента И-НЕ 17, а инверсный выход соединен с вторым входом элемента И 6, соединенного третьим входом с инверсным выходом формирователя 11 импульсов и вторым входом элемента И-НЕ 16, выходы дешифратора 18 являются вторыми выходами устройства, а входы соединены с выходами счетчика 7 импульсов, старший разряд которого через соединенные последовательно элемент ИЛИ 25 и элемент И 22 соединен с динамическим входом сброса триггера I, вход останова формирователя 11 импульсов соединен с шиной сигнала Лог.1 первая группа информационных входов блока 8 сравнения является второй группой входов устройства, треть группа входов которого через мультиплексор 21 соединена с второй группой входов блока 8 сравнения, тактовый вход счетчика 20 импульсов соединен с динамическим входом сброса триггера 9 и подключен к старшему разряду счетчика 7 импульсов, а выход старшего разряда через соединенные последовательно элемент ИЛИ 26 и элемент И 22 соединен с входом сброса триггера 1, четвертый вход устройства соединен с вторым входом

элемента ИЛИ 25 и с управляющим входом мультиплексора 21 непосредственно, а с вторым входом элемента ИЛИ 26 - через элемент НЕ 24, вторая группа информационных входов мультиплексора 2 является пятым входом устройства и соединена с группой информационных выходов устройства считывания с перфоленты (не показано), вход Установка 1 третьего триггера является шестым входом устройства, соединенным с выходом Синхродорож- ка перфоввода (не показан), прямой выход соединен с вторым входом элемента И 23 и входом Старт устройства считывания с перфоленты, соединенного входом Стоп с инверсным выходом триггера 19, группа выходов счетчика 20 импульсов является третьей группой выходов устройства.

Блок 8 сравнения содержит мультиплексоры 27 и 28, п входов управле.3 1

ния которых соединены между собой и являются входами управления блока, а 2 информационных входов каждого мультиплексора являются информа ционными входами блока, и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 29, входы которого соединены с выходами мультиплексоров, а выход является выходом блока. Каждому коду на входах управления со соответствует пара информационных уходов, подключаемая мультиплексорами 27 и 28 к входам элемента ИСКЛЮ- ЧАЮЩЕЕ ИЛИ 29. При этом, если сигналы данной пары информационных входов совпадают, на выходе элемента PiCKTDO- ЧАЮЩЕЕ ИЛИ 29 устанавливается сигнал .Лог.О, если не совпадают - Лог,1,

Формирователь (9, 10, 11, 12) импульсов содержит элемент НЕ 30, вход которого, являющийся входом остано- ва формирователя, соединен с первым входом элемента И 31, второй вход которого является динамическим входо формирователя, элемент ИЛИ 32, выход которого соединен с входом сбро- са триггера 33, прямой выход которого, являющийся прямым выходом формирователя, через элемент 34 задержки соединен с первым входом элемента ИЛИ 32, второй вход которого соеди- нен с выходом элемента НЕ 30, а выход соединен с входом сброса триггера 33, динамический вход- Установка 1 которого соединен с выходом элемента И 31, м инверсный выход явля- етСй инверсным выходом формирователя. При сигнале Лог.1 на входе останова по фронту сигнала Лог.1 на динамическом входе формирователя на прямом выходе формирователя форми- руется импульс Лог.1 (на инверсном - Лог.О), длительность которого определяется элементом 3.4 задержки. При сигнале Лог.О на входе останова формирователь устанавлива- ется в исходное состояние, сигналы на динамическом входе- не воспринимаются .

; Устройство работает следующим об- |разом.

В ручном режиме на четвертый вход устройства поступает Лог.О. При этом данные на вход блока 8 сравнения поступают через мультиплексор 21 с третьей группы входов устройст- ва, предназначенных дпя подключения эталона. В счетчик 20 импульсов, к выходам которого подключены адресные входы программируемой микросхет

684

мы, вводится код программируемой . ячейки. Временная диаграмма на фиг. приведена для случая программирова- ния микросхемы с четырехразрядной шиной данных (2 4), когда требуется изменить состояние только первого разряда.

В исходном состоянии от триггера 1(S) на вход останова формирователя 12, выходы сброса счетчика 7 и триггера 2 поступают сигналы Лог.О на прямых выходах формирователя 12 (&) и триггера 2 (3) сигналы Лог. О, на инверсных выходах формирователей 9 (е) и 10 (лс), на выходе генератора 13 (j), на инверсном выходе формирователя 1 1 (и) сигналы Лог.., на вькодах счетчика 7 (к,л сигналы Лог.О, на первом выходе дешифратора 18 сигнал Лог.1 (м), на остальных (н,о ,л) - сигналы Лог.О. Так как коды, поступающие на вторые и третьи входы устройства от программируемой микросхемы и от эталона, не совпадают -в первом разряде, на выходе блока 8 сравнения сигналы Лог.1 (г).

В первом цикле работы устройства когда на первый вход устройства поступает короткий импульс Лог.О (а), на выходе триггера 1 устанавливается сигнал Лог.1 (5), на прямом выходе формирователя 12 формируется импульс Лог.1, на прямом выходе триггера 2 устанавливается Лог.1 (Э) , на инверсном выходе фомирователя 9 формируется импульс Лог.О (е), от генератора 13 на первый выход устройства поступает :ерия импульсов Лог.О (j). Когда на первом выходе устройства устанавливается Лог.О, на выходах согласующего усилителя (не показан), связанных с соответствующими входами программируемой микросхемы, устанавливаются уровни сигналов, необходимые для программирования. Контроль состояния программируемой микросхемы происходит в интервалах между подачей программируемого импуль- са на вход элемента И-НЕ I5 с выхода устройства поступает Лог.О , запрещающий прохождение сигналов сброса от блока 8 сравнения на вход триггера 2.

После пережигания перемычки в программируемой микросхеме на выходе блока 8 сравнения устанавливается

Jlor.O (г), с установлением Лог.1 на первом выходе устройства () на прямом выходе триггера 2 устанавливается Лог.О (д), на инверсном выходе формирователя 10 формируется им- 5 пульс Лог.О (лс) , в продолжении которого от генератора 13 на первый выход устройства продолжают поступать импульсы лог.О, на инверсном выходе

. лог. О

формирователя 9 устанавливается Лог.1 (е). Посл е установления Лог,1 на инверсном выходе формирователя 10 (лс) от гене|эатора 13 на первый выход устройства поступает

10

68 -6

21 от перфоввода на пятую группу вхо дов устройства. Программирова {ие . ячейки микросхемы с адресом, задаваемым счетчиком 20, происходит так же, как и в ручном режиме. По окончании последнего цикла, когда счетчик 7 выходит в исходное состояние, по отрицательному фрону сигнала в старшем разряде счетчика 7 происходит увеличение содержимого счетчика 20 на единицу младшего разряда, от триггера 19 на вход Стоп подается Лог.1, а на вход Старт и второй вход элемента И 26 - Лог.О.

Лог.1 (j), на инверсном выходе фор- - Перфолента перемещается на один шаг.мирователя 1 формируется имеульс Лог.о (), по окончании которого в первом разряде счетчика 7 устанавливается Jlor.l (i) , на втором выходе дешифратора 18 устанавливается Лог.1 (), на остальных выходах (м, о , г ) - Лог.О.I .

Во втором цикле работы, так как

коды, поступающие на вторые и третьи входы устройства от программируемой микросхемы и от эталона совпадают, на выходе блока 8 сравнения остается Лог.О (7), с формированием на. прямом выходе формирователя 12 по истечении задержки, обусловленной элементом 14, импульса Лог.1 (fe) триггер 2 не изменяет своего состояния (д), не происходит формирования импульсов на выходах формирователей 9-П (e,tHc, и ). По окончании импульса Лог.1 на выходе формирователя 12 (6) в первом разряде счетчика 7 устанавливается Лог.О (wj, во втором разряде - Лог.1 (л), на третьем выходе дешифратора 18 устанавливается Лог.1 (о), на остальных выходах (N, н , п ) - Лог.О.

В третьим и четвертом циклах устройство работает так же, как и во втором.

По окончании четвертого цикла работы, когда счетчик 7 выходит в исходное состояние, по отрицательному фронту сигнала в старшем (втором) разряде счетчика 7 (л) происходит изменение состояния счетчика 20 и сбро триггера 1 (S), и устройство выходит в выходное состояние.

В автоматическом режиме на четвертый вход устройства поступает Лог.1 При этом данные на вход блока 8 сравнения поступают через муль типлексор

68 -6

21 от перфоввода на пятую группу входов устройства. Программирова {ие . ячейки микросхемы с адресом, задаваемым счетчиком 20, происходит так же, как и в ручном режиме. По окончании последнего цикла, когда счетчик 7 выходит в исходное состояние, по отрицательному фрону сигнала в старшем разряде счетчика 7 происходит увеличение содержимого счетчика 20 на единицу младшего разряда, от триггера 19 на вход Стоп подается Лог.1, а на вход Старт и второй вход элемента И 26 - Лог.О.

0

5

0

Передним фронтом сигн.ала Лог..О на выходе Синхродорожка перфоввода триггер 19 устанавливается в исходное состояние, на вход Стоп перфоввода поступает Лог.О, на вход Старт и второй вход элемента И 26 - Лог.. На вход блока 8 сравнения поступают данные, которые должны быть введены в ячейку с адресом, задаваемым счетчиком 20. По завершении Программирования последней ячейки микросхемы счетчик 20 выходит в исходное состояние, отрица- тельныг-1( фронтом сигнала в старшем разряде счетчика 20 происходит сброс триггера I и устройство выходит в ис- кодное состояние.

35 Форму л а изо

р е т е н и я

0

5

0

5

Устройство для формирования импульсов, содержащее первый триггер, вход Установка 1 которого является первым входом устройства, а прямой-вы- выход через первый элемент К соединен с входом сброса второго триггера, выходы считчика импульсов соединены с входами управления блока сравнения, выход генератора импульсов, являющийся первым выходом устрой- ства, соединен с первым входом первого элемента И-НЕ, выход которого соединен с вторым входом первого элемента И, а второй вход первого элемента И-НЕ соединен с выходом второго элемента И-НЕ, соединенного первым входом с выходом бло- ка Сравнения и первым входом третьего элемента И-НЕ, выход которого соединен с входом Установка 1 второго триггера, соединенного инверсным .выходом с первым в.ходом второго эле- мента И, а прямым выходом - с дина712

мическим входом первого формирователя . импульсов , прямой выход которого через второй элемент И соединен с динамическим входом второго формирователя импульсов, соединенного входом останова .с шиной сигнала логической единицы и подключенного инверсным выходом к первом входу треть его элемента И и входу останова первого формирователя импульсов, ин- версный выход которого через третий элемент И соединен с входом останова генератора импульсов, динамическим входом третьего формирователя импульсов и первым входом четверто- го элемента И, подключенного к так- товому входу счетчика импульсов и к входу элемента задержки, вход останова четвертого формирователя импульсов соединен с входом сброса счетчи- ка импульсов и прямым выходом первого триггера, прямой выход соединен с вторым входом третьего элемента И-НЕ, а инверсный выход соединен с вторым входом четвертого элемента К, соединенного третьим входом с инверсным выходом третьего формирователя . импульсов и вторьм входом второго : элемента И-НЕ, выходы дешифратора яв- ляются вторыми выходами устройства, ,а входы соединены с выходами счетчика импульсов, вход останова третьего формирователя импульсов соединен с шиной сигнала логической единицы, первые информационные входы блока сравнения являются вторыми входами устройства, отличающееся тем, что, с целью расширения функцио

О 0 5

5

0

688

нальных возможностей путем обеспечения работы устройства в автоматическом режиме, в него введены третий триггер, второй счетчик импульсов, мультиплексор, пятый и шестой элементы И, элемент НЕ и первый и второй Элементы ИЛИ, при этом старший .разряд первого счетчика и пульсов соединен с вторым входом первого триггера через соединенные последо- вательно первый элемент ИЛИ и пятый элемент И, выход элемента задержки соединен с первым входом чёт- вертвго формирователя импульсов через шестой элемент И, вторая группа информационных входов блока сравнения соединена с третьей группой входов устройства через мультиплексор, вход второго счетчика импульсов соединен с первым входом третьего триггера и поключен к старшему разряду первого счетчика импульсов, а выход старшего разряда через второй элемент ИЛИ соединен с вторым входом пятого элемента И, четвертый вход устройства соединен с вторым входом первого элемента ИЛИ и с управляющим входом мультиплексора непосредственно, а с вторым входом второго элемента ИЛИ - через элемент НЕ, вторая группа информационных входов мультиплексора является пятым входом устройства, вход Установка 1 третьего триггера соединен с шестой шиной устройства,выход соединен с вторым входом шестого элемента И, группа выходов второго счетчика импульсов является третьей группой выходов устройства.

Редактор С.Пекарь

Ф(лзМ

Составитель М.Леонова

Техред В.Кадар Корректор В.Бутяга

Заказ 285/57 Тираж 902 . Подписное БРЛШПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полигра фическое предприятие, г.Ужгород, ул.Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования импульсов | 1987 |

|

SU1497724A1 |

| Устройство для формирования импульсов | 1984 |

|

SU1224995A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Устройство для контроля блоков оперативной памяти | 1989 |

|

SU1689994A2 |

| Устройство для реализации логических функций | 1989 |

|

SU1619247A1 |

| Программируемый контроллер | 1985 |

|

SU1509887A2 |

| Цифровой измеритель угловой скорости | 1985 |

|

SU1275292A1 |

| Устройство для программного управления | 1987 |

|

SU1596307A1 |

| Устройство для контроля многоканальных импульсных последовательностей | 1989 |

|

SU1732332A1 |

| Формирователь импульсных последовательностей для контроля запоминающих модулей на цилиндрических магнитных доменах | 1987 |

|

SU1513514A1 |

Изобретение предназначено для формирования сигналов управления программатором интегральных схем. Цель изобретения - расширение функциональных, возможностей устройства. Устройство содержит триггеры 1 и 2, злемен- ты И 4, 5 и 6, счетчик 7 импульсов, блок 8 сравнения, формирователи 9-12 импульсов, генератор 13-импульсов, элемент 14 задержки, элементы И-НЕ 15-17 и дешифратор 18. Введение в устройство триггера 19, счетчика 20 импульсов, мультиплексора 21, элементов И 22 и 23, элемента НЕ 24, и элементов ИЛИ 25 и 26 с образованием новых функциональных связей обеспечивает работу устройства в автоматическом режиме. 4 ил. flwA.J ND СО 1чЭ а 00

| Устройство для формирования импульсов | 1982 |

|

SU1064443A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для формирования импульсов | 1984 |

|

SU1224995A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-02-23—Публикация

1985-07-02—Подача