1

Изобретение относится к вычислительной технике, в частности к вычислительным системам параллельной обработки данных, и предназначено доя параллельного выполнения операций суммирования чисел и определени максимального или минимального числа из массива чисел.

Цель изобретения - расширение функциональных возможностей путем увеличения диапазона представления суммируемых чисел.

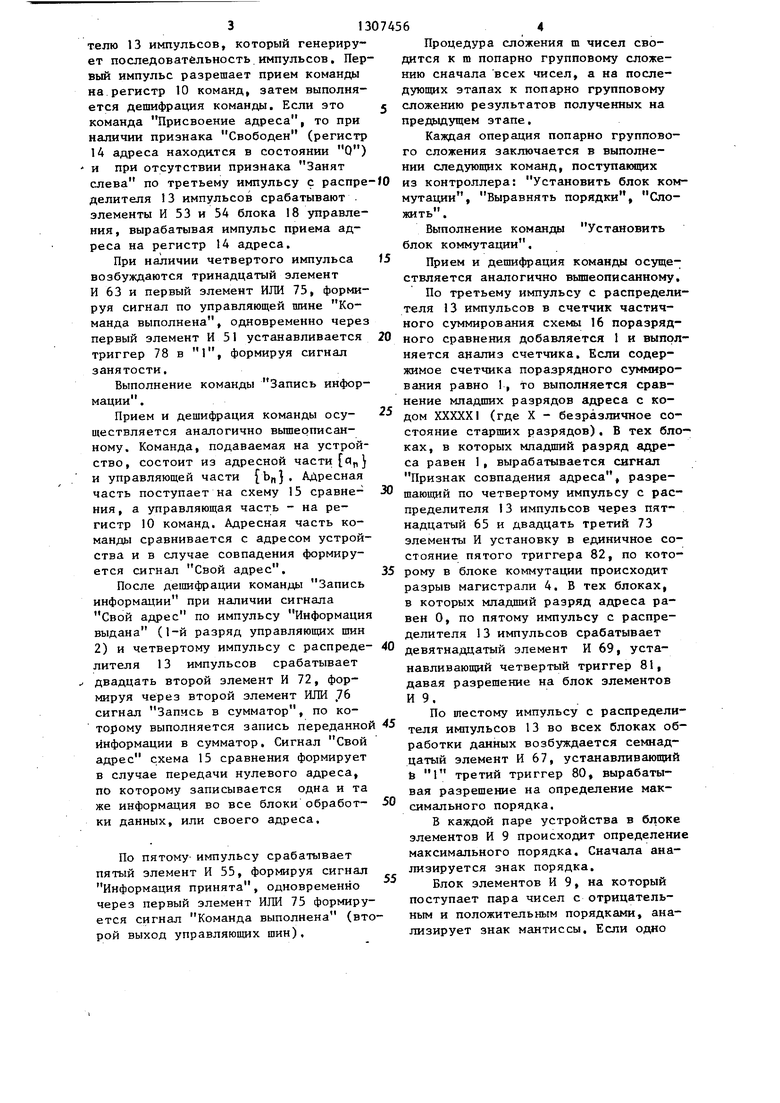

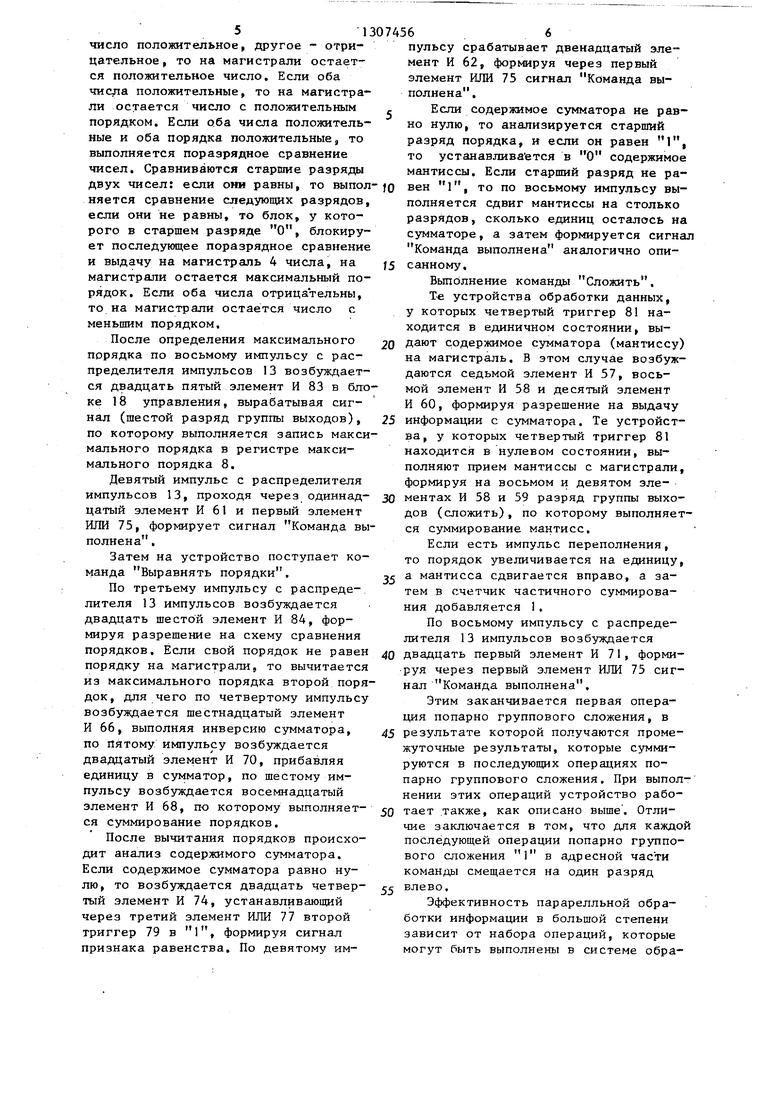

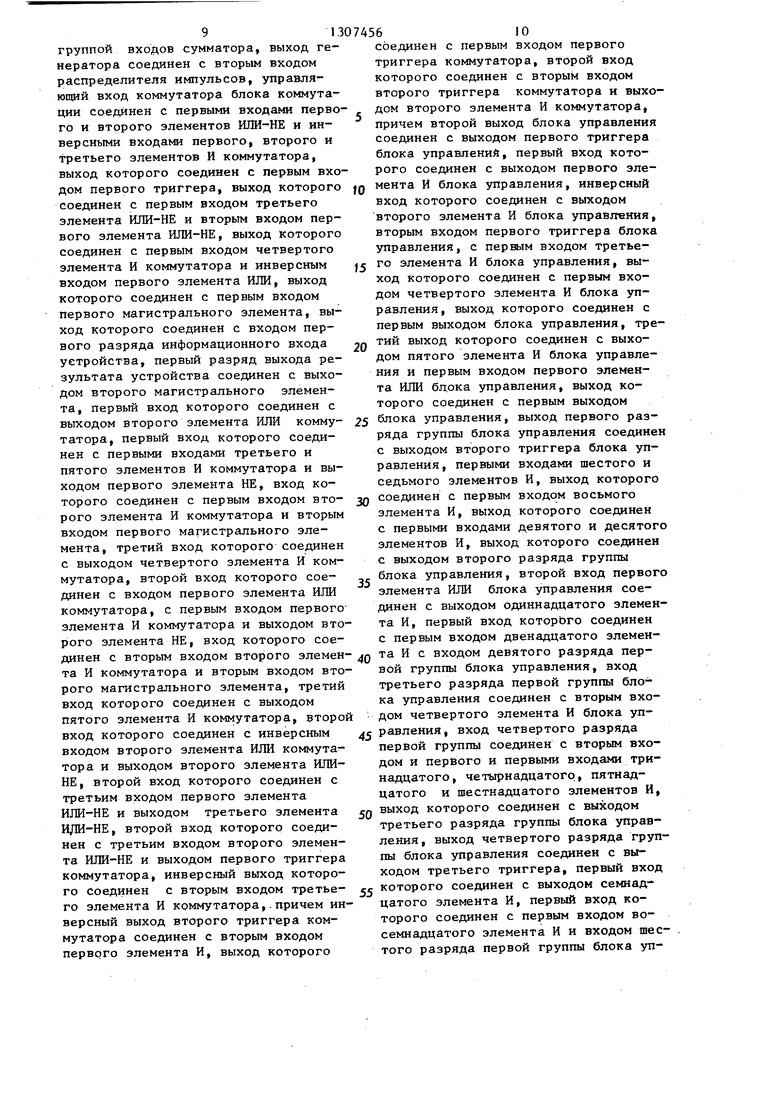

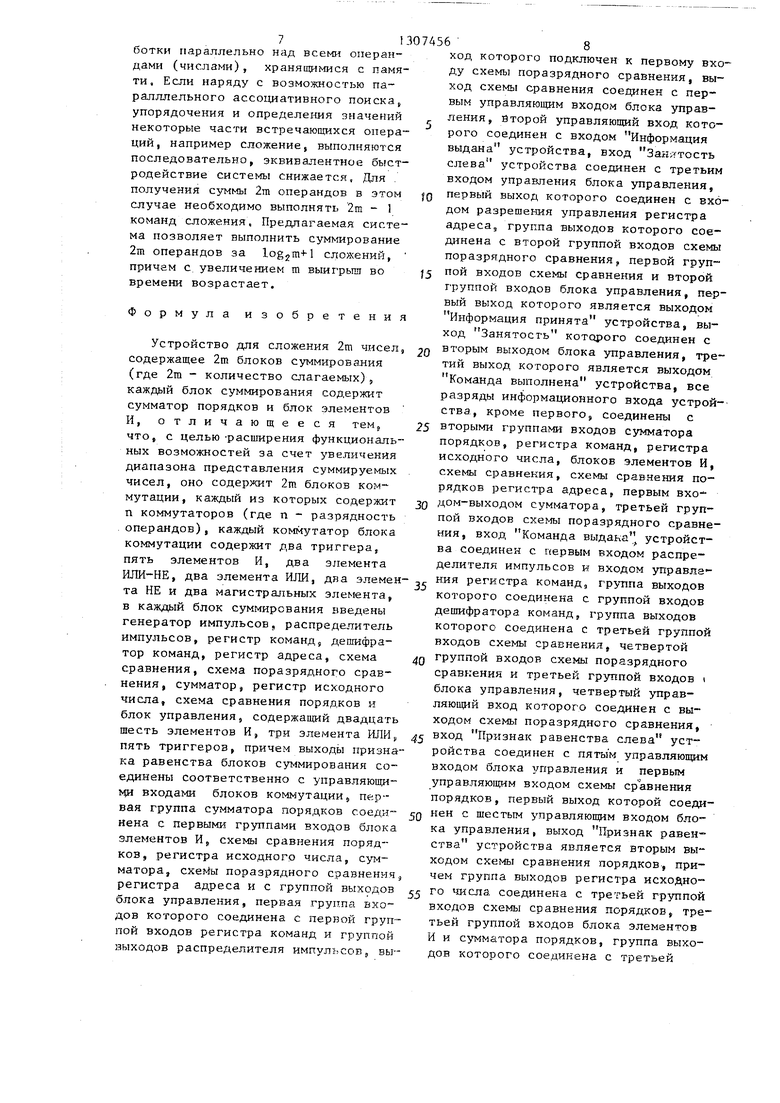

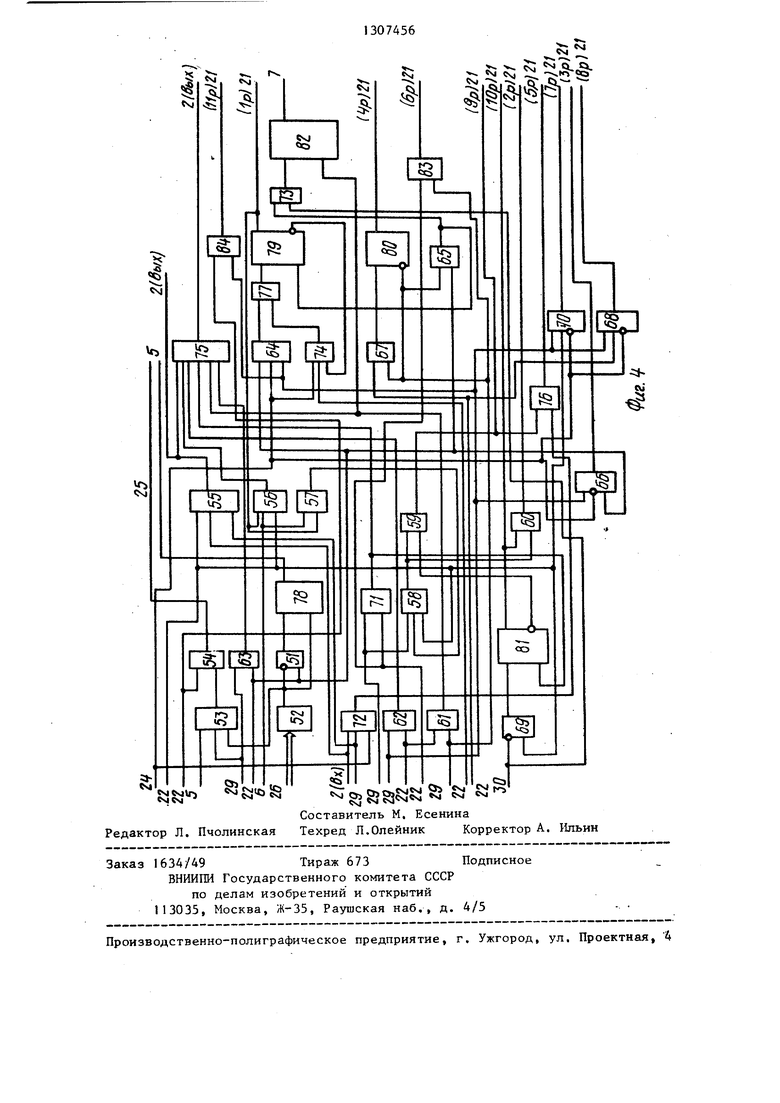

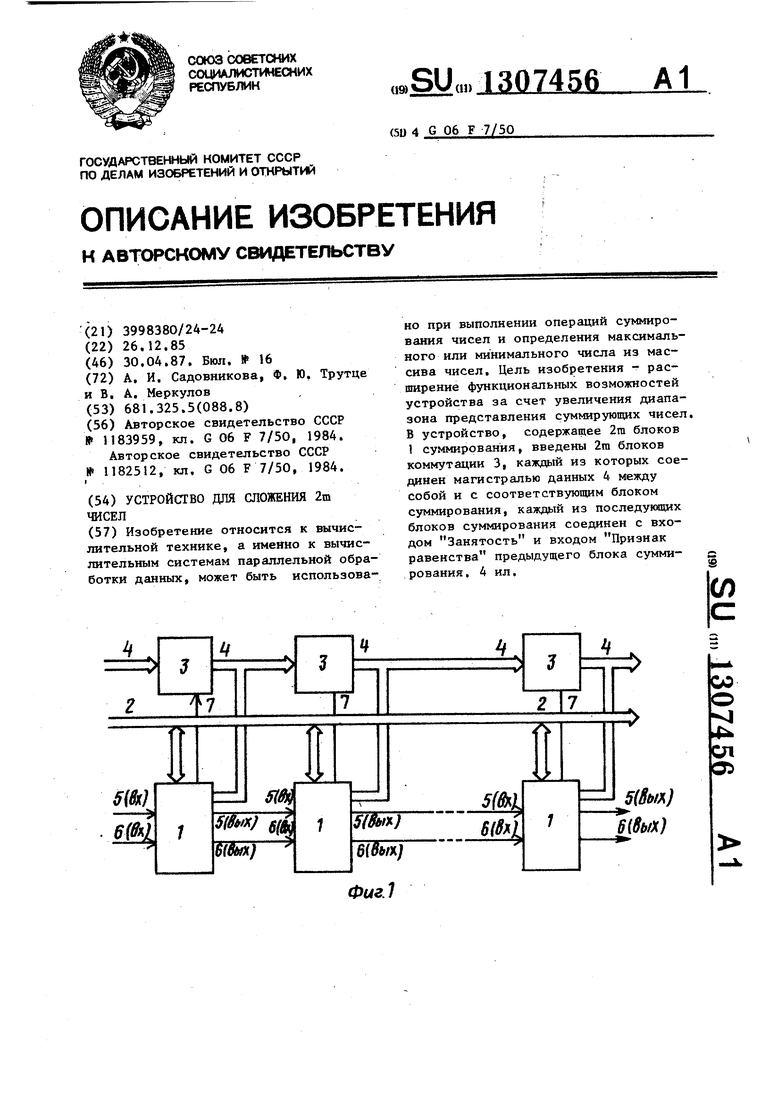

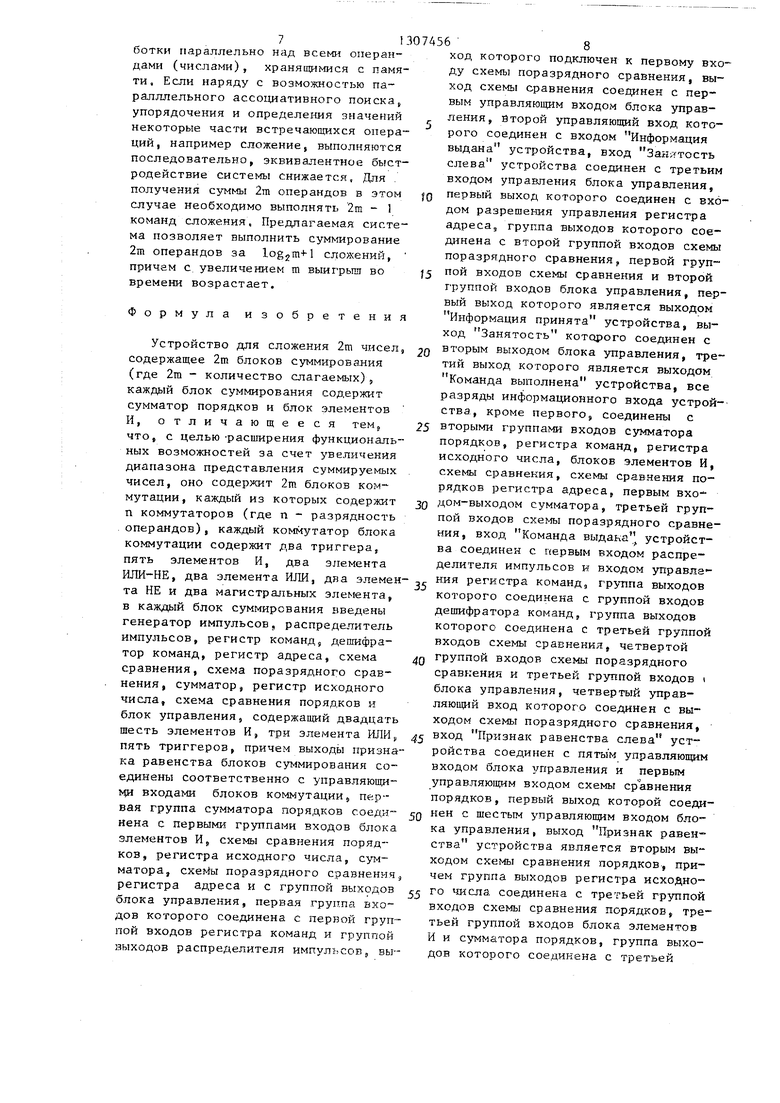

На фиг. 1 представлена функциональная схема устройства для сложения 2т чисел; на фиг. 2 - функциональная схема блока суммирования; на фиг. 3 - функциональная схема блка коммутации; на фиг. 4 - функциональная схема блока управления блок суммирования.

Устройство сложения 2т чисел содержит 2т блоков 1 суммирования, соединенных управляющими шинами 2, 2т блоков 3 коммутации, каждый из которых соединен информационным входом между собой и с соответствующим блоком 1 суммирования, каждый из последующих блоков 1 суммирования соединен с предыдущим входом 5 Занятост и входом 6 Признак равенства, каждый блок 1 суммирования выходом 7 сединен с входом управления соответствующего блока коммутации.

Блок суммирования 1 содержит регистр 8 хранения исходного числа, блок элементов И 9, регистр 10 команд, дешифратор 11 команд, генератор 12, распределитель 13 импульсов, регистр 14 адреса, схему 15 сравнения, схему 16 поразрядного сравнения, сумматор 17, блок 18 управления, схему 19 сравнения порядков, сумматор 20 порядков, группа входов 21 блока управления которого соединена с первыми группами входов блока злементов И 9, схемы 19 сравнения порядков, регистра 8, сумматора 17, схемы 16 поразрядного сравнения, регистра 14 адреса и группой выходов блока 18 управления, группу выходов 22 распределителя импульсов выход 23 распределителя импульсов, выход 24 схемы сравнения 15, первый выход 25 блока управления, группу выходов 26 регистра адреса, первый управляюш й вход 27 блока управления, выход 28 регистра команд, выход 29 дешифратора команд, выход 30

5

0

5

признака совпадения адреса схемы поразрядного сравнения, шестой управ- . ляющий вход 31 блока управления, выход 32 генератора импульсов, выход 33 сумматора порядков и третью груп- пу. входов 34 сумматора..

Блок 3 коммутации содержит п коммутаторов (где п - разрядность магистрали данных) , каждая из которых содержит первый 35 и второй 36 триг- герь, первый 37 и второй 38 магистральные элементы, первый 39, второй 40, третий 41, четвертый 42 и пятый 43 элементы И, первый 44, второй 45 и третий 46 элементы ИЛИ-НЕ, первый 47 и второй 48 элементы ИЛИ и элементы НЕ 49 и 50.

Блок управления содержит первый 51 -двадцать четвертый 74 элементы И, первый 75, второй 76 и третий 77 элементы ИЛИ, первый 78, второй 79, третий 80, четвертый 81 и пятый 82 триггеры.

Устройство работает следующим образом.

Процедура параллельного суммирования сводится к выполнению следующих команд: Присвоение адреса, Запись информации, Установка блока коммутации, Выравнять порядки, Сложить.

Перед началом работы каждому блоку суммирования присваивается адрес. Адреса присваиваются последовательно слева направо. Затем выполняется запись информации по адресу. После того, как информация записана, во все блоки поступает команда Установка блока коммутации, по которой магистраль 4 разрывается таким образом, что обмен информацией может выполняться только по парам. По команде Выравнять порядки происходит попарное выравнивание порядков, затем по команде Сложить выполняется параллельное сложение чисел в каждой па0

5

0

50

55

ре, а результат записывается в блоки суммирования с четным адресом. Затем повторяется выполнение команд Установка ШУП, Выравнять порядки и Сложить только в четных блоках, до тех пор пока не сложатся два последних числа.

Выполнение команды Присвоение адреса.

По второму разряду управляющих шин поступает сигнал (Команда выдана), разрешающий работу распредели3130

телю 13 импульсов, который генерирует последовательность.импульсов. Первый импульс разрешает прием команды на регистр 10 команд, затем выполняется дешифрация команды. Если это команда Присвоение адреса, то при наличии признака Свободен (регистр 14 адреса находится в состоянии О) и при отсутствии признака Занят

Каждая операция попарно группового сложения заключается в выполнении следующих команд, поступающих

J5

20

слева по третьему импульсу с распре-JO из контроллера: Установить блок коммутации, Выравнять порядки, Сложить.

Выполнение команды Установить блок коммутации.

Прием и дешифрация команды осуществляется аналогично вышеописанному.

По третьему импульсу с распределителя 13 импульсов в счетчик частичного суммирования схемы 16 поразрядного сравнения добавляется 1 и выполняется анализ счетчика. Если содержимое счетчика поразрядного суммирования равно 1, то выполняется сравнение младших разрядов адреса с ко дом XXXXXI (где X - безразличное состояние старших разрядов) . В тех бло- ках, в которых младший разряд адреса равен 1, вырабатывается сигнал Признак совпадения адреса, разрешающий по четвертому импульсу с распределителя 13 импульсов через пятнадцатый 65 и двадцать третий 73 элементы И установку в единичное состояние пятого триггера 82, по кото35 рому в блоке коммутации происходит разрыв магистрали 4. В тех блоках, в которых младший разряд адреса равен О, по пятому импульсу с распределителя 13 импульсов срабатывает

делителя 13 импульсов срабатывают . элементы И 53 и 54 блока 18 управления , вырабатывая импульс приема адреса на регистр 14 адреса.

При наличии четвертого импульса возбуждаются тринадцатый элемент И 63 и первый элемент ИЛИ 75, формируя сигнал по управляющей шине Команда выполнена, одновременно через первый элемент И 51 устанавливается триггер 78 в 1, формируя сигнал занятости.

Выполнение команды Запись информации .

Прием и дешифрация команды осуществляется ансшогично вьшеописан- ному. Команда, подаваемая на устройство, состоит из адресной части и управляющей части . Адресная часть поступает на схему 15 сравнения , а управляющая часть - на регистр 10 команд. Адресная часть команды сравнивается с адресом устройства и в случае совпадения формируется сигнал Свой адрес.

После дешифрации команды Запись информации при наличии сигнала Свой адрес по импульсу Информация выдана (1-й разряд управляющих шин

30

2) и четвертому импульсу с распреде- 40 девятнадцатый элемент И 69, уста- лителя 13 импульсов срабатывает „авливающий четвертый триггер 81, двадцать второй элемент И 72, формируя через второй элемент ИЛИ ,76 сигнал Запись в сумматор, по кодавая разрешение на блок элементов И 9.

По шестому импульсу с распределиторому выполняется запись переданной 45 импульсов 13 во всех блоках обйнформации в сумматор. Сигнал Свой адрес схема 15 сравнения формирует в случае передачи нулевого адреса, по которому записывается одна и та же информация во все блоки обработки данных, или своего адреса.

По пятому импульсу срабатывает пятый элемент И 55, формируя сигнал Информация принята, одновременно через первый элемент ИЛИ 75 формируется сигнал Команда выполнена (второй выход управляющих шин).

50

55

работки данных возбуждается семнадцатый элемент И 67, устанавливающий и I третий триггер 80, вырабатывая разрешение на определение максимального порядка.

В каждой паре устройства в блоке элементов И 9 происходит определение максимального порядка. Сначала анализируется знак порядка.

Блок элементов И 9, на который поступает пара чисел с отрицательным и положительным порядками, анализирует знак мантиссы. Если одао

Процедура сложения m чисел сводится к m попарно групповому сложению сначала всех чисел, а на последующих этапах к попарно групповому сложению результатов полученных на предадущем этапе.

Каждая операция попарно группового сложения заключается в выполнении следующих команд, поступающих

из контроллера: Установить блок коммутации, Выравнять порядки, Сложить.

девятнадцатый элемент И 69, уста- „авливающий четвертый триггер 81,

давая разрешение на блок элементов И 9.

По шестому импульсу с распредели импульсов 13 во всех блоках об0

5

работки данных возбуждается семнадцатый элемент И 67, устанавливающий и I третий триггер 80, вырабатывая разрешение на определение максимального порядка.

В каждой паре устройства в блоке элементов И 9 происходит определение максимального порядка. Сначала анализируется знак порядка.

Блок элементов И 9, на который поступает пара чисел с отрицательным и положительным порядками, анализирует знак мантиссы. Если одао

число положительное, другое - отрицательное, то на магистрали остается положительное число. Если оба числа положительные, то на магистрали остается число с положительным порядком. Если оба числа положительные и оба порядка положительные, то выполняется поразрядное сравнение чисел. Сравниваются старшие разряды двух чисел: если они равны, то выпол няется сравнение следующих разрядов, если они не равны, то блок, у которого в старшем разряде О, блокирует последующее поразрядное сравнение и выдачу на магистраль 4 числа, на магистрали остается максимальный порядок. Если оба числа отрицательны, то на магистрали остаётся число с меньшим порядком.

После определения максимального порядка по восьмому импульсу с распределителя импульсов 13 возбуждается двадцать пятый элемент И 83 в блоке 18 управления, вырабатывая сиг

нал (шестой разряд группы выходов), 25 информации с сумматора. Те устройстпо которому выполняется запись максимального порядка в регистре максимального порядка 8.

Девятый импульс с распределителя импульсов 13, проходя через одиннадцатый элемент И 61 и первый элемент ИЛИ 75, формирует сигнал Команда выполнена ,

Затем на устройство поступает команда Выравнять порядки.

По третьему импульсу с распределителя 13 импульсов возбуждается двадцать шестой элемент И 84, формируя разрешение на схему сравнения

ва, у которых четвертый триггер 81 находится в нулевом состоянии, выполняют прием мантиссы с магистрали, формируя на восьмом и девятом эле30 ментах И 58 и 59 разряд группы выходов (сложить), по которому выполняется суммирование мантисс.

Если есть импульс переполнения, то порядок увеличивается на единицу,

г а мантисса сдвигается вправо, а затем в счетчик частичного суммирования добавляется .

По восьмому импульсу с распределителя 13 импульсов возбуждается порядков. Если свой порядок не равен 40 двадцать первый элемент И 71, форми- порядку на магистрали, то вычитается .руя через первый элемент ИЛИ 75 сиг- из максимального порядка второй поря- нал Команда выполнена, док, для чего по четвертому импульсу Этим заканчивается первая опера- возбуждается шестнадцатый элемент ция попарно группового сложения, в И 66, выполняя инверсию сумматора, 5 результате которой получаются промежуточные результаты, которые суммируются в последующих операциях попарно группового сложения. При выполнении этих операций устройство рабопо Пятому импульсу возбуждается двадцатый элемент И 70, прибавляя единицу в сумматор, по шестому импульсу возбуждается восемнадцатый

элемент И 68, п-о которому выполняет- ;Q тает также, как описано выше . Отли- ся суммирование порядков.

После вычитания порядков происходит анализ содержимого сумматора. Если содержимое сумматора равно нулю, то возбуждается двадцать четвертый элемент И 74, устанавливающий через третий элемент ИЛИ 77 второй триггер 79 в 1, формируя сигнал признака равенства. По девятому имчие заключается в том, что для каждой последующей операции попарно группового сложения в адресной части команды смещается на один разряд с к влево,

Эффективность парарелльной обработки информации в большой степени зависит от набора операций, которые могут быть выполнены в системе обра

5

0

пульсу срабатывает двенадцатый элемент И 62, формируя через первый элемент ИЛИ 75 сигнал Команда выполнена.

Если содержимое сумматора не равно нулю, то анализируется старший разряд порядка, и если он равен 1, то устанавливается в О содержимое мантиссы. Если старший разряд не равен 1, то по восьмому импульсу выполняется сдвиг мантиссы на столько разрядов, сколько единиц осталось на сумматоре, а затем формируется сигнал Команда выполнена аналогично описанному.

Вьтолнение команды Сложить.

Те устройства обработки данных, у которых четвертый триггер 81 находится в единичном состоянии, выдают с-одержимое сумматора (мантиссу) на магистраль. В этом случае возбуждаются седьмой элемент И 57, восьмой элемент И 58 и десятый элемент И 60, формируя разрешение на выдачу

ва, у которых четвертый триггер 81 находится в нулевом состоянии, выполняют прием мантиссы с магистрали, формируя на восьмом и девятом элементах И 58 и 59 разряд группы выходов (сложить), по которому выполняется суммирование мантисс.

Если есть импульс переполнения, то порядок увеличивается на единицу,

а мантисса сдвигается вправо, а затем в счетчик частичного суммирования добавляется .

По восьмому импульсу с распредетает также, как описано выше . Отли-

чие заключается в том, что для каждой последующей операции попарно группового сложения в адресной части команды смещается на один разряд влево,

Эффективность парарелльной обработки информации в большой степени зависит от набора операций, которые могут быть выполнены в системе обрагруппой входов сумматора, выход генератора соединен с вторым входом распределителя импульсов, управляющий вход коммутатора блока коммутации соединен с первыми входами первого и второго элементов ИЛИ-НЕ и инверсными входами первого, второго и третьего элементов И коммутатора, выход которого соединен с первым входом первого триггера, выход которого соединен с первым входом третьего элемента ИЛИ-НЕ и вторым входом первого элемента ШШ-НЕ, выход которого соединен с первым входом четвертого элемента И коммутатора и инверсным входом первого элемента ИЛИ, выход которого соединен с первым входом первого магистрального элемента, выход которого соединен с входом первого разряда информационного входа устройства, первый разряд выхода результата устройства соединен с выходом второго магистрального элемента, первый вход которого соединен с

выходом второго элемента ИЛИ комму- 25 блока управления, выход первого раз- татора, первый вход которого соединен с первыми входами третьего и пятого элементов И коммутатора и выходом первого элемента НЕ, вход которого соединен с первым входом вто- зо рого элемента И коммутатора и вторым входом первого магистрального элемента, третий вход которого соединен с выходом четвертого элемента И коммутатора, второй вход которого соединен с входом первого элемента ИЛИ коммутатора, с первым входом первого элемента И коммутатора и выходом второго элемента НЕ, вход которого соединен с вторым входом второго элемен- Q та И с входом девятого разряда пер- та И коммутатора и вторым входом вто- вой группы блока управления, вход

35

ряда группы блока управления соединен с выходом второго триггера блока управления, первыми входами шестого и седьмого элементов И, выход которого соединен с первым входом восьмого элемента И, выход которого соединен с первыми входами девятого и десятого элементов И, выход которого соединен с выходом второго разряда группы блока управления, второй вход первого элемента ИЛИ блока управления соединен с выходом одиннадцатого элемента И, первый вход которЬго соединен с первым входом двенадцатого злеменрого магистрального элемента, третий вход которого соединен с выходом пятого элемента И коммутатора, второй вход которого соединен с инверсным входом второго элемента ИЛИ коммута тора и выходом второго элемента ИЛИ- НЕ, второй вход которого соединен с третьим входом первого элемента ИЛИ-НЕ и выходом третьего элемента ИДИ-НЕ, второй вход которого соединен с третьим входом второго элемента ИЛИ-НЕ и выходом первого триггера коммутатора, инверсный выход которого соединен с вторым входом третьего элемента И коммутатора,.причем инверсный выход второго триггера коммутатора соединен с вторым входом первого элемента И, выход которого

соединен с первым входом первого триггера коммутатора, второй вход которого соединен с вторым входом второго триггера коммутатора и выходом второго элемента И коммутатора, причем второй выход блока управления соединен с выходом первого триггера блока управлений, первый вход которого соединен с выходом первого элеQ мента И блока управления, инверсный вход которого соединен с выходом второго элемента И блока управления, вторым входом первого триггера блока управления, с первым входом третье го элемента И блока управления, выход которого соединен с первым входом четвертого элемента И блока управления , выход которого соединен с первым выходом блока управления, третий выход которого соединен с выходом пятого элемента И блока управления и первым входом первого элемента ИЛИ блока управления, выход которого соединен с первым выходом

0

25 блока управления, выход первого раз- зо Q та И с входом девятого разряда пер- вой группы блока управления, вход

35

ряда группы блока управления соединен с выходом второго триггера блока управления, первыми входами шестого и седьмого элементов И, выход которого соединен с первым входом восьмого элемента И, выход которого соединен с первыми входами девятого и десятого элементов И, выход которого соединен с выходом второго разряда группы блока управления, второй вход первого элемента ИЛИ блока управления соединен с выходом одиннадцатого элемента И, первый вход которЬго соединен с первым входом двенадцатого злементретьего разряда первой группы блока управления соединен с вторым входом четвертого элемента И блока уп- с равления, вход четвертого разряда первой группы соединен с вторым входом и первого и первыми входами тринадцатого, четырнадцатого, пятнадцатого и шестнадцатого элементов И, выход которого соединен с выходом третьего разряда группы блока управления, выход четвертого разряда группы блока управления соединен с выходом третьего триггера, первый вход которого соединен с выходом семнад- цатого элемента И, первый вход которого соединен с первым входом восемнадцатого элемента И и входом шестого разряда первой группы блока уп0

5

ботки параллельно над всеми операндами (числами), хранящимися с памяти. Если наряду с возможностью па ралллельного ассоциативного поиска, упорядочения и определения значений некоторые части встречающихся операций, например сложение, выполняются последовательно, эквивалентное быстродействие системы снижается. Для . получения суммы 2га операндов в этом случае необходимо выполнять 2т - 1 команд сложения, Предлагаемая система позволяет выполнить суммирование 2т операндов за log2m- -l сложений, причем с. увеличением m выигрьшг во времени возрастает.

Формула изобретени

Устройство для сложения 2т чисел содержащее 2т блоков суммирования (где 2т - количество слагаемых), каждый блок суммирования содержит сумматор порядков и блок элементов И, отличающееся тем, что, с целью -расширения функциональных возможностей за счет увеличения диапазона представления суммируемых чисел, оно содержит 2т блоков ком-мутации, каждый из которых содержит п коммутаторов (где п - разрядность . операндов), каждый коммутатор блока коммутации содержит два триггера, пять элементов И, два элемента

ИЛИ-НЕ, два элемента ИЛИ, два элемен- ния регистра команд группа выходов

та НЕ и два магистральных элемента, в каждый блок суммирования введены генератор импульсов, распределитель импульсов, регистр команд, депшфра- тор команд, регистр адреса, схема 0 сравнения, схема поразрядного сравнения, сумматор, регистр исходного числа, схема сравнения порядков я блок управления, содержащий двадцать шесть элементов И, три элемента ИЛИ, пять триггеров, причем выходы признака равенства блоков суммирования соединены соответственно с управляющими входами блоков коммутации первая группа сумматора порядков соеди- 50 иена с первыми группами входов блока элементов И, схемы сравнения порядков, регистра исходного числа, cyr-i-которого соединена с группой входов дешифратора команд, группа выходов которого соединена с третьей группой входов схемы сравнения, четвертой группой входов схемы поразрядного сравнения и третьей группой входов блока управления, четвертый управляющий вход которого соединен с выходом схемы поразрядного сравнения, вход Признак равенства слева устройства соединен с пятым управляющим входом блока управления и первым управляющим входом схемы ср авнения порядков, первый выход которой соеди нен с щестым yпpaвляюшJ м входом блока управления, выход Признак равенства устройства является вторым выходом схемы сравнения порядков, причем группа выходов регистра исходнокоторого соединена с группой входов дешифратора команд, группа выходов которого соединена с третьей группой входов схемы сравнения, четвертой группой входов схемы поразрядного сравнения и третьей группой входов блока управления, четвертый управляющий вход которого соединен с выходом схемы поразрядного сравнения, вход Признак равенства слева устройства соединен с пятым управляющим входом блока управления и первым управляющим входом схемы ср авнения порядков, первый выход которой соединен с щестым yпpaвляюшJ м входом блока управления, выход Признак равенства устройства является вторым выходом схемы сравнения порядков, причем группа выходов регистра исходноматора, схеМы поразрядного сравнения, регистра адреса и с группой выходов - го шсла соединена с третьей группой блока управления, первая группа вхо входов схемы сравнения порядков, тредов которого соединена с первой груп- тьей группой входов блока элементов пой входов регистра команд и группой И и с мматора порядков, группа выхо- зыходов распределителя импульсов, вы™ дов которого соединена с третьей

ход которого подключен к первому входу схемы поразрядного сравнения, выход схемы сравнения соединен с первым управляющим входом блока управ- ления, Итерой управляющий вход которого соединен с входом Информация выдана устройства, вход Зан тость слева устройства соединен с третьим входом управления блока управления,

первый выход которого соединен с входом разрешения управления регистра адреса,, группа выходов которого соединена с второй группой входов схемы поразрядного сравнения, первой группой входов схемы сравнения и второй группой входов блока, управления, первый выход которого является выходом Информация принята устройства, выход Занятость которого соединен с

вторым выходом блока управления, третий выход которого является выходом Команда выполнена устройства, все разряды информационного входа устройства, кроме первого, соединены с

вторыми группами входов сумматора порядков, регистра команд, регистра исходного числа, блоков элементов И, схемы сравнекия, схемы сравнения порядков регистра адреса, первым входом-выходом сумматора, третьей группой входов схемы поразрядного сравнения, вход Команда выдана устройства соединен с первым входом распре- делителя импульсов и входом управлакоторого соединена с группой входов дешифратора команд, группа выходов которого соединена с третьей группой входов схемы сравнения, четвертой группой входов схемы поразрядного сравнения и третьей группой входов блока управления, четвертый управляющий вход которого соединен с выходом схемы поразрядного сравнения, вход Признак равенства слева устройства соединен с пятым управляющим входом блока управления и первым управляющим входом схемы ср авнения порядков, первый выход которой соединен с щестым yпpaвляюшJ м входом блока управления, выход Признак равенства устройства является вторым выходом схемы сравнения порядков, причем группа выходов регистра исходного шсла соединена с третьей группой входов схемы сравнения порядков, третьей группой входов блока элементов И и с мматора порядков, группа выхо- дов которого соединена с третьей

равления, вход пятого разряда первой группы соединен с первыми входами пятого, девятнадцатого и двадцатого элементов И и вторыми входами шестого и восьмого элементов И блока управления, третий вход которого соединен с первым входом двадцать первого элемента И и входом первого разряда группы третьей группы блока управления, вход второго разряда третьей группы соединен с вторыми входами третьего и тринадцатого элементов И блока управления, выход которого соединен с третьим входом первого элемента ЕТШ, четвертый вход которого соединен с . выходом шестого элемента И, третий вход которого соединен с вторым входом седьмого элемента И и с пятым управляющим входом блока управления, третий управляющий вход блока управления соединен с третьим входом третьего элемента И блока управления, входы второй группы блока управления соединены соответственно с входами второго элемента И блока управления, четвертый управляющий вход блока управления соединен с вторым входом девятнадцатого элемента И и первым входом двадцать третьего элемента И, выход двадцать второго элемента И соединен с первым входом второго элемента ИЛИ блока управления, выход которого соединен с выходом пятого разряда группы выходов блока, выход пятнадцатого элемента И соединен с вторым входом двадцать третьего элемента И и первым входом второго триггера блока управления, инверсный выход которого соединен с первым входом двадцать четвертого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ блока управления, выход которого соединен с вторым входом второго триггера блока управления, второй вход блока соединен с первым входом - двадцать второго элемента И и вторыми входами четырнадцатого, шестнадцатого, восемнадцатого, двадцать четвертого и двадцатого элементов И, выход которого соединен с выходом седьмого разряда группы блока управления, выход восьмого разряда группы соединен с выходом восемнадцатого элемента И, третий вход которого соединен с третьими входами двадцатого, четырнадцатого, шестнадцатого элементов И, вторым входом двенадцатого элемента И и входом третьего разряда тре тьей группы входов блока, вход четвертого разряда третьей группы-соединен с вторыми входами одиннадцатого, пятнадцатого и семнадцатого элементов И и инверсным входом третьего триггера, вход пятого разряда третьей группы блока соединен с вторыми входами двадцать второго и пятого элементов И, третий

вход которого соединен с третьим входом I двадцать второго элемента И и вторым управляющим входом блока управления, вход седьмого разряда первой группы соединен с вторым входом двадцать четвертого элемента И, вход восьмого разряда первой rpynnbf соединен с вторым входом двадцать первого элемента И, выход которого соединен с пятым входом первого элемента ИЛИ блока управления и первым входом четвертого триггера, инверсный выход которого соединен с вторым входом девятого элемента И, выход которого соединен с вторым входом

второго элемента ИЛИ блока управления и выходом девятого разряда группы блока управления, выход десятого разряда группы соединен с вторым входом десятого элемента И и прямым выходом четвертого триггера, второй вход которого соединен с выходом девятнадцатого элемента И, щестой вход первого элемента ИЛИ блока управления соединен с выходом двенадцатого элемента И, выход четырнадцатого элемента И соединен с вторым входом третьего элемента ИЛИ, второй вход двадцать третьего элемента И соединен с выходом пятнадцатого и девятнадцатого элементов И, выход двадцать третьего элемента И соединен с первым входом пятого триггера, выход которого соединен с выходом признака равенства блока суммирования,

а второй вход пятого триггера соединен с выходом одиннадцатого элемента И, первый вход двадцать пятого элемента И соединен с вторым входом двадцать первого элемента И, второй

вход двадцать пятого элемента И соединен с вторым входом пятнадцатого элемента И, выход двадцать пятого элемента И соединен с выходом шестого разряда группы, первый вход двад- цать шестого элемента И соединен с третьим входом четырнадцатого элемента И, второй вход двадцать шестого элемента И соединен с вторым входом четверто

13130745614

го элемента И блока управления, И соединен с выходом одиннадцатого выход двадцать шестого элемента разряда группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| Процессор для обработки массивов данных | 1985 |

|

SU1293737A1 |

| Устройство для контроля информационного тракта "запоминающее устройство команд-процессор | 1980 |

|

SU1005060A2 |

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| УСТРОЙСТВО СОВМЕСТНОГО КОДИРОВАНИЯ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ | 2012 |

|

RU2497180C1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Устройство для вычисления @ -функций | 1983 |

|

SU1124321A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Генератор псевдослучайных чисел | 1990 |

|

SU1805465A1 |

Изобретение относится к вычислительной технике, а именно к вычислительным системам параллельной обработки данных, может быть использовано при выполнении операций суммирования чисел и определения максимального или минимального числа из массива чисел. Цель изобретения - расширение функциональных возможностей устройства за счет увеличения диапазона представления суммирующих чисел. В устройство, содержащее 2т блоков 1 суммирования, введены 2га блоков коммутации 3, каждый из которых сое- данен магистралью данных 4 между собой и с соответствующим блоком суммирования, каждый из последующих блоков суммирования соединен с входом Занятость и входом Признак равенства предыдущего блока суммирования, 4 ил. S (Л 00 о 4 СЛ 05 Фиг.

5{8х

2(1р}

Z(t8M)

Фиг. г

Ы

J7

36

ш

W

,Й

ч:

з&

45

| Устройство для суммирования чисел | 1984 |

|

SU1183959A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сложения последовательности чисел с плавающей запятой | 1984 |

|

SU1182512A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| I | |||

Авторы

Даты

1987-04-30—Публикация

1985-12-26—Подача