13

ВЫ

- 2

ЩУоп

п

7

11

ТО 12

l±JLJ

л

20

(Л

с

СП

ос о:

4

а

| название | год | авторы | номер документа |

|---|---|---|---|

| Интерполятор | 1981 |

|

SU987634A1 |

| Цифро-аналоговый преобразователь | 1980 |

|

SU949800A1 |

| Устройство для программного управления | 1981 |

|

SU976428A1 |

| Система управления вибростендом | 1985 |

|

SU1305649A1 |

| МНОГОКАНАЛЬНОЕ АКУСТИКО-ЭМИССИОННОЕ УСТРОЙСТВО | 2020 |

|

RU2736171C1 |

| Линейный интерполятор | 1982 |

|

SU1075276A1 |

| МНОГОКАНАЛЬНОЕ АКУСТИКО-ЭМИССИОННОЕ УСТРОЙСТВО | 2019 |

|

RU2726278C1 |

| Стохастический измеритель действующего значения периодического сигнала | 1980 |

|

SU869019A1 |

| Устройство для регулирования расходов компонентов при смешении | 1977 |

|

SU696422A1 |

| Функциональный преобразователь | 1983 |

|

SU1145353A1 |

Изобретение относится к аналоговой вычислительной технике. Цель изобретения - повышение точности и упрощение настройки - достигается за счет переключения устройства в режим автоматической калибровки, при котором корректируются коэффициенты передачи интеграторов с помощью цифроаналоговых преобразователей 3, 4 таким образом, чтобы обнулить остаточные напряжения на выходе запоминающего элемента 2 и интегратора 5. Это соответствует получению идеальной импульсной переходной характеристики интерполятора. 1 ил.

г 15

16

И

- 21

Кали&ро8ка

10

Изобретение относится к аналоговой вычислительной технике.

Цель изобретения - повышение точности и упрощение настройки.

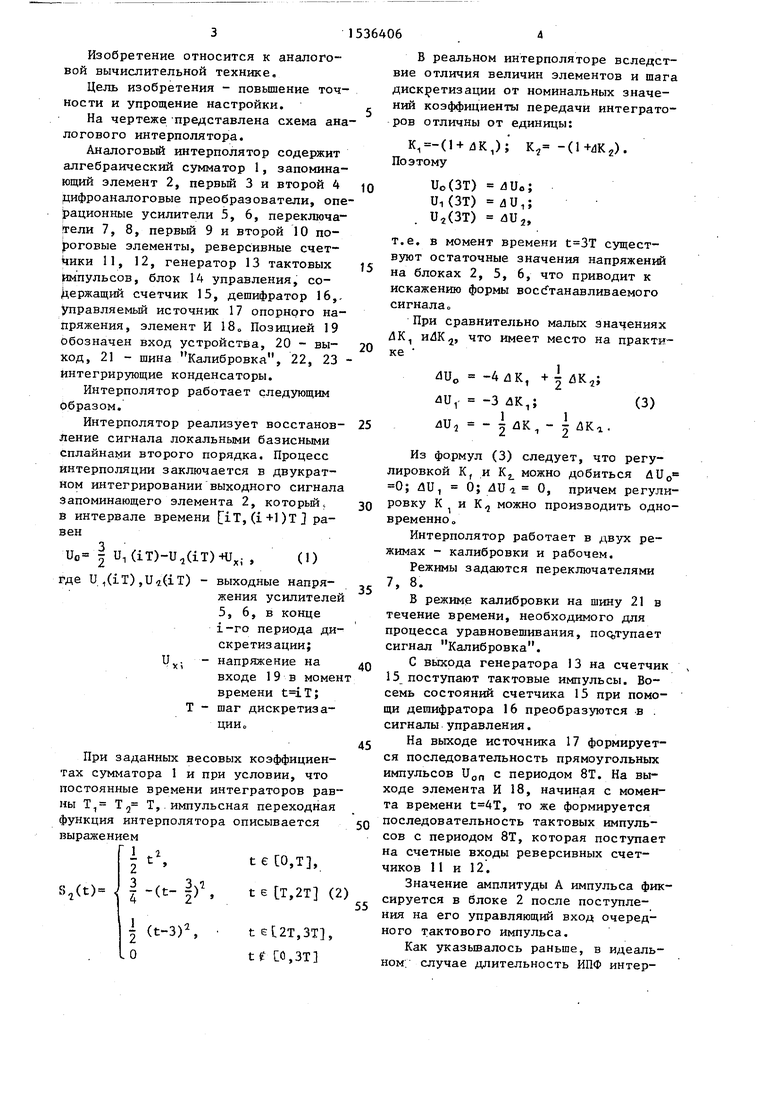

На чертеже представлена схема аналогового интерполятора.

Аналоговый интерполятор содержит алгебраический сумматор 1, запоминающий элемент 2, первый 3 и второй 4 цифроаналоговые преобразователи, операционные усилители 5, 6, переключатели 7, 8, первый 9 и второй 10 пороговые элементы, реверсивные счетчики 11, 12, генератор 13 тактовых импульсов, блок 14 управления, содержащий счетчик 15, дешифратор 16,- управляемый источник 17 опорного напряжения, элемент И 180 Позицией 19 обозначен вход устройства, 20 - вы- ход, 21 - шина Калибровка, 22, 23 интегрирующие конденсаторы.

Интерполятор работает следующим образом.

Интерполятор реализует восстанов- ление сигнала локальными базисными сплайнами второго порядка. Процесс интерполяции заключается в двукратном интегрировании выходного сигнала запоминающего элемента 2, который в интервале времени CiT,(i+l)T равен

U0 | U.CiD-U iD-KJ , (1)

где U ,(iT) ,Ui(iT) - выходные напряжения усилителей 5, 6, в конце 1-го периода дискретизации;

Ux; - напряжение на входе 19 в момен времени Т - шаг дискретизации о

При заданных весовых коэффициентах сумматора 1 и при условии, что постоянные времени интеграторов равны ., Т Q Т, импульсная переходная функция интерполятора описывается выражением

te О,Т,

te T,2T (2)

t eUT,3T, t f СО.ЗТ

0

5 0

0

5

5

0

5

В реальном интерполяторе вследствие отличия величин элементов и шага дискретизации от номинальных значений коэффициенты передачи интеграторов отличны от единицы:

К,-(1+ ДК,); К7 -(1+ЛК2). Поэтому

U0(3T) 4U0;

U,(3T) 4U,;

. U2(3T) лиг,

т.е. в момент времени существуют остаточные значения напряжений на блоках 2, 5, 6, что приводит к искажению формы восстанавливаемого сигналао

При сравнительно малых значениях ЛК, иДК 2, что имеет место на практике

dU0 -4 ЛК, + | ДК,;

аи, -3 ЛКП; (3)

dU7 - 2 К1 - ДК-.

Из формул (3) следует, что регулировкой К, и Kt можно добиться AU0 0; ли, 0; ли i 0, причем регулировку К i и K,j можно производить одновременно.

Интерполятор работает в двух режимах - калибровки и рабочем.

Режимы задаются переключателями 7, 8.

В режиме калибровки на шину 21 в течение времени, необходимого для процесса уравновешивания, поступает сигнал Калибровка.

С выхода генератора 13 на счетчик 15 поступают тактовые импульсы. Восемь состояний счетчика 15 при помощи дешифратора 16 преобразуются в . сигналы управления.

На выходе источника 17 формируется последовательность прямоугольных импульсов Uon с периодом 8Т. На выходе элемента И 18, начиная с момента времени , то же формируется последовательность тактовых импульсов с периодом 8Т, которая поступает на счетные входы реверсивных счетчиков 11 и 12.

Значение амплитуды А импульса фиксируется в блоке 2 после поступления на его управляющий вход очередного тактового импульса.

Как указывалось раньше, в идеальном случае длительность ИПФ интерполятора должна быть равной ЗТ и в момент времени должно выполняться условие

U,

и, и

0.

1 -

Для проверки его выполнения выходные сигналы элемента 2 и усилителя 5 подаются на входы элементов 10 и 9 соответственно, имеющих нулевые пороги срабатывания с,

Если в момент времени U0 0, то счетчик 12 уменьшает свое состояние на единицу, а при U1 0 счетчик Il увеличивает свое состояние на единицу,, При этом коэффициенты передачи блоков изменяются так, что отклонения контролируемых напряжений уменьшаются.

После прихода следующего импульса из последовательности процесс калибровки повторяется.

По истечении времени, необходимого для обнуления напряжений, сигнал Калибровка снимается, переключа- тели 7, 8 переходят в положение, соответствующее рабочему режиму. В этом режиме счетчики II, 12 заблокированы и сохраняют свое предыдущее состояние На вход 19 поступает последовательность дискретных значений сигнала, а с выхода 20 снимается аналоговый восстановленный сигнал

Формула изобрет.ения

Аналоговый интерполятор, содержащий алгебраический сумматор, выход которого соединен с информационным входом запоминающего элемента, первый и второй операционные усилители с интегрирующим конденсатором в цепи обратной связи, выходы операционных усилителей соединены с первым и вторым входами алгебраического сумматора, и генератор тактовых импульсов, выход которого соединен с управляющим входом запоминающего элемента, отличающийся тем, что, с целью повышения точности и упрощения настройки, в него введены первый и второй цифроаналоговые пре5

5

г.

0

0

5

0

5

0

образователи, первый и второй ревер-. сивные счетчики, первый и второй пороговые элементы, первый и второй переключатели и блок управления, содержащий счетчик, дешифратор, управляемый источник опорного напряжения и элемент И, при этом третий вход алгебраического сумматора соединен через первый переключатель с входом аналогового интерполятора и с выходом управляемого источника опорного напряжения блока управления, зы- ход запоминающего элемента соединен с входом первого порогового элемента и с аналоговым входом первого цифро- аналогового преобразователя, выход которого соединен с входом первого операционного усилителя, выход которого соединен с входом второго порогового элемента и с аналоговым входом второго цифроаналогового преобразователя, выход которого соединен с входом второго операционного усилителя, выход которого и шина нулевого потенциала соединечы с выходом устройства через второй переключатель, выход генератора тактовых импульсов соединен с входом счетчика и с первым входом элемента И блока управления, выход счетчика соединен с входом дешифратора, первый выход которого соединен с входом управляемого источника опорного напряжения, а второй выход - с вторым входом элемента И, управляющие входы первого и второго переключателей и третий вход элемента И соединены с шиной Калибровка, выход элемента И соединен со счетным входом первого и второго реверсивных счетчиков, знаковый вход первого реверсивного счетчика соединен с выходом второго порогового элемента, а выход - с кодовым входом первого цифроаналогового преобразователя, выход первого порогового элемента соединен со знаковым входом второго реверсивного счетчика, выход которого соединен с кодовым входом второго цифроаналогового преоО- разователя.

| Полиномиальный интерполятор | 1983 |

|

SU1239732A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для регистрации сигналов | 1986 |

|

SU1323856A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-01-15—Публикация

1988-04-26—Подача