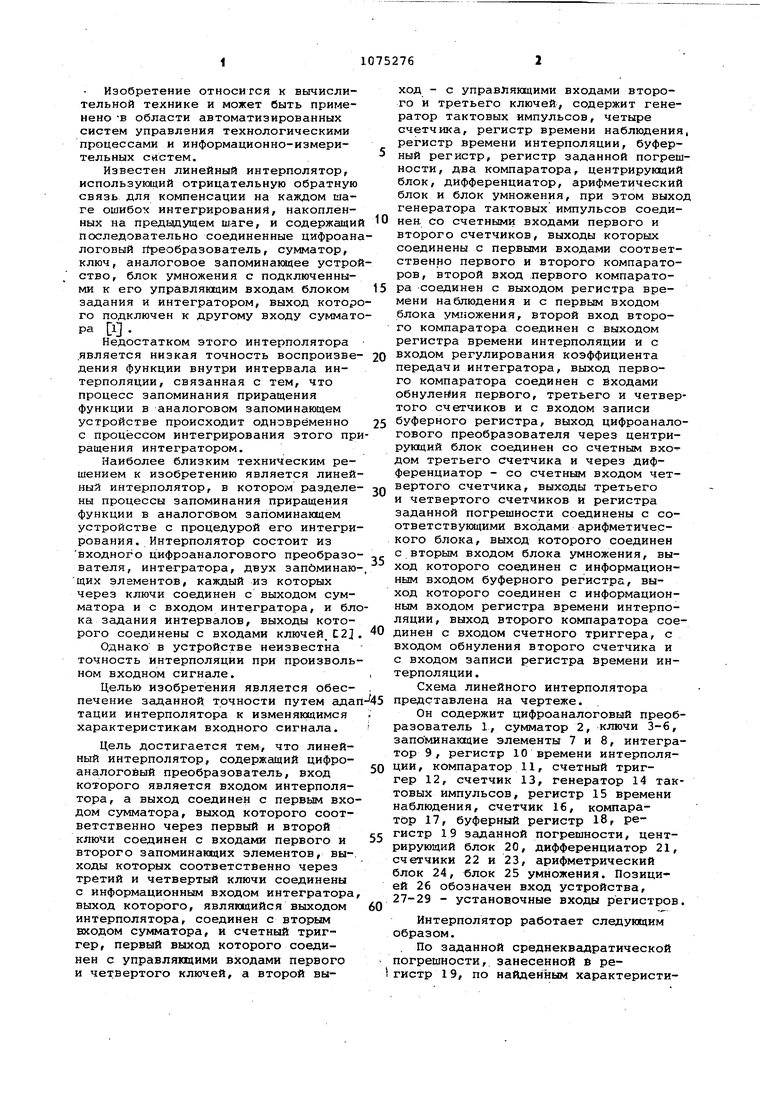

Изобретение относится к вычислительной технике и может быть прш енено -в области автоматизированных систем управления технологическими процессами и информационно-измерительных Систем. Известен линейный интерполятор, использующий отрицательную обратную связь для компенсации на каждом шаге ошибок интегрирования, накопленных на предьщущем шаге, и содержшци последовательно соединенные цифроан логовый гфеобразователь, сумматор, ключ, аналоговое запоминакадее устро ство, блок умножения с подключенными к его управляющим входам блоком задания и интегратором, выход котор го подключен к другому входу суммат ра 1 . Недостатком этого интерполятора является низкая точность воспроизве дения функции внутри интервала интерполяции, связанная с тем, что процесс запоминания приращения функции в аналоговом запоминающем устройстве происходит одновременно с процессом интегрирования этого пр ращения интегратором. Наиболее близким техническим решением к изобретению является линей ный интерполятор, в котором разделе ны процессы запоминания приращения функции в аналогс вом запоминающем устройстве с процедурой его интегри рования. Интерполятор состоит из входного цифроаналогового преобразо вателя, интегратора, двух запбминаю щих элементов, каждый из которых через ключи соединен с выходом сумматора и с входом интегратора, и бл ка задания интервалов, выходы которого соединены с входами ключей C2J Однако в устройстве неизвестна точность интерполяции при произволь ном входном сигнале. Целью изобретения является обеспечение заданной точности путем ада тации интерполятора к изменяющимся характеристикам входного сигнала. Цель достигается тем, что линейный интерполятор, содержащий цифроаналоговый преобразователь, вход которого является входом интерполятора, а выход соединен с первым вхо дом сумматора, выход которого соответственно через первый и второй ключи соединен с входами первого и второго запоминающих элементов, выходы которых соответственно через третий и четвертый ключи соединены с Информационным входом интегратора выход которого, являющийся выходом интерполятора, соединен с вторым входом сумматора, и счетный триггер, первый выход которого соединен с управляющими входами первого и четвертого ключей, а второй выход - с управляющими входами второго и третьего ключей, содержит генератор тактовых импульсов, четыре счетчика, регистр времени наблюдения, регистр времени интерполяции, буферный регистр, регистр заданной погрешности, два компаратора, центрирующий блок, дифференциатор, арифметический блок и блок умножения, при этом выход генератора тактовых импульсов соединен со счетными входами первого и второго счетчиков, выходы которых соединены с первыми входами соответственно первого и второго компараторов, второй вход .первого компаратора соединен с выходом регистра времени наблюдения и с первым входом блока умножения, второй вход второго компаратора соединен с выходом регистра времени интерполяции и с входом регулирования коэффициента передачи интегратора, выход первого компаратора соединен с входами Обнулен ия первого, третьего и четвертого счетчиков и с входом записи буферного регистра, выход цифроаналогового преобразователя через центриругаций блок соединен со счетным входом третьего счетчика и через дифференциатор - со счетнЕлм входом четвертого счетчика, выходы третьего и четвертого счетчиков и регистра заданной погрешности соединены с соответствующими входами арифметического блока, выход которого соединен с вторым входом блока умножения, выход которого соединен с информационным входом буферного регистра, выход которого соединен с информационным входом регистра времени интерполяции, выход второго компаратора соединен с входом счетного триггера, с входом обнуления второго счетчика и с входом записи регистра времени интерполяции . Схема линейного интерполятора представлена на чертеже. Он содержит цифроаналоговый преобразователь 1, сумматор 2, ключи 3-6, запоминакщие элементы 7 и 8, интегратор 9, регистр 10 времени интерполяции, компаратор 11, счетный триггер 12, счетчик 13, генератор 14 тактовых импульсов, регистр 15 времени наблюдения, счетчик 16, компаратор 17, буферный регистр 18, регистр 19 заданной погрешности, центрирующий блок 20, дифференциатор 21, счетчики 22 и 23, арифметрический блок 24, блок 25 умножения. Позицией 26 обозначен вход устройства, 27-29 - установочные входы регистров. Интерполятор работает следующим образом. . По заданной среднеквадратической погрешности, занесенной и регистр 19, по найденным характеристикам сигнала (число нулей интерполируемой функции и ее производной) через время наблюдения Тц рассчитьшается время интерполяции Т, которое заносится в регистр 10..

В регистр 10 вводится начальное значение времени интерполяции Т, в регистр 15 - значение времени набгаодения Тц.

Существует два независи1 х рабочих цикла, один с периодом Тц - для получения времени интерполяции Т; второй с периодом Т - для обработки очередного значения интерполируемой функции, при этом Т«Тц.

Последний цикл начинается с того, что в интеграторе 9 устанавливается значение постоянной времени интегрирования, равное времени интерполяции Т. На вход цифроаналогового преобразователя 1 поступают в цифровом коде значения интерполируемой функции.

Ключи 3-6 замыкаются так, что, например, в каждый четный интервал времени замкнуты ключи 3 и 6, а в каждый нечетный - ключи 4 и 5. С выхода цифроаналогового преобразователя 1 ступенчатое напряжение поступает на первый вход сумматора 2, по второму входу которого подается напряжение обратной связи с выхода интегратора 9. Напряжение с выхода сумматора 2 в четные интервалы вреьени .замкнутый ключ 3 поступает на вход запоминаюа1его элемента 7 и в течение этого интервала времени запоминается в нем с обратным знаком. В этот же интервал времени интегратор 9 интегрирует напряжение, поступающее на его вход через замкнутый ключ 6с выхода запоминающего элемента 8, которое запоминается в нем в четные интервалы -времени, К моменту окончания четного интервала времени в запоминающем элементе 7 содержится величина напряжения, равная приращению интерполируемой функции. Затем происходит размыкание ключей 3, 6 и замыкание ключей 4 и 5.

В нечетные интервалы времени напряжение с выхода сумматора 2 через ключ 4 поступает на вход запоминающего элемента 8, и в течение этого интервала времени интегратор 9 интегрирует напряжение, поступающее на его вход через замкнутый ключ 5 с выхода элемента 7. С выхода интегратора 9 снимаются значения интерполирующей функции в аналоговой форме.

Работой-ключей 3-5 управляет триггер 12. Компаратор 11 сравнивает значение содержимого регистра 10 и текущее значение счетчика 13, и

в момент их совпадения вырабатывает управляющий импульс, перебрасывающий триггер-12 в новое положение. В результате обеспечивается описанная выше последовательность размыкания ключей.

Рабочий цикл по расчету времени интерполяции начинается с того, что с выхода цифроаналогового преобразователя 1 значения функции поступают На центрирующий блок 20. С выхода центрирующего блока 20 значения интерполируемой функции подаются на счетчик 23 и через дифференциатор 21 на счетчик 22, на которых производится отсчет числа пересечений функции и ее производной своего среднего уровня.

Компаратор 17 сравнивает значение регистра 15 времени наблюдения и текущее значение счетчика 16 и в моент их совпсшения вырабатывает управляющий импульс, в результате содержимое счетчиков 22 и 23 переносится в арифметический блок 24, и счетчики сбрасываются в нулевое состояние. В арифметическом блоке 24 вычисляется квадратный корень отношения значения погрешности интерполяции, содержащейся в регистре 19, и произведения значений счетчиков 22 и 23. С выхода арифметического блока 24 полученное значение поступает на вход блока 25 умножения, с выхода которого рассчитанное значение времени интерполяции Т заносится в буферный регистр 18. По разрешающему сигналу компаратора 11 оно переписывается в регистр 10.

В результате работы устройства на его выходе формируется кусочнолинейное напряжение, которое интерполирует значения воспроизводимой функции времени с заданной точностью.

Арифметический блок 24 и блок 25 умножения могут быть реализованы как икропрограммные автоматы или с .использованием существующих программируемых калькуляторов.

Отличительной особенностью устройства является то, что оно производит интерполяцию с гарантируемой точностью при минимуме априорной Информации об интерполируемой функции путем использования характеристик нулей функции и ее производной. Это позволяет использовать устройство для работы в реальном масштабе времени в информационно-измерительных системах и автоматизированных системах управления технологическими процессами. Это определяет технико-экономический эффект от использования изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Нелинейный интерполятор | 1979 |

|

SU851425A1 |

| Линейный интерполятор | 1978 |

|

SU698012A1 |

| Интерполятор | 1978 |

|

SU765821A1 |

| Интерполятор | 1981 |

|

SU987634A1 |

| Функциональный преобразователь | 1983 |

|

SU1145353A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Устройство для интерполяции амплитудно-импульсных сигналов | 1980 |

|

SU886015A1 |

| Линейный интерполятор | 1989 |

|

SU1686408A1 |

| Интерполятор | 1978 |

|

SU686039A1 |

| Цифровой квадратичный интерполятор | 1985 |

|

SU1317452A1 |

ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР, содержащий цифроаналоговый преобразователь , вход которого является входом интерполятора, а выход соединен с первым входом сумматора, выход которого соответственно через первый и второй ключи соединен с входами первого и второго запоминающих элементов, выходы которых соответственно через третий и четвертый ключи соединены с информационным входом интегратора, выход которого, являющийся выходом интерполятора, соединен с вторым входом сумматора, и счетный триггер, первый выход которого соединен с управляющими входами первого и четвертого ключей, а второй выход - с управляющими входами второго и третьего ключей, отличающийся тем, что, с целью обеспечения заданной точности путем адаптации интерполятора к изменяющимся характеристикам входного сигнала, интерполятор содержит генератор тактовых импульсов, четыре счетчика, регистр времени наблюдения, регистр времени интерполяции, буферный регистр, регистр заданной погрешности, два компаратора, центрирующий блок, дифференциатор, арифметический блок и блок умножения, при этом выход генератора тактовых импульсов соединен со счетными входами первого и.второго счетчиков, выходы которых соединены с первыми входами соответственно первого и второго компараторов, второй вход первого компаратора соединен с выходом регистра времени наблюдения и с первым входом блока умножения, второй вход второго компаратора соединен с выходом регистра времени интерполяции и с входом регулирования коэффициента передачи интегратора, выход первого компаратора (Л соединен с входами обнуления первого третьего и четвертого счетчиков и с входом записи буферного регистра, выход цифроаналогового преобразователя через центрирующий блок соеди- 5 нен со счетным входом третьего счетчика и через дифференциатор - со счетным входом четвертого счетчика, выходы третьего и четвертого, счетчиков и регистра заданной погрешности соединены с соответствующими входам арифметического блока, выход которого соединен с вторыг входом блока умножения, выход которого соединен с информационным входом буферного регистра, выход которого соединен с информационным входом регистра времени интерполядии, выход второго компаратора соединен с входом счетного триггера, с входом обнуления второго счетчика и с входом записи регистра времени интерполяции.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Линейный интерполятор | 1973 |

|

SU628500A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Линейный интерполятор | 1978 |

|

SU698012A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-02-23—Публикация

1982-12-21—Подача