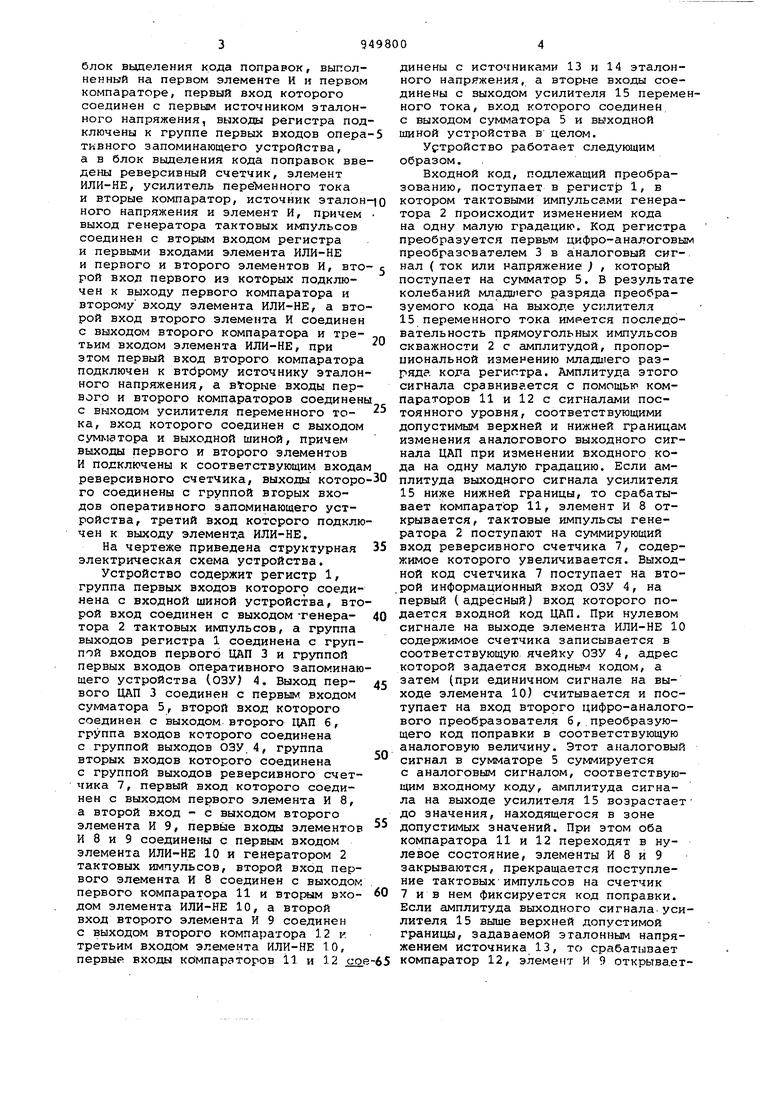

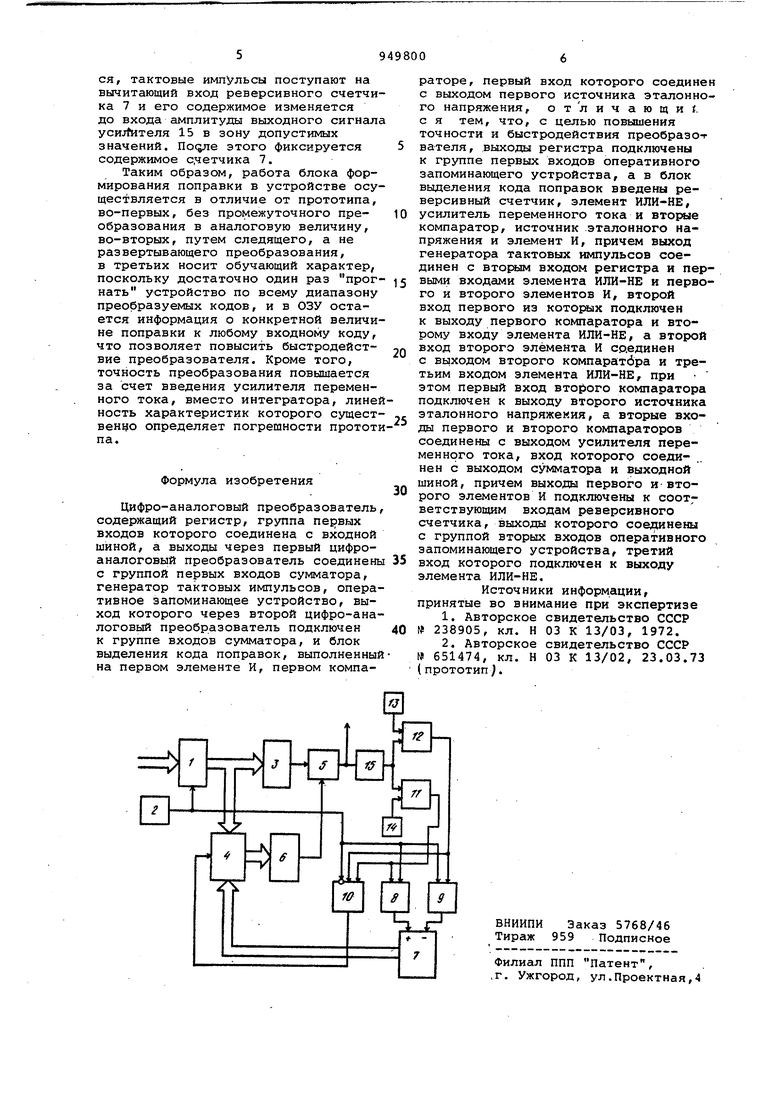

Изобретение относится к информационно-измерительной технике и может найти применение при преобразовании цифровых сигналов в непрерывные, пригодные для работы с аналоговыми устройствами и приборами автоматических систем управления и контроля i Известен цифро-аналоговый преобразователь СЦАП), имеющий высокую точность преобразования в температурном диапазоне, в котором базы транзисто-ров делителей тока подключены через переключатели,управляемые сигналами преобразуемого кода к источникам смещения, соединенным с вторым и третьим генераторами тока, при этом выход одного из источников смещения подключен к земляной шине, а другого - чере резистор - к четвертому генератору тока, выход которого подключен к входам усилителя и.пятого генератора тока Г1. Известен также преобразователь кода в аналог, содержащий регистр числа, соединенный через ключевые уст ройства с входом сумматора, запоминающее устройство (ЗУ), подключенное через эталонные ключевые устройства к другому входу сумматора, устройство управления, соединенное с регистром числа, ЗУ и устройством выделения кода поправок, которое содержит генератор импульсов, интегрируквдий операционный усилитель, компаратор, триггер и ключ, причем вход компаратора соединен с источником эталонного напряжения, а выход кс шаратора подключен к установочному входу триггера 23. Недостатками описанных устройств являются сложность конструкции и низт кое быстродействие, а также необходимость использования большого числа прецизионных резисторов для достижения приемлемой точности. Цель изобретения - повышение точности и быстродействия цифро-аналогового преобразования. Поставленная цель достигается тем, что в цифро-аналоговом преобразователе, содержащем регистр, группа первых входов которого соединена с входной шиной, а выход через первый цифро-аналоговый преобразователь соединены с группой первых входов сумматора, генератор тактовых импульсов, оперативное запоминающее устройство, выход которого через второй цифроаналоговый преобразователь подключен к группе вторых входов сумматора, и блок выделения кода поправок, выполненный на первом элементе И и первом компараторе, первый вход которого соединен с первым источником эталонного напряжения, выходы регистра под ключены к группе первых входов опера тивного запоминающего устройства, а в блок выделения кода поправок вве дены реверсивный счетчик, элемент ИЛИ-НЕ, усилитель пере1иенного тока и вторые компаратор, источник эталон ного напряжения и элемент И, причем выход генератора тактовых импульсов соединен с вторым входом регистра и первыми входами элемента ИЛИ-НЕ и первого и второго элементов И, вто рой вход первого из которых подключен к выходу первого компаратора и второму входу элемента ИЛИ-НЕ, а вто рой вход второго элемента И соединен с выходом второго компаратора и третьим входом элемента ИЛИ-НЕ, при этом первый вход второго компаратора подключен к втброму источнику эталон ного напряжения, а вторые входы первого и второго компараторов соединен с выходом усилителя переменного тока, вход которого соединен с выходом сумматора и выходной шиной, причем выходы первого и второго элементов И подключены к соответствующим входа реверсивного счетчика, выходы которо го соединены с группой вторых входов оперативного запоминающего устройства, третий вход которого подклю чен к выходу элемента ИЛИ-НЕ. На чертеже приведена структурная электрическая схема устройства. Устройство содержит регистр 1, группа первых входов которого соединена с входной шиной устройства, вто рой вход соединен с выходом тенератора 2 тактовых импульсов, а группа выходов регистра 1 соединена с группой входов первого ЦАП 3 и группой первых входов оперативного запоминаю щего устройства (ОЗУ) 4. Выход первого ЦАП 3 соединен с первым входом сумматора 5, второй вход которого соединен с выходом второго б, группа входов которого соединена с группой выходов ОЗУ.4, группа вторых входов которого соединена с группой выходов реверсивного счетчика 7, первый вход которого соединен с выходом первого элемента И 8, а второй вход - с выходом второго элемента И 9, первые входы элементов И 8 и 9 соединены с первым входом элемента ИЛИ-НЕ 10 и генератором 2 тактовых импульсов, второй вход первого элемента И 8 соединен с выходом первого компаратора 11 и вторялм входом элемента ИЛИ-НЕ 10, а второй вход второго элемента И 9 соединен с выходом второго компаратора 12 и. третьим входом элемента ИЛИ-НЕ 10, первые входы компараторов 11 и 12 co динены с источниками 13 и 14 эталонного напряжения, а вторые входы соединены с выходом усилителя 15 переменного тока, вход которого соединен с выходом сумматора 5 и выходной шиной устройства в целом. Устройство работает следующим образом. Входной код, подлежащий преобразованию, поступает в регистр 1, в котором тактовыми импульсами генератора 2 происходит изменением кода на одну малую градацию. Код регистра преобразуется первым цифро-аналоговым преобразователем 3 в аналоговый сигнал ( ток или напряжение ) , который поступает на сумматор 5. В результате колебаний младшего разряда преобразуемого кода на выходе усилителя 15 переменного тока имеется последовательность прямоугольных импульсов скважности 2 с амплитудой, пропорциональной изменению младшего разряде, кода регистра. Амплитуда этого сигнала сравнивается с помощью компараторов 11 и 12 с сигналами постоянного уровня, соответствующими допустимым верхней и нижней границам изменения аналогового выходного сигнала ЦАП при изменении входного кода на одну малую градацию. Если амплитуда выходного сигнала усилителя 15 ниже нижней границы, то срабатывает компаратЬр 11, элемент И 8 открывается, тактовые импульсы генератора 2 поступают на суммирующий вход реверсивного счетчика 7, содержимое которого увеличивается. Выходной код счетчика 7 поступает на второй информационный вход ОЗУ 4, на первый (адресный) вход которого подается входной код ЦАП. При нулевом сигнале на выходе элемента ИЛИ-НЕ 10 содержимое счетчика записывается в соответствующую ячейку ОЗУ 4, адрес которой задается входны / кодом, а затем (при единичном сигнале на выходе элемента 10) считывается и поступает на вход второго цифро-аналогового преобразователя б, преобразующего код поправки в соответствующую аналоговую величину. Этот аналоговый сигнал в сумматоре 5 суммируется с аналоговым сигналом, соответствующим входному коду, амплитуда сигнала на выходе усилителя 15 возрастаетдо значения, находящегося в зоне допустимых значений. При этом оба компаратора 11 и 12 переходят в нулевое состояние, элементы И 8 и 9 закрываются, прекращается поступление тактовых-импульсов на счетчик 7 ив нем фиксируется код поправки. Если амплитуда выходного сигнала-усилителя 15 выше верхней допустимой границы, задаваемой эталонным напряжением источника 13, то срабатывает компаратор 12, элемент И 9 открывается, тактовые импульсы поступают на вычитающий вход реверсивного счетчика 7 и его содержимое изменяется до входа амплитуды выходного сигнала уси7 ителя 15 в зону допустимых значений. Посыле этого фиксируется содержимое с.четчика 7. Таким образом, работа блока формирования поправки в устройстве осуществляется в отличие от прототипа, во-первых, без промежуточного преобразования в аналоговую величину, во-вторых, путем следящего, а не развертывающего преобразования, в третьих носит обучающий характер, поскольку достаточно один раз прогнать устройство по всему диапазону преобразуемых кодов, и в ОЗУ остается информация о конкретной величине поправки к любому входному коду, что позволяет повысить быстродействие преобразователя. Кроме того, точность преобразования повышается за счет введения усилителя переменного тока, вместо интегратора, лине ность характеристик которого сущест венцо определяет погрешности протот па. Формула изобретения Цифро-аналоговый преобразователь содержащий регистр, группа пеЕзвых входов которого соединена с входной шиной, а выходы через первый цифроаналоговый преобразователь соединен с группой первых входов сумматора, генератор тактовых импульсов, опера тивное запоминающее устройство, выход которого через второй цифро-ана логовый преобразователь подключен к группе входов сумматора, и блок выделения кода поправок, выполненны на первом элементе И, первом компараторе, первый вход которого соединен с выходом первого источника эталонного напряжения, отличающий, с я тем, что, с целью повышения точности и быстродействия преобразо-г вателя, выходы регистра подключены к группе первых входов оперативного запоминающего устройства, а в блок выделения кода поправок введены реверсивный счетчик, элемент ИЛИ-НЕ, усилитель переменного тока и вторые компаратор/ источник эталонного напряжения и элемент И, причем выход генератора тактовых импульсов соединен с вторим входом регистра и первыми входами элемента ИЛИ-НЕ и первого и второго элементов И, второй вход первого из которых подключен к выходу первого компаратора и второму входу элемента ИЛИ-НЕ, а второй вход второго элемента И ср.единен с выходом второго компаратдра и третьим входом элемента ИЛИ-НЕ, при этом первый вход второго компаратора подключен к выходу второго источника эталонного напряжения, а вторые входы первого и второго компараторов соединены с выходом усилителя переменного тока, вход которого соеди- .. нен с выходом сумматора и выходной шиной, причем выходы первого и-второго элементов И подключены к соответствующим входам реверсивного счетчика, выходы которого coe : инeны с группой вторых входов оперативного запоминающего устройства, третий вход которого подключен к выходу элемента ИЛИ-НЕ. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 238905, кл. Н 03 К 13/03, 1972. 2.Авторское свидетельство СССР № 651474, кл. Н 03 К 13/02, 23.03.73 (прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1287290A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Устройство для управления @ - фазным шаговым двигателем | 1988 |

|

SU1647841A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Аналого-цифровой преобразователь с коррекцией погрешности | 1988 |

|

SU1688473A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Многоканальная электроразведочная станция | 1980 |

|

SU934414A1 |

| Калибратор периодических сигналов инфразвуковых частот | 1987 |

|

SU1449926A1 |

Авторы

Даты

1982-08-07—Публикация

1980-04-25—Подача