|/- JLHJJE

Изибретение относится к разделу технической физики, а именно к области сбора и перед :чи сигналив, и может быть использовано при сборе и передаче результатов измерений.

Цель изобретения - повышение информативно стн сокращения длины цифровой комбинации кадра в момент смены режимов формирования кадра.

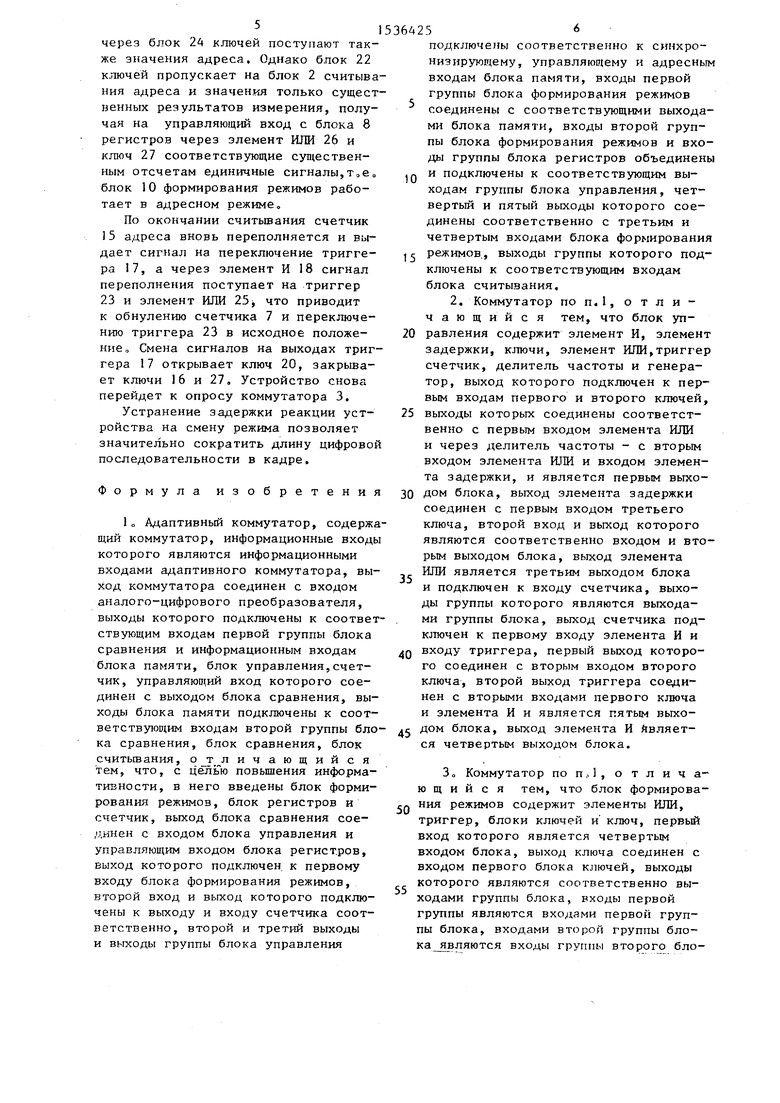

На чертеже приведена структурная схема адаптивного коммутатора.

Адаптивный коммутатор содержит информационные входы 1, блок 2 считывания, коммутатор 3, аналого-цифровой преобразователь 4, блок 5 памяти блок 6 сравнения, счетчик 7, блок 8 регистров, блок 9 управления, блок 10 формировании режимов, информационные выходы 11 блока 10.

Блок 9 управления содержит элемен 12 задержки, первый ключ 13, элемент ИЛИ l i, счетчик 15, второй ключ 16, триггер 17, элемент И 18, делитель

19частоты, третий ключ 20 и генератор 21 ,

Блок 10 формирования режимов содержит первый блок 22 ключе, тригге 23, второй блок 24 ключей, элементы ИЛИ 25 и 26, ключ 27.

В исходном состоянии триггеры 17 и 23 держат единичные разрешающие сигналы на управляющих входах соответственно ключа 20 и блока 2 ключей, ключи 13, 16, 27 и блок 22 ключей закрыты, счетчики 7 и 15 обнулены с

В блоке 9 управлении импульгы от задающего генератора 21 через ключ

20и делитель 19 частоты подаются и коммутатор 3 и через элемент ИЛИ 1А поступают также в счетчик 15 адреса и на управляющий считыванием вход блока 5. Сигналы с информационных входов 1 через коммутатор 3 и аналого-цифровой преобразователь (ЛЦП) А в параллельном коде поступают в блик 6, в который из блока 5 плмчли подаются предыдущие отсчеты, выбираемые по адресам, получаемым из счегчика 15 адреса. Блок 6 сравнения определяет разность текущего и предыдущего значений и срапнивает ее с порогом срабатывании. В случае превышения этого порога с блока 6 сравнения па ключ 13 поступает разрешающий сигнал, а в счетчик 7 и блок Я регистров по указанному адресу записывается единиц 1. При этом единичный сиг

5

0

0

5

0

5

0

5

нал с элемент л 12 ,ш р- ь и Ч Р ключ 13 поступает н,ч ynp.ni пичшы ,- писью вход блока 5 памяти, в котором на месте предыдущего отсчета записывается текущее значение результата измерения. Если же разность оказывается меньше или равна порогу срабатывания, то ключ 13 остается закрытым, запись в счетчик 7 и блок 5 памяти не производится, а в блоке 8 регистров по указанному адресу заносится ноль. Счетчик 7 подсчитывает число N избыточных отсчетов, поступивших за время одного цикла опроса коммутатораь При превышении М-гра- ннчного числа Nrp, рассчитанного из условия равенства цифровой последовательности при адресном и безадресном режимах, счетчик 7 переполняется, на триггер 23 поступает сигнал переполнения, перебрасывающий единичный сигнал триггера 23 на вход элемента ИЛИ 26 и через элемент ИЛИ 25 на вход сброса в ноль счетчика 7, т.е. блок 10 переходит в готовность к безадресному формированию кадра. По окончании опроса комму гатора } счетчик 15 адреса переполняется и обнуляется, сигнал переполнении подается на вход элемента И 18, который его не пропускает из-за отсутствия единичного сигнала на втором своем входе, кроме того, сигнал переполнения счетчика 15 адреса переключает триггер 17, который закрывает ключ 20, открывает ключи 16 и 27,подает единичный сигнал на второй вход элемента И 13 Теперь импульсы от задающего генератора 21 через ключ 16

и элемент ИЛИ I 1 поступают в счетчик 15 адреса и на управляющий считыванием вход блока 5 памяти, который рыдает псе отсчеты на блок 22 ключей. Так как на управляющий вход блока 22 ключей от триггера 23 через элемент ИЛИ 26 и ключ 27 подастся единичный разрешающий сигнал,все отсчеты из блока 5 памяти выдаются в блок 2 считывания без адресов, где они преобразуются в последовательный код и поступают в канал связи.

Если счетчик 7 за время цикла опроса коммутатора 3 не переполняется, триггер 23 не переключается и блок 10 формирования режимов остается в ГОТОБНО -. ги к адресному формированию кадра. Тогда при считывании отсчетов из блока 5 памяти на блок 22 ключей

через блок 24 ключей поступают также значения адреса. Однако бпок 22 ключей пропускает на блок 2 считывания адреса и значения только сущест- ненных результатов измерения, получая на управляющий вход с блека 8 регистров через элемент ИЛИ 26 и ключ 27 соответствующие существенным отсчетам единичные сигналы, т „е,, блок 10 формирования режимов работает в адресном режиме„

По окончании считывания счетчик 15 адреса вновь переполняется и выдает сигнал на переключение тригге- P.I 17, а через элемент И 18 сигнал переполнения поступает на триггер 23 и элемент ИЛИ 25, что приводит к обнулению счетчика 7 и переключению триггера 23 в исходное положение. Смена сигналов на выходах триггера 17 открывает ключ 20, закрывает ключи 16 и 27. Устройство снова перейдет к опросу коммутатора 3.

Устранение задержки реакции устройства на смену режима позволяет значительно сократить длину цифровой последовательности в кадре.

Формула изобретения

1„ Адаптивный коммутатор, содержащий коммутатор, информационные входы которого являются информационными входами адаптивного коммутатора, выход коммутатора соединен с входом аналого-цифрового преобразователя, выходы которого подключены к соответствующим входам первой группы блока сравнения и информационным входам блока памяти, блок управления,счетчик, управляющий вход которого соединен с выходом блока сравнения, выходы блока памяти подключены к соответствующим входам второй группы блока сравнения, бпок сравнения, блок

считывания, о тличающийся тем, что, с целью повышения информативности, в него введены блок формирования режимов, блок регистров и г етчик, выход блока сравнения сое- , лнен с входом блока управления и управляющим входом блока регистров, выход которого подключен к первому входу блока формирования режимов, нтоport вход и выход которого подключены к выходу и входу счетчика соот- Ботг твенно, второй и третий выходы и вмходы группы блока управления

0

5

подключены соответственно к синхронизирующему, управляющему и адресным входам блока памяти, входы первой группы блока формирования режимов соединены с соответствующими выходами блока памяти, входы второй группы блока формирования режимов и входы группы блока регистров объединены и подключены к соответствующим выходам группы блока управления, четвертый и пятый выходы которого соединены соответственно с третьим и четвертым входами блока формирования режимов, выходы группы которого подключены к соответствующим входам блока считывания,

2. Коммутатор по п.I, о т л и - чающийся тем, что блок уп- 0 равления содержит элемент И, элемент задержки, ключи, элемент ИЛИ,триггер счетчик, делитель частоты и генератор, выход которого подключен к первым входам первого и второго ключей, 5 выходы которых соединены соответственно с первым входом элемента ИЛИ и через делитель частоты - с вторым входом элемента ИЛИ и входом элемента задержки, и является первым вьгхо- 0 Д°м блока, выход элемента задержки соединен с первым входом третьего ключа, второй вход и выход которого являются соответственно входом и вторым выходом блока, выход элемента ИЛИ является третьим выходом блока и подключен к входу счетчика, выходы группы которого являются выходами группы блока, выход счетчика подключен к первому входу элемента И и входу триггера, первый выход которого соединен с вторым входом второго ключа, второй выход триггера соединен с вторыми входами первого ключа и элемента И и является пятым выхое дом блока, выход элемента И йвляет- ся четвертым выходом блока.

5

0

30 Коммутатор по п 1, отличающийся тем, что блок формирования режимов содержит элементы ИЛИ, триггер, блоки КЛЮЧРЙ и ключ, первый вход которого является четвертым входом блока, выход ключа соединен с входом первого блока ключей, выходы которого являются соогпетственно выходами группы блока, входы первой группы являются входами первой группы блока, входами второй группы блока являются входы группы второго бло

715364258

ка ключей, выходы которого подключе-дом триггера и является третьим вхоны к входам второй группы первогодом блока, выход первого элемента

блока ключей, первый выход триггераИЛИ является выходом блока, второй

соединен с входом второго блока клю-вход второго элемента ИЛИ н триггера

чей, второй выход триггера подключенявляются соответственно первым и вток первым входам первого и второгорым входами блока, выход второго элеэлементов ИЛИ, второй вход первогомента ИЛИ соединен с вторым входом

элемента ИЛИ объединен с первым вхо-ключа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1989 |

|

SU1649529A1 |

| Многоканальное устройство для ввода информации | 1984 |

|

SU1265783A1 |

| Устройство для считывания графической информации | 1989 |

|

SU1621062A1 |

| Устройство для считывания изображений | 1984 |

|

SU1179394A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1986 |

|

SU1376087A1 |

| Устройство для передачи информации | 1981 |

|

SU1012311A1 |

| Устройство для регистрации команд в резервированной системе управления | 1989 |

|

SU1633284A1 |

| Цифровой Фурье-преобразователь | 1982 |

|

SU1043663A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| УСТРОЙСТВО АВТОВЫБОРА ДИСКРЕТНОГО КАНАЛА | 2011 |

|

RU2488222C1 |

Изобретение может быть использовано при сборе и передаче результатов измерений. Целью изобретения является повышение информативности. Адаптивный коммутатор содержит информационные входы 1, блок управления 9, блок считывания 2, счетчик 7, коммутатор 3, аналого-цифровой преобразователь 4, блок 5 памяти, блок 6 сравнения, блок 10 формирования режимов, блок 8 регистров. Цель достигается за счет устранения задержки реакции устройства при переходе к новому режиму формирования кадра. 2 з.п. ф-лы, 1 ил.

| Ольховский Ю.Б | |||

| и др | |||

| Сжатие данных при телеизмерениях | |||

| М.: Советское радио, 1971, с.246 | |||

| Авдеев В.Я., Антонюк Е,М„ Адаптивные телеизмерительные системы | |||

| Л.: Энергоиздат, 1981, с.85, рис„3- 19. |

Авторы

Даты

1990-01-15—Публикация

1988-04-11—Подача