сл

Од

а

о

00

.f

Изобретение относится к контрольно-измерительной технике и может быть использовано для контроля и диагностики многоразрядных цифровых узлов радиоэлектронной аппаратуры.

Цель изобретения - расширение функциональных возможностей путем (подстройки частоты и изменения задержки считывания при контроле.

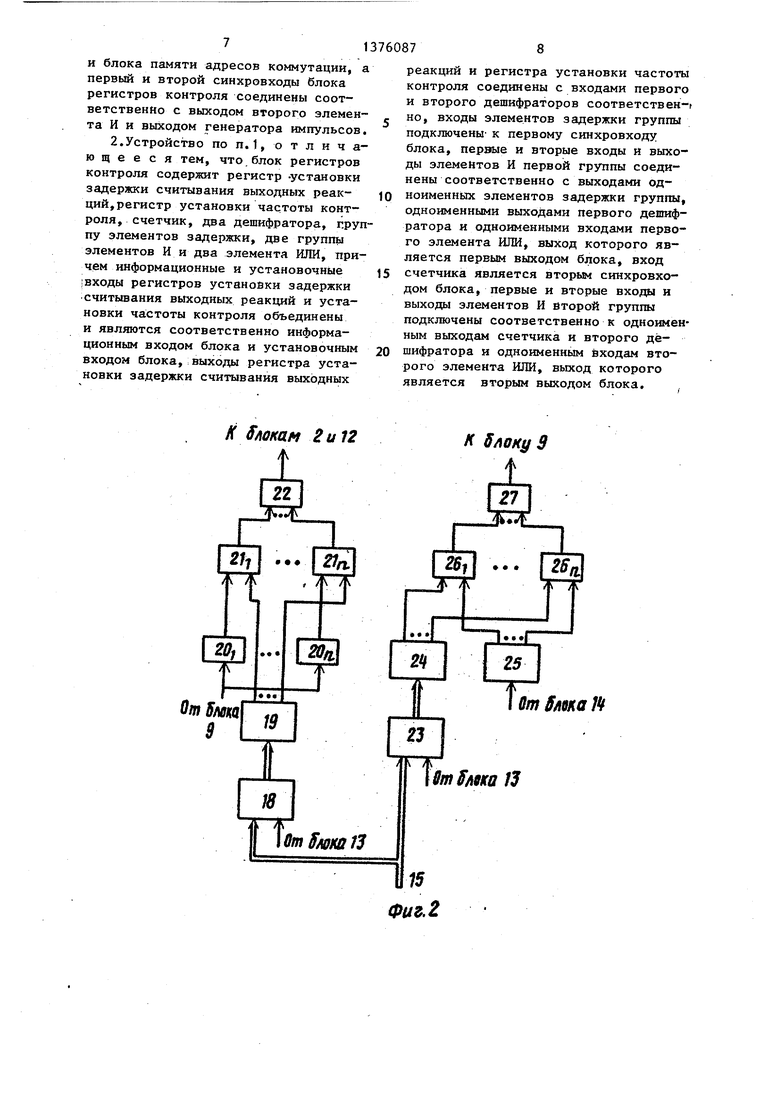

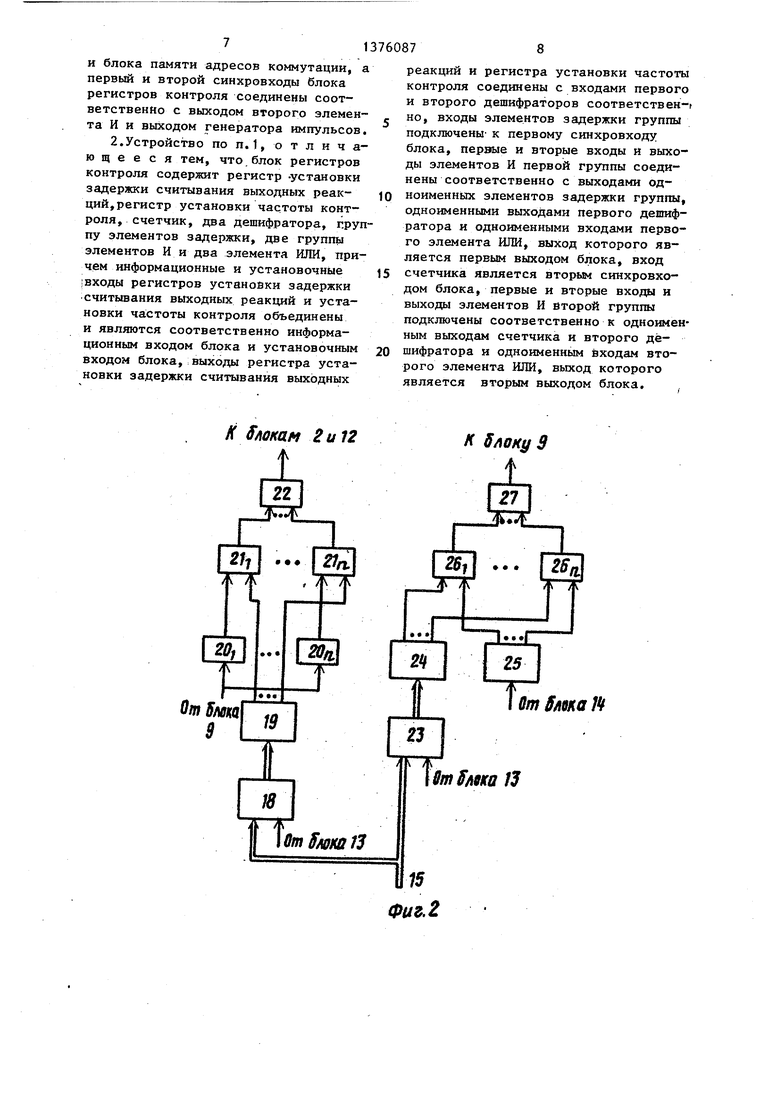

На фиг.1 представлена функциональная схема устройства; на фиг.2 - функциональная схема блока регистров контроля.

Устройство содержит (фиг.1) блок

Iпамяти тестов, блок 2 йамяти реакций, контролируемый модуль 3, блок

4 памяти адресов коммутации, коммутатор 5 тестов, счетчик 6 адреса, первый элемент -И 7, элемент ШШ 8, второй элемент И 9, триггер 10, блок

IIрегистров контроля, элемент 12 задержки, дешифратор 13, генератор 14 импульсов и имеет информационный вход 15, информационный выход 16 и вход 17 выборки.

Блок 11 регистров контроля содержит (фиг.2) регистр 18 установки задержки считьшания выходных реакций первьй дешифратор 19, группу элемен- тов задержки, первую группу элементов И 21,-2 If,, первый элемент ИЛИ 22, регистр 23 установки частоты контроля, второй дешифратор 24, счетчик (делитель) 25, вторую груп- пу элементов И 26, второй элемент ИЛИ 27. ,.

Блок 1 памяти тестов служит для хранения и формирования тестовой последовательности. Блок 2 памяти реакций предназначен для фиксации, хранения и считывания результатов контроля. Блок 4 памяти адресов коммутации предназначен для хранения контрольного распределения входов и выходов контролируемого модуля по каждому каналу и в каждом такте тестовых воздействий. Коммутатор 5 тестов предназначен для переключения входных и выходных каналов контроли- руемого модуля. Счетчик 6 адреса служит для формирования адреса блоков 1,2 и 4. Первый элемент И 7 предназначен для формирования сигнала переполнения счетчика 6 адреса. Элемент ИЛИ 8 дает возможность прибавлять 1 к содержимому счетчика 6 адреса как от элемента 12 задержки, так и от дешифратора 13.. Второй элемент

И 9 служит для запрета прохождения импульсов от-блока 11, когда триггер 10 находится в состоянии Останов. Триггер 10 предназначен для пуска и останова процесса прохождения тестов Блок 11 регистров контроля предназначен для организации контроля модуля в разных частотах а также управляет временем считывания реакции контролируемого модуля. Элемент 12 задерж1 и предназначен для получения временного сдвига между импульсами считывания блока 2 и импульсами, уве личиваюпщми содержимое счетчика 6 адреса на 1. Дешифратор 13 предназначен для формирования импульсов, предназначенных для первоначальной загрузки блоков 1 и 4, считывания результатов контроля из блока 2, установки параметров контроля в регистрах 18 и 23, прибавления к содержимому счетчика 6 адреса 1, установления счетчика 6 адреса в , запуска триггера 10. Генератор 14 импульсов выдает серию синхронизирующих импульсов. На вход 15 пос- .тупает код, записываемый в блоки 1,4 и 11. Выход 16 предназначен для съема реакций контролируемого модуля. На вход 17 подается код выборки соответствующего абонента и импульс сопровождения.

Устройство работает следующим образом.

Перед началом работы в подготовительном режиме на входе 17 устанавливается код, соответствующий сигналу установки в ноль счетчика 6 адреса, и подается импульс сопровождения На соответствующем выходе дешифратор 13 формируется импульс, который устанавливает в ноль счетчик 6 адреса. После этого на вход 15 подается первое тестовое слово, затем на входе 17 устанавливается код, соответствующий записи информации в блок 1, и подается импульс сопровождения. На соответствующем выходе дешифратора 13 формируется импульс, который записывает первое тестовое слово в блок 1 по нулевому адресу. После этого на входе 15 устанавливается код, задающий распределение входных и выходных контактов контролируемого модуля на первом тестовом слове, а на входе 17 устанавливается код, соответствующий записи информации в блок 4, и подается импульс сопровождения. На

соответствующем выходе дешифратора 13 формируется импульс, который записывает информацию, задающую распределение входных и выходных контактов контролируемого модуля на первом тестовом слове в блок 4 по нулевому адресу. В общем случае конт ролируемый модуль может иметь большое количество выводов, поэтому чтобы ограничить количество разрядов входа 15, тестовое слово и информацию о коммутации можно записывать в блоках 1 и 4 по группам. При этом каждой группе на входе 17 должен соответствовать код выборки, который дает возможность записать информацию в .блоках 1 и 4 по группам. Затем на входе 17 устанавливается код, соответствующий сигналу прибавления к содержимому счетчика 6 адреса 1, и подается импульс сопровождения. На соответствующем выходе дешифратора 13 формируется импульс, который через элемент ИЛИ 8 увеличивает содержимое счетчика 6 адреса на 1, и записывается информация по первому адресу блоков 1 и 4. Аналогичным образом в блоки 1 и 4 записывается информация по всем адресам. В соответствии с этим в каждом тестовом слове для входного контакта в блоке 4 записывается нулевая информация, а для выходного контакта - единичная информация.,

Для установки параметров контроля на входе 15 устанавливается информация, соответствующая необходимой задержке считывания данного контролируемого модуля, а на входе 17 выборки устанавливается код, соответствующий сигналу записи в регистр 18 установки задержки считывания выходных реакций, и подается импульс сопровождения. На выходе дешифратора 13 формируется импульс, который записывает установленную на входе 15 информацию в регистр 18. Аналогичным образом в регистре 23 установки частоты контроля записывается информация, соответствующая выборке необходимой частоты контроля. Серия импульсов из генератора 14 поступает на вход счетчика 25, на выходах которого формируются серии импульсов разной частоты, и в зависимости от содержимого регистра 23 выбирается соответствующий выход дешифратора 24 который разрешает поступление серии

импульсов выбранной частоты через один из элементов И 26| - 26 и через элемент ИЛИ 27 на второй вход элемента И 9.

После заполнения блоков 1 и 4.и установки регистров 18 и 23 счетчик 6 адреса устанавливается в О. На входе 17 устанавливается код, соответствующий формированию сигнала установки триггера 10 в единичное состояние, и подается импульс сопровождения. На соответствующем выходе дешифратора 13 формируется импульс,

который устанавливает триггер 1в в единичное состояние, благодаря чему устройство переводится в режим Прогон. В этом режиме серия импульсов, поступающих на второй вход элемента

И 9, проходит через него. Первый импульс серии считывает информацию по нулевому адресу блоков 1 и 4, которая поступает на входы коммутатора 5. На выходе коммутатора формируется код, каждый разряд которого может иметь три состояния. Если данный разряд коммутатора 5 подключен к входному контакту контролируемого модуля 3, тогда сигнал на выходе

коммутатора данного разряда принимости от информации, считанной из блока 1 памяти тестов (так как на управляющий вход коммутатора данного разряда от блока 4 поступает сигнал логического О, соответствующего входному контакту). Если данный разряд коммутатора 5 подключен к выходному контакту контролируемого модуля 3, тогда сигнал на выходе коммутатора данного разряда принимает высокоимпедансное состояние (так как на управляющий вход данного разряда коммутатора 5 от блока 4 , поступает сигнал логической 1, соответствующий выходному контакту), благодаря чему этот разряд на инфор-, мационном входе блока 2 данного разряда будет принимать значения, которые задает контролируемый модуль 3. В качестве коммутатора использованы элементы типа 133ЛП8 или 155ЛП8. Таким образом, как входные, так и выходные сигналы контролируемого модуля 3 оказываются подключенными к информационным входам блока 2 памяти реакций. Сигнал записи в блок 2 поступает из блока 11 и формируется еле ) дующим oiSpaaoM.

5

0

5

0

5

Первый импульс с выхода элемента И 9 поступает на входы элементов 20 задержки. При этом на выходах элементов 20,- 20„ формируются импульсы разной задержки, и в зависимости от содержимого регистра 18 установки задержки считывания выходных реакций выбранньй выход дешифратора 19 разрешает поступление через выбранный элемент из элементов И 21 группы задержанного импу- льса и через элемент ИЛИ 22 на вход записи блока 2, записывая в нем результат реализации первого тестового слова по нулевому адресу. Таким образом считывание выходных реакций контролируемого модуля 3 и запись их в блок 2 производится с учетом задержки распространения сигналов в данном контролируемом модуле.

Первый импульс, сформированный на выходе элемента ИЛИ 22, через элемент 12 задержки и элемент ИЛИ 8 поступает также на счетньш вход счетчика 6 адреса, вследствие чего следующий импульс , сформированный на выходе элемента И 9, организует реализацию второго тестового слова и т.д. Когда все тесты исчерпаны, сигнал с выхода элемента 17 перебрасывает триггер 10 в состояние, запрещающее прохождение импульсов через элемент И 9,

Выдача результатов контроля на выход 16 осуществляется установкой счетчика 6 адреса при помощи дешифратора 13 и формированием импульсов считывания. Для формирования импульса считывания на выходе 17 устанавливается код, соответствующий сигналу считывания, и подается импульс сопровождения. При этом на выходе дешифратора. 13 формируется импульс считьшания. Как запись в блоки 1 и 4, так и считывание из блока 2 можно производить по группам. Вход 15 и вход 17 выборки могут подключаться или к пульту, или к блоку ввода информации, или к микроэвм в зависимости от области применения устройст ва. То же самое можно сказать о выходе 16 для считывания информации. Он может подключаться как к просто-, му индикационному устройству, так

и к микроэвм...

Формула изобретения

1. Устройство для тестового контроля и диагностики цифровых модулей

0

0

5

содержащее бл ок памяти тестов и блок памяти реакций, отличающее- с я тем что, с целью расширения функциональных возможностей устройства путем подстройки частоты и изменения задержки считывания при контроле, оно содержит блок памяти адресов коммутации, коммутатор тестов, счетчик адреса, два элемента И, элемент ИЛИ, триггер, дешифратор, генератор импульсов, элемент задержки и блок регистров контроля, причем информационные входы блока памяти тестов, блока памяти адресов коммутации и блока регистров контроля образуют информационный вход утройст- ва, вход записи блока памяти тестов, вход записи блока памяти адресов коммутации,тгход считывания блока памяти реакций, установочный вход блока регистров контроля, первый вход элемента ИЛИ, вход сброса счетчика адреса, вход установки триггера под- 5 ключены к выходам дешифратора соответственно с первого по седьмой, вход дешифратора является входом выборки устройства, выход счетчика адреса подключен к адресным входам блока памяти тестов, блока памяти, адресов коммутации и блока памяти реакций и входам первого элемент-а И, выход которого соединен с входом сброса триггера, информационные выходы блока памяти тестов и блока памяти адресов коммутации подключены соответственно к информационному и управляющему входам коммутатора тестов, выход которого является выходом устройства для подключения к входу контролируемого модуля и соединен также с информационным входом блока памяти реакций, который является входом устройства для подключения к выходу контролируемого модуля, информационный выход блока памяти реакций является информационным выходом устройства, первый выход блока регистров контроля соединен с входом записи блока памяти реакций и входом элемента задержки, выход которого подключен к второму входу элемента ИЛИ, выход которого соединен со счетным входом счетчика адреса, первый и второй входы и выход-второго элемента И подключены соответственно к выходу триггера, второму выходу блока регистров контроля и входам считывания блока памяти тестов и

5

0

5

0

5

и блока памяти адресов коммутации, а первый и второй синхровходы блока регистров контроля соединены соответственно с выходом второго элемента И и выходом генератора импульсов. 2.Устройство по п.1, о т л и ч а- ю щ е а с я тем, что блок регистров контроля содержит регистр -установки задержки считывания выходных реак- ций,регистр установки частоты контроля, счетчик, два дешифратора, группу элементов задержки, две группы элементов И и два элемента ИЛИ, причем информационные и установочные входы регистров устаноеки задержки считывания выходных реакций и установки ча:стоты контроля объединены и являются соответственно информационным входом блока и установочным входом блока, выходы регистра установки задержки считывания выходных

реакций и регистра установки частоты контроля соединены с входами первого и второго дешифраторов соответственно, входы элементов задержки группы подключены- к первому синхровходу блока, первые и вторые входы и выходы элементов И первой грзтпы соединены соответственно с выходами одноименных элементов задержки группы, одноименными выходами первого дешифратора и одноименными входами первого элемента ИЛИ, выход которого является первым выходом блока, вход счетчика является вторьм синхровхо- дом блока, первые и вторые входа и выходы элементов И второй группы подключены соответственно к одноименным выходам счетчика и второго дешифратора и одноименным входам второго элемента ИЛИ, выход которого является вторым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1700557A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1683015A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Многоканальное устройство тестового контроля логических узлов | 1985 |

|

SU1265778A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Многоканальное устройство для контроля систем управления | 1985 |

|

SU1345200A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Устройство для контроля памяти | 1985 |

|

SU1316052A1 |

Изобретение относится к контрольно-измерительной технике и может быть использовано для контроля и диагностики многоразрядных цифровых узлов радиоэлектронной аппаратуры. Целью изобретения является расширение функциональных возможностей устройства путем подстройки частоты и изменения задержки считывания при контроле. С этом целью в устройство, содержащее блок 1 памяти тестов и блок 2 памяти реакций, введены блок 4 памяти адресов коммутации, коммутатор 5 тестов, счетчик 6 адреса, элементы И 7, 9, элемент ИЛИ 8, триггер 10, дешифратор 13, генератор 14 импульсов, элемент 12 задержки и блок 11 регистров контроля. 2 ил.

К блокам 2 и 12

1

22

.

От SMKU

Iffm Дш J3

К 5лону 9

А

Ш.

а,

/V

/ / V

Ш

2ii

25

lOmffmafif

23

SmfA9Ka /J

| Патент США 3849726, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Устройство для контроля микропроцессора | 1977 |

|

SU660053A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-23—Публикация

1986-08-18—Подача