Изобретение относится- к вычислительной технике и может быть использовано как совместно с ЭВМ при построении высокопроизводительных систем сбора и обработки аналоговых данных, так и отдельно при построении многоканальных информационно-измерительных систем.

Цель изобретения - сокращение избыточности выводимой информации.

В устройстве сокращение избыточности выходных данных обеспечивается уменьшением служебных данных о временной привязке существенных отсчетов и устранением кодов канальной привязки существенных отсчетов. При этом на выходе устройства формируется бит - ориентированный код в виде следующей последовательности: G;T;ЈX;, где GJ. - бит текущего признака кода Галуа который принимает значение 0 или 1 в зависимости от кодового ключа генератора кодов поля Галуа; Т| - бит признака существенности отсчета, причем при Т 1 отсчет является существенным, а при Т - 0 - несущественным; Јх«Д- k-битовый двоичный код существенного отсчета (1с - количество битов последовательного кода). Если текущий отсчет входного сигнала является существенным, а последующий отсчет является несущественным, то устройство формирует следующую последовательность: G; l(X;JGi+,OGj+2/ Восстановление сжатых сигналов осуществляется по меткам G с учетом текущих значений признака Т |.

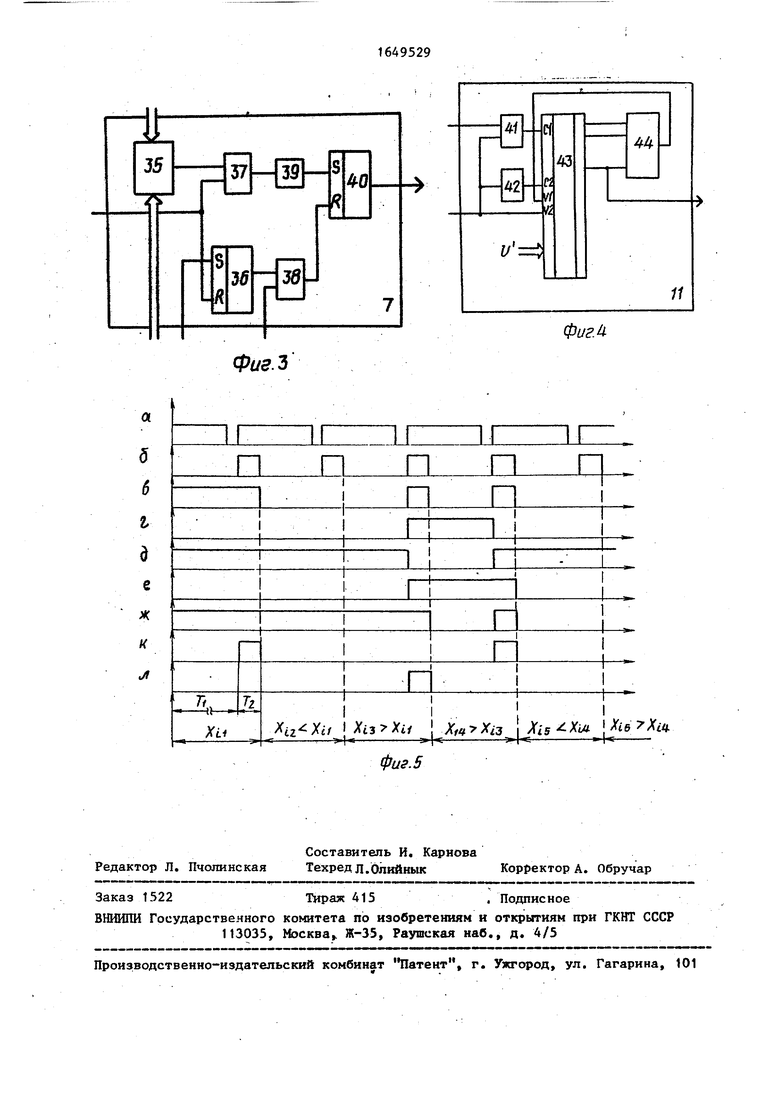

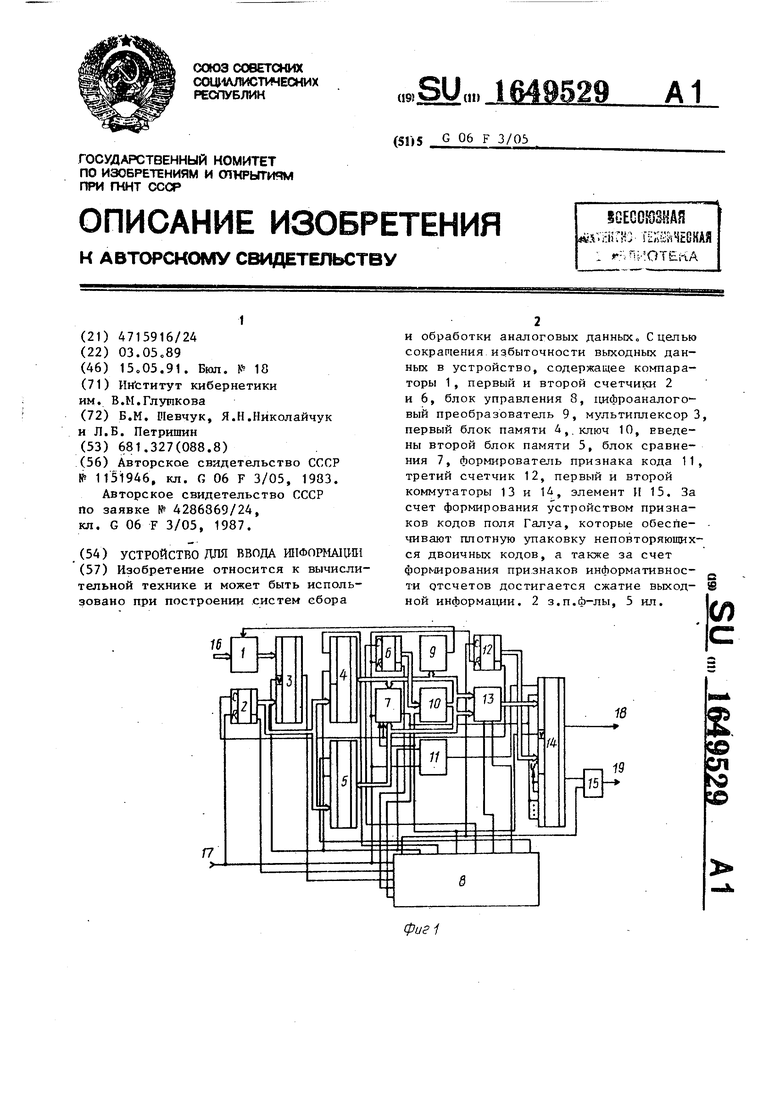

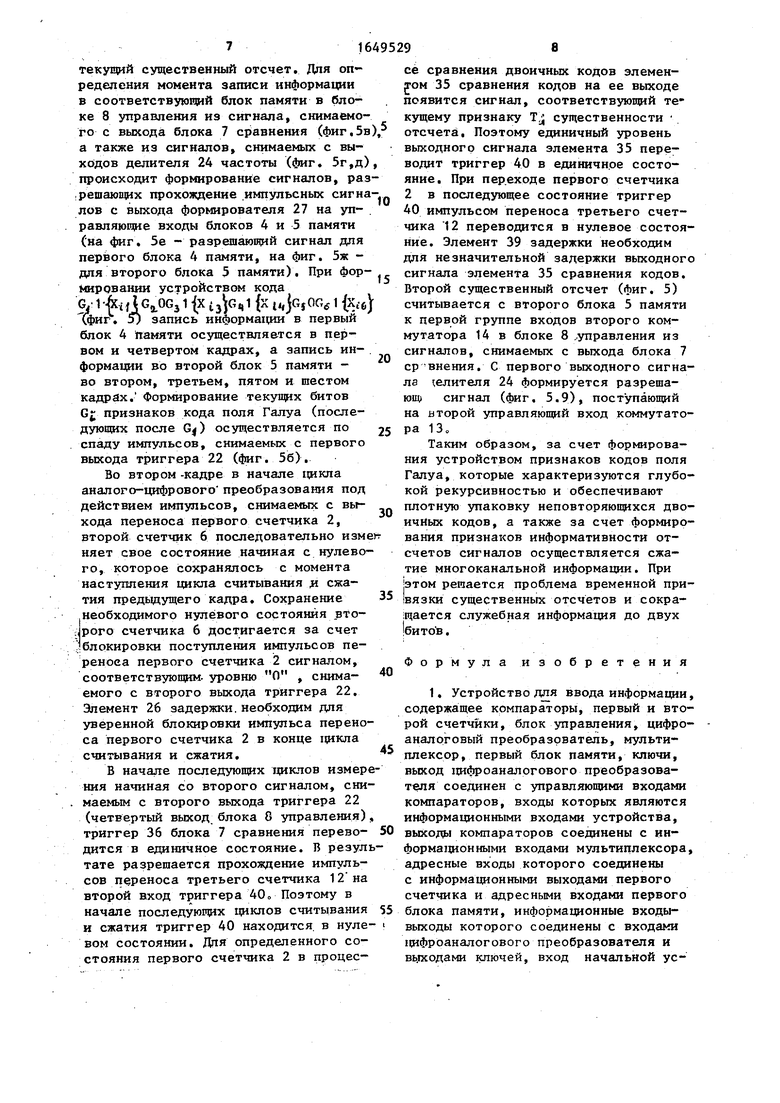

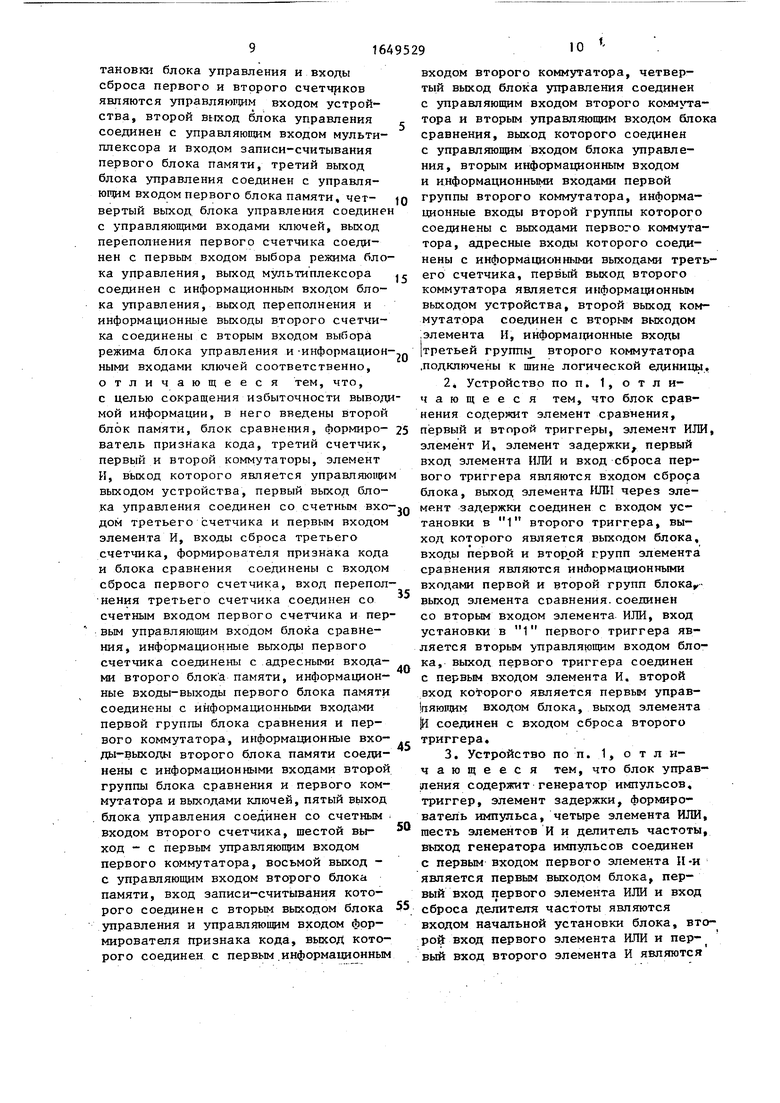

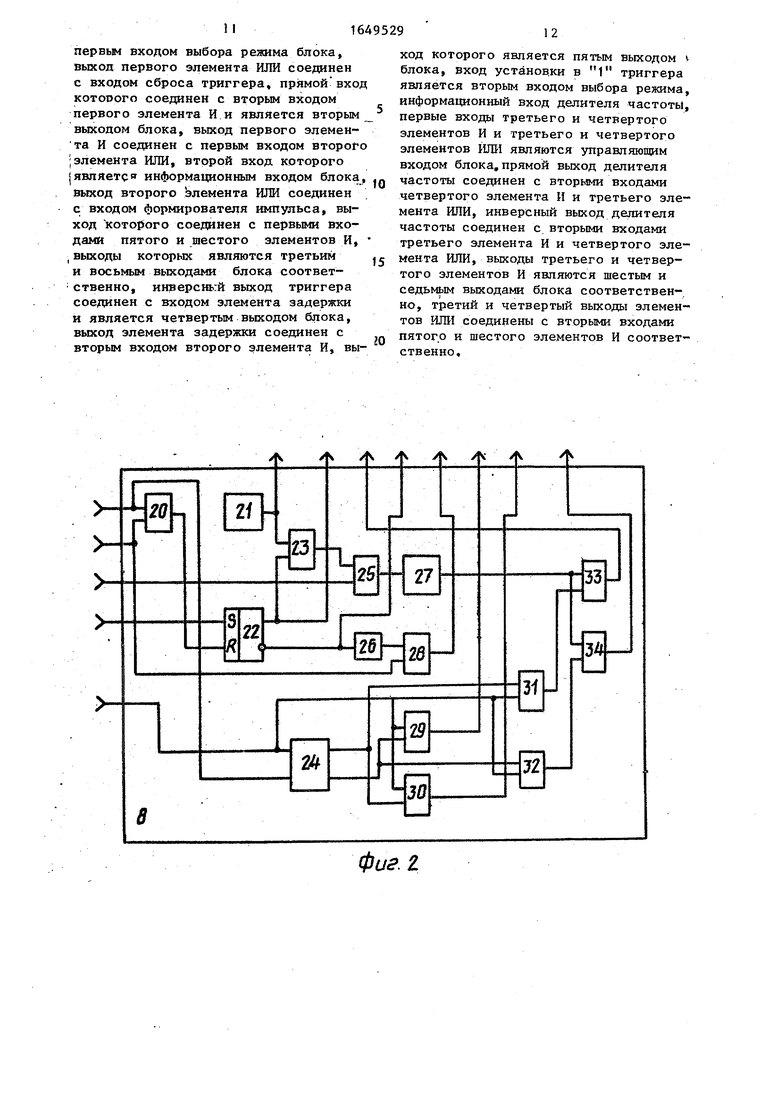

На фиг. 1 приведена структурная схема устройства)на фиг. 2 - струк- турная схема блока управления; на фиг. 3 - структурная схема блока сравнения кодов; на фиг, 4 - структурная схема формирователя признака кода; на фиг. 5 - временные диаграммы работы устройства.

Устройство содержит компараторы 1, Первый счетчик 2, мультиплексор 3, первый 4 и второй 5 блоки памяти, второй счетчик 6, блок 7 сравнения, блок 8 управления, цифроаналоговый преобразователь (ЦАП) 9, ключи 10, формирователь 11 признака кода, третий счетчик 12, первый 13 и второй 14 коммутаторы и элемент И 15 и имеет входы и выходы 16-19 устройства.

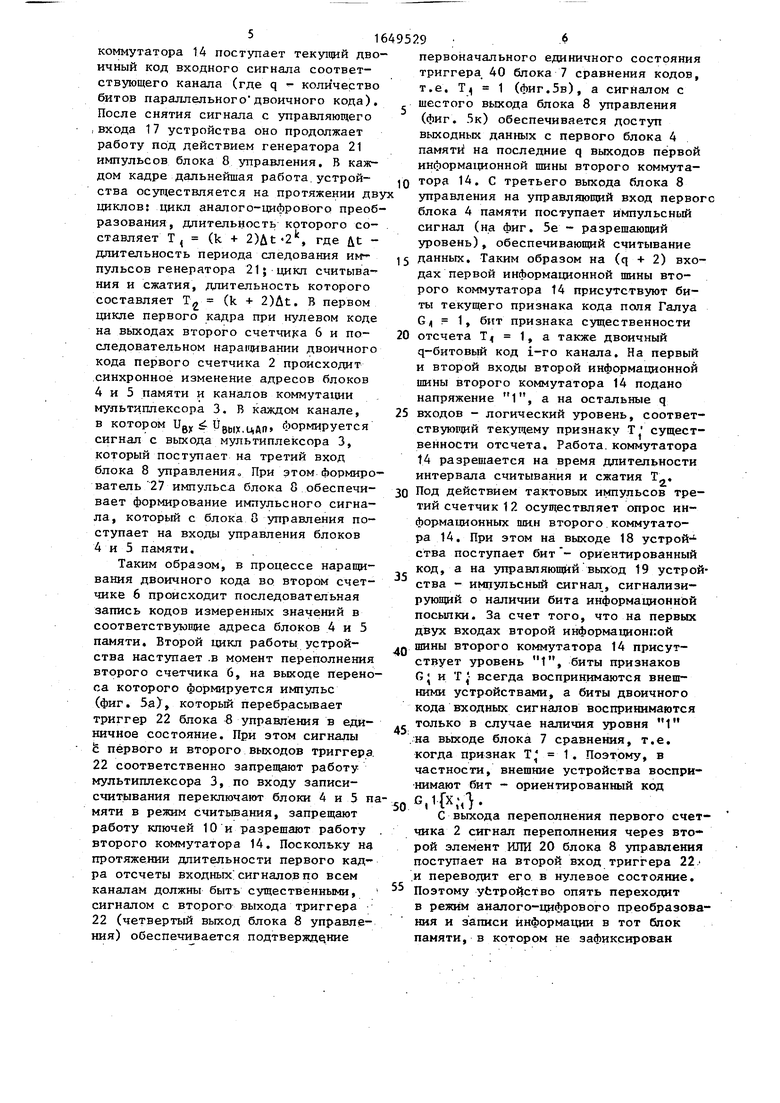

Блок 8 управления состоит из пер- вого элемента ИЛИ 20, генератора 21 импульсов, триггера 22, первого элемен

Q

0 5

5

та , делителя частоты 24, второго элемента ИЛИ 25, элемента 26 задержки, формирователя 27 импульса, второго 28, третьего 29 и четвертого 30 элементов И, третьего 31 и четвертого 32 элементов ИЛИ, пятого 33 и шестого 34 элементов И.

Блок 7 сравнения содержит элемент 35 сравнения, первый триггер 36, элемент ИЛИ 37, элемент И 38, элемент 39 задержки и второй триггер 40.

Формирователь 11 признака кода образуют элемент ИЛИ 41, одновибра- тор 42, регистр 43 и элементы 44 обратной связи.

Устройство для ввода информации работает следующим образом.

Входные аналоговые сигналы поступают на входы устройства 16. На входы компараторов 1 подается выходной сигнал ЦАП 9. Для приведения устройства в исходное состояние подается сигнал на управляющий вход 17. При этом Ьчетчики 2, 6 и 12, триггер 22, делитель 24 блока 8 управления, и триггер 36 блока 7 сравнения сбрасываются в нулевое состояние, триггер 40 блока 7 сравнения устанавливается в единичное состояние, обеспечивается установка в начальное состояние формирователя 11 (формирователь 11 может быть реализован на регистре сдвига с линейной цепью обратной связи), упрощенная структурная схема которого приведена на фиг. 4. Перепадом 1-0 с выхода одновибратора 42 обеспечивается запись в регистр сдвига 43 начального кода 111 ... 1 , а также выдача формирователем 11 текущего признака G j 1 кода поля Галуа (перепадом ; 1,0). В этом состоянии сигналом с первого выхода триггера 22 блока 8 управления (фиг. 5о2) разрешается работа мультиплексора 3, блоки 4 и 5 памяти по входу записи - считывания переводятся в режим записи, сигналом с второго выхода триггера 22 (четвертого выхода блока 8 управления) разрешается работа ключей 10 и запрещается работа второго коммутатора 14.

Таким образом, в исходном состоянии с выхода формирователя 11 на первый вход второго коммутатора 14 поступает признак G: 1 кода поля Галуа, на второй вход коммутатора 14 поступает бит признака Т существенности цифрового отсчета входного сигнала (Т 1 ), а на остальные q-e входы

51

коммутатора 14 поступает текущий дво ичный код входного сигнала соответствующего канала (где q - количество битов параллельного двоичного кода). После снятия сигнала с управляющего входа 17 устройства оно продолжает работу под действием генератора 21 импульсов блока 8 управления. В каждом кадре дальнейшая работа устройства осуществляется на протяжении дв циклов: цикл аналого-цифрового преобразования, длительность которого со

ставляет Т (k + 2)ДИ-2 , где &t - длительность периода следования импульсов генератора 21; цикл считывания и сжатия, длительность которого составляет Т- (k + 2)At. В первом цикле первого кадра при нулевом коде на выходах второго счетчика 6 и последовательном наращивании двоичного кода первого счетчика 2 происходит синхронное изменение адресов блоков 4 и 5 памяти и каналов коммутации мультиплексора 3. В каждом канале, в котором UB)f UBblx,цдп формируется сигнал с выхода мультиплексора 3, который поступает на третий вход блока 8 управления При этом Формирователь 27 импульса блока 8 обеспечивает формирование импульсного сигнала, который с блока 0 управления поступает на входы управления блоков 4 и 5 памяти.

Таким образом, в процессе наращивания двоичного кода во втором счетчике 6 происходит последовательная запись кодов измеренных значений в соответствующие адреса блоков 4 и 5 памяти. Второй цикл работы устройства наступает в момент переполнения второго счетчика 6, на выходе переноса которого формируется импульс (фиг. 5а), который перебрасывает триггер 22 блока 8 управления в единичное состояние. При этом сигналы с первого и второго выходов триггера 22 соответственно запрещают работу мультиплексора 3, по входу записи- считывания переключают блоки 4 и 5 пмяти в режим считывания, запрещают работу ключей 10 и разрешают работу второго коммутатора 14. Поскольку на протяжении длительности первого кадра отсчеты входных сигналов по всем каналам должны быть существенными, сигналом с второго выхода триггера 22 (четвертый выход блока 8 управления) обеспечивается подтверждение

первоначального единичного состояния триггера, 40 блока 7 сравнения кодов, т.е. Т 1 (фиг.5в), а сигналом с шестого выхода блока 8 управления (фиг. 5к) обеспечивается доступ выходных данных с первого блока 4 памяти1 на последние q выходов первой информационной шины второго коммутатора 14. С третьего выхода блока 8 управления на управляющий вход первого блока 4 памяти поступает импульсный сигнал (на фиг. 5е - разрешающий уровень), обеспечивающий считывание

5 данных. Таким образом на (q + 2) входах первой информационной шины второго коммутатора 14 присутствуют биты текущего признака кода поля Галуа G4 1, бит признака существенности

0 отсчета Tj 1, а также двоичный

q-битовый код 1-го канала. На первый и второй входы второй информационной шины второго коммутатора 14 подано напряжение 1, а на остальные q

5 входов - логический уровень, соответствующий текущему признаку Т существенности отсчета. Работа коммутатора 14 разрешается на время длительности интервала считывания и сжатия Т.

0 Под действием тактовых импульсов третий счетчик 12 осуществляет опрос информационных шин второго коммутатора 14. При этом на выходе 18 устрой-1 ства поступает бит - ориентированный код, а на управляющий выход 19 устройства - импульсный сигнал, сигнализирующий о наличии бита информационной посыпки. За счет того, что на первых двух входах второй информационной

Q шины второго коммутатора 14 присутствует уровень 1, биты признаков G« и Т t всегда воспринимаются внешними устройствами, а биты двоичного кода входных сигналов воспринимаются только в случае наличия уровня 1 на выходе блока 7 сравнения, т.е. когда признак Т, 1 . Поэтому, в частности, внешние устройства воспринимают бит - ориентированный код

0СЛХ, ЛС выхода переполнения первого счетчика 2 сигнал переполнения через второй элемент ИЛИ 20 блока 8 управления поступает на второй вход триггера 22 - и переводит его в нулевое состояние.

5 Поэтому устройство опять переходит

в режим аналого-цифрового преобразования и записи информации в тот блок памяти, в котором не зафиксирован

5

71649529

текущий существенный отсчет. Для определения момента записи информации в соответствующий блок памяти в блоке 8 управления из сигнала, снимаемо8

се сравнения двоичных кодов элементом 35 сравнения кодов на ее выходе появится сигнал, соответствующий те кущему признаку Tj существенности

го с выхода блока 7 сравнения (фиг.5в), отсчета. Поэтому единичный уровень

8

се сравнения двоичных кодов элементом 35 сравнения кодов на ее выходе появится сигнал, соответствующий те кущему признаку Tj существенности

отсчета. Поэтому единичный уровень

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сжатия аналоговой информации | 1988 |

|

SU1709368A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для приема информации | 1988 |

|

SU1552216A1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501298A1 |

| Устройство для отображения информации | 1987 |

|

SU1474634A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1564661A1 |

| Устройство для телеконтроля | 1990 |

|

SU1732366A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении систем сбора и обработки аналоговых данных. С целью сокращения избыточности выходных данных в устройство, содержащее компараторы 1, первый и второй счетчики 2 и 6, блок управления 8, цифроаналого- вый преобразователь 9, мультиплексор 3, первый блок памяти 4, ключ 10, введены второй блок памяти 5, блок сравнения 7, формирователь признака кода 11, третий счетчик 12, первый и второй коммутаторы 13 и 14, элемент И 15. За счет формирования устройством признаков кодов поля Галуа, которые обеспечивают плотную упаковку неповторяющихся двоичных кодов, а также за счет формирования признаков информативности отсчетов достигается сжатие выходной информации. 2 з.п.ф-лы, 5 ил. (Л

а также из сигналов, снимаемых с выходов делителя 24 частоты (фиг. 5г,д), происходит формирование сигналов, разрешающих прохождение импульсных сигналов с выхода формирователя 27 на управляющие входы блоков 4 и 5 памяти (на фиг. 5е - разрешающий сигнал для первого блока 4 памяти, на фиг. 5ж - для второго блока 5 памяти). При формировании устройством кода G, 1 &,, I СгОС31 (X , 1 (X 1„JG,OGtf I (Xt-6) (фиг. 5) запись информации в первый блок 4 памяти осуществляется в первом и четвертом кадрах, а запись информации во второй блок 5 памяти - во втором, третьем, пятом и шестом кадрах. Формирование текущих битов GЈ признаков кода поля Галуа (последующих после G|) осуществляется по спаду импульсов, снимаемых с первого выхода триггера 22 (фиг. 56).

Во втором -кадре в начале цикла аналого-цифрового преобразования под действием импульсов, снимаемых с выхода переноса первого счетчика 2, второй счетчик 6 последовательно измег- няет свое состояние начиная с нулевого, которое сохранялось с момента наступления цикла считывания д сжатия предыдущего кадра. Сохранение необходимого нулевого состояния вто- Jporo счетчика 6 достигается за счет блокировки поступления импульсов переноса первого счетчика 2 сигналом, соответствующим уровню О , снимаемого с второго выхода триггера 22. Элемент 26 задержки необходим для уверенной блокировки импульса переноса первого счетчика 2 в конце цикла считывания и сжатия.

В начале последующих циклов измерения начиная со второго сигналом, снимаемым с второго выхода триггера 22 (четвертый выход блока 8 управления),

10

15

20

25

30

35

40

45

выходного сигнала элемента 35 переводит триггер 40 в единичное состояние. При переходе первого счетчика 2 в последующее состояние триггер 40 импульсом переноса третьего счетчика 12 переводится в нулевое состоя ние. Элемент 39 задержки необходим для незначительной задержки выходног сигнала элемента 35 сравнения кодов. Второй существенный отсчет (фиг. 5) считывается с второго блока 5 памяти к первой группе входов второго коммутатора 14 в блоке 8 управления из сигналов, снимаемых с выхода блока 7 ср внения. С первого выходного сигна ла {елителя 24 формируется разреша- ющ сигнал (фиг. 5.9), поступающий на второй управляющий вход коммутато ра 13,

Таким образом, за счет формирования устройством признаков кодов поля Галуа, которые характеризуются глубо кой рекурсивностью и обеспечивают плотную упаковку неповторяющихся дво ичных кодов, а также за счет формиро вания признаков информативности отсчетов сигналов осуществляется сжатие многоканальной информации. При этом решается проблема временной при вязки существенных отсчетов и сокращается служебная информация до двух битов.

Формула изобретения

1, Устройство для ввода информации содержащее компараторы, первый и вто рой счетчики, блок управления, цифро аналоговый преобразователь, мультиплексор, первый блок памяти, ключи, выход цифроаналогового преобразователя соединен с управляющими входами компараторов, входы которых являются информационными входами устройства,

триггер 36 блока 7 сравнения перево- 50 выходы компараторов соединены с ин- дится в единичное состояние. В результате разрешается прохождение импульсов переноса третьего счетчика 12 на второй вход триггера 40 Поэтому в начале последующих циклов считывания 55 и сжатия триггер 40 находится в нуле- вом состоянии. Для определенного состояния первого счетчика 2 в процесформационными входами мультиплексора адресные входы которого соединены с информационными выходами первого счетчика и адресными входами первого блока памяти, информационные входы- выходы которого соединены с входами цифроаналогового преобразователя и выходами ключей, вход начальной ус

выходного сигнала элемента 35 переводит триггер 40 в единичное состояние. При переходе первого счетчика 2 в последующее состояние триггер 40 импульсом переноса третьего счетчика 12 переводится в нулевое состояние. Элемент 39 задержки необходим для незначительной задержки выходного сигнала элемента 35 сравнения кодов. Второй существенный отсчет (фиг. 5) считывается с второго блока 5 памяти к первой группе входов второго коммутатора 14 в блоке 8 управления из сигналов, снимаемых с выхода блока 7 ср внения. С первого выходного сигнала {елителя 24 формируется разреша- ющ сигнал (фиг. 5.9), поступающий на второй управляющий вход коммутатора 13,

Таким образом, за счет формирования устройством признаков кодов поля Галуа, которые характеризуются глубокой рекурсивностью и обеспечивают плотную упаковку неповторяющихся двоичных кодов, а также за счет формирования признаков информативности отсчетов сигналов осуществляется сжатие многоканальной информации. При этом решается проблема временной привязки существенных отсчетов и сокращается служебная информация до двух битов.

Формула изобретения

1, Устройство для ввода информации, содержащее компараторы, первый и второй счетчики, блок управления, цифро- аналоговый преобразователь, мультиплексор, первый блок памяти, ключи, выход цифроаналогового преобразователя соединен с управляющими входами компараторов, входы которых являются информационными входами устройства,

выходы компараторов соединены с ин-

выходы компараторов соединены с ин-

формационными входами мультиплексора, адресные входы которого соединены с информационными выходами первого счетчика и адресными входами первого блока памяти, информационные входы- выходы которого соединены с входами цифроаналогового преобразователя и выходами ключей, вход начальной ус

916

тановки блока управления и входы сброса первого и второго счетчиков являются управляющим входом устройства, второй выход блока управления соединен с управляющим входом мультиплексора и входом записи-считывания первого блока памяти, третий выход блока управления соединен с управляющим входом первого блока памяти, четвертый выход блока управления соедине с управляющими входами ключей, выход переполнения первого счетчика соединен с первым входом выбора режима блока управления, выход мультиплексора соединен с информационным входом блока управления, выход переполнения и информационные выходы второго счетчика соединены с вторым входом выбора режима блока управления и-информационными входами ключей соответственно, отличающееся тем, что, с целью сокращения избыточности выводмой информации, в него введены второй

30

35

40

блок памяти, блок сравнения, формиро- 25 первый и второй триггеры, элемент ИЛИ,

элемент И, элемент задержкил первый вход элемента ИЛИ и вход сброса первого триггера являются входом сброса блока, выход элемента ИЛИ через элемент задержки соединен с входом установки в 1 второго триггера, выход которого является выходом блока, входы первой и второй групп элемента сравнения являются информационными входами первой и второй групп блока,.- выход элемента сравнения.соединен со вторым входом элемента ИЛИ, вход установки в 1 первого триггера является вторым управляющим входом блока, выход первого триггера соединен с первым входом элемента И. второй вход которого является первым управ- пяющим входом блока, выход элемента |И соединен с входом сброса второго триггера.

ватель признака кода, третий счетчик, первый и второй коммутаторы, элемент И, выход которого является управляющим выходом устройства, первый выход блока управления соединен со счетным входом третьего счетчика и первым входом элемента И, входы сброса третьего счетчика, формирователя признака кода и блока сравнения соединены с входом сброса первого счетчика, вход переполнения третьего счетчика соединен со счетным входом первого счетчика и первым управляющим входом блока сравнения, информационные выходы первого счетчика соединены с адресными входами второго блока памяти, информационные входы-выходы первого блока памяти соединены с информационными входами первой группы блока сравнения и первого коммутатора, информационные входы-выходы второго блока памяти соединены с информационными входами второй группы блока сравнения и первого коммутатора и выходами ключей, пятый выход блока управления соединен со счетным входом второго счетчика, шестой выход - с первым управляющим входом первого коммутатора, восьмой выход - с управляющим входом второго блока памяти, вход записи-считывания которого соединен с вторым выходом блока 55 управления и управляющим входом формирователя признака кода, выход которого соединен с первым информационным

45

50

1

входом второго коммутатора, четвертый выход блока управления соединен с управляющим входом второго коммутатора и вторым управляющим входом блока сравнения, выход которого соединен с управляющим входом блока управления, вторым информационным входом и информационными входами первой группы второго коммутатора, информационные входы второй группы которого соединены с выходами первого коммутатора, адресные входы которого соединены с информационными выходами третьего счетчика, первый выход второго коммутатора является информационным выходом устройства, второй выход коммутатора соединен с вторым выходом элемента И, информационные входы третьей группы второго коммутатора .подключены к шине логической единицы.

30

5

35

5

40

55

55

45

55

50

первым входом выбора режима блока, выход первого элемента ИЛИ соединен с входом сброса триггера, прямой вход КОТОРОГО соединен с вторым входом первого элемента И и является вторым выходом блока, выход первого элемен- та И соединен с первым входом второго (элемента ИЛИ, второй вход которого (является информационным входом блока, выход второго элемента ИЛИ соединен с входом формирователя импульса, выход которого соединен с первыми входами пятого и шестого элементов И, ,выходы которых являются третьим и восьмым выходами блока соответственно, инверсный выход триггера соединен с входом элемента задержки и является четвертым выходом блока, выход элемента задержки соединен с вторым входом второго элемента И, вы

ход которого является пятым выходом v блока, вход установки в 1 триггера является вторым входом выбора режима, информационный вход делителя частоты первые входы третьего и четвертого элементов И и третьего и четвертого элементов ИЛИ являются управляющим входом блока,прямой выход делителя частоты соединен с вторыми входами четвертого элемента И и третьего элемента ИЛИ, инверсный выход делителя частоты соединен с вторыми входами третьего элемента И и четвертого элемента ИЛИ, выходы третьего и четвертого элементов И являются шестым и седьмым выходами блока соответственно, третий и четвертый выходы элементов ИЛИ соединены с вторыми входами пятого и шестого элементов И соответственно.

фиг. г

Фиг. 5

| Устройство для ввода информации | 1983 |

|

SU1151946A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР по заявке № 4286869/24, кл, G 06 F 3/05, 1987. | |||

Авторы

Даты

1991-05-15—Публикация

1989-05-03—Подача