Изобретение относится к автоматизации и вычислительной технике.

Цель изобретения - упрощение преобразователя .

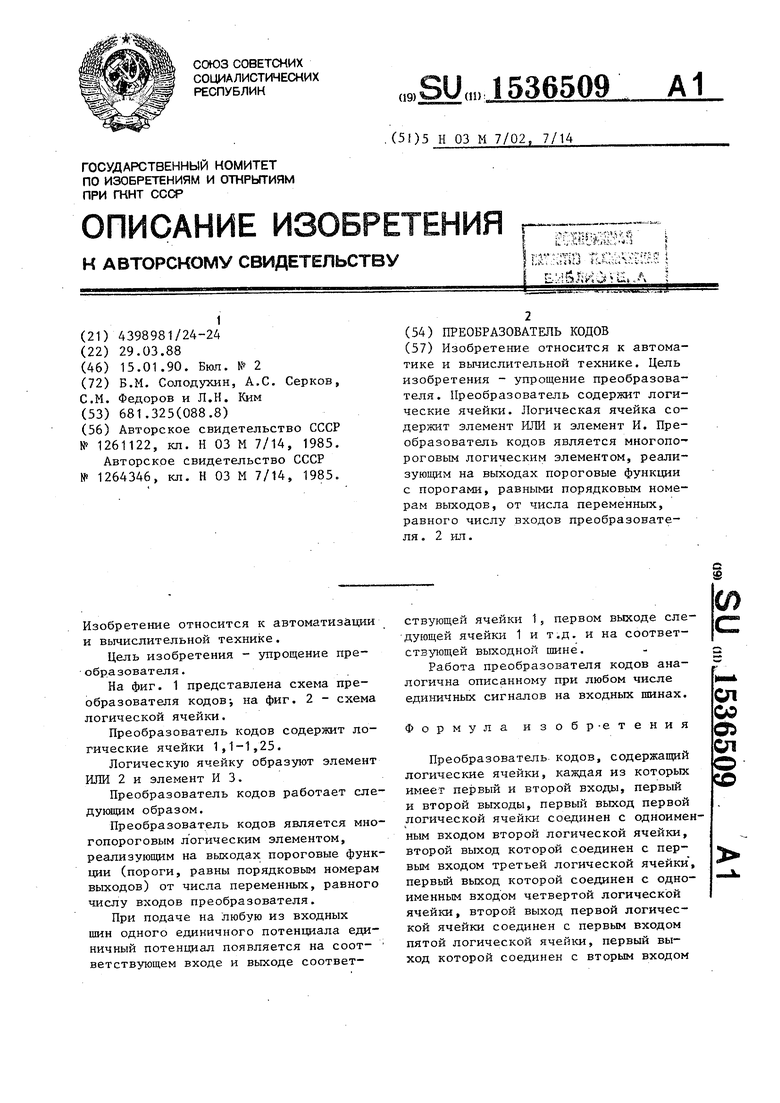

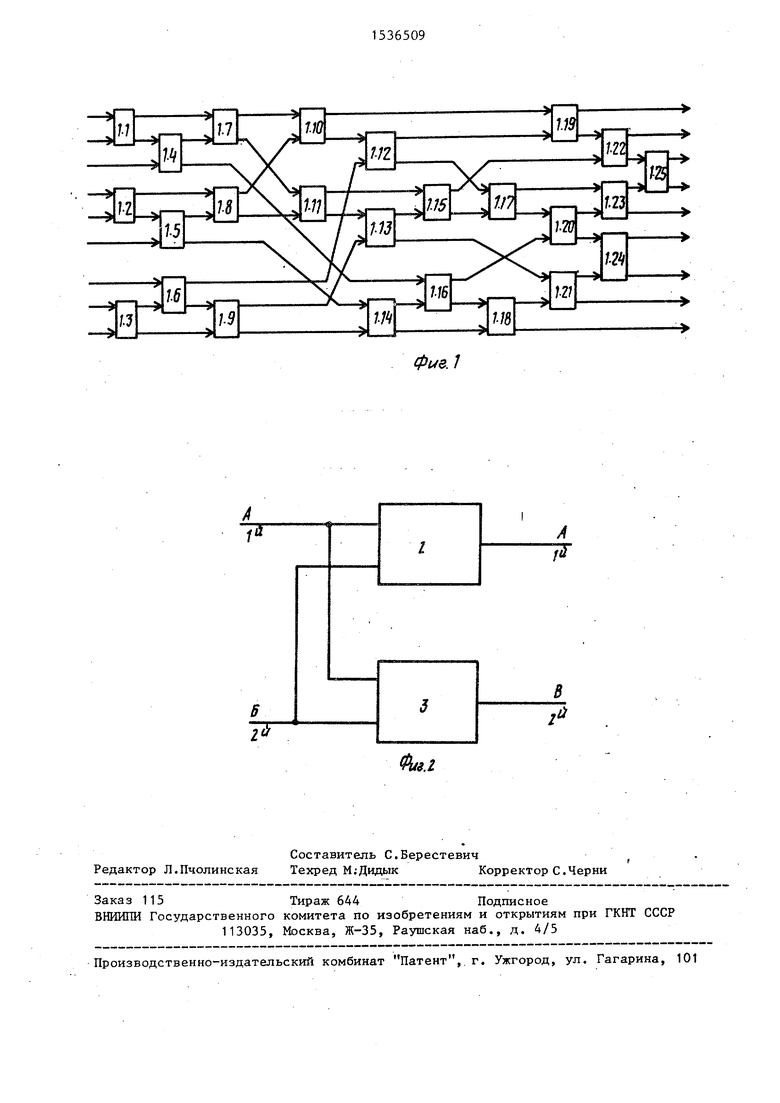

На фиг. 1 представлена схема преобразователя кодов-, на фиг. 2 - схема логической ячейки.

Преобразователь кодов содержит логические ячейки 1,1-1,25.

Логическую ячейку образуют элемент ИЛИ 2 и элемент И 3.

Преобразователь кодов работает следующим образом.

Преобразователь кодов является многопороговым логическим элементом, реализующим на выходах пороговые функции (пороги, равны порядковым номерам выходов) от числа переменных, равного числу входов преобразователя.

При подаче на любую из входных шин одного единичного потенциала единичный потенциал появляется на соответствующем входе и выходе соответствующей ячейки 15 первом выходе следующей ячейки 1 и т.д. и на соответствующей выходной шине.

Работа преобразователя кодов аналогична описанному при любом числе единичных сигналов на входных шинах.

Формула изобр-етения

Преобразователь кодов, содержащий логические ячейки, каждая из которых имеет первый и второй входы, первый и второй выходы, первый выход первой логической ячейки соединен с одноименным входом второй логической ячейки, второй выход которой соединен с первым входом третьей логической ячейки, первый выход которой соединен с одноименным входом четвертой логической ячейки, второй выход первой логической ячейки соединен с первым входом пятой логической ячейки, первый выход которой соединен с вторым входом

СП

оэ а ел

второй логической ячейки, второй выход третьей логической ячейки соединен с первым входом шестой логической ячейки, первый выход которой соединен с вторым входом четвертой логической ячейки, первый выход седьмой логической ячейки соединен с одноименным входом восьмой логической ячейки, второй выход седьмой логичес- кой ячейки соединен с первым входом девятой логической ячейки, первый выход которой соединен с вторым входом восьмой логической ячейки, второй выход десятой логической ячейки соеди- нен с первым входом одиннадцатой логической ячейки, первый выход которой соединен с вторым входом двенадцатой логической ячейки, второй выход одиннадцатой логической ячейки соединен с первым входом тринадцатой ячейки, первый выход которой соединен с вторым входом четырнадцатой логической ячейки,первый выход которой соединен с вторым входом пятнадцатой логической ячейки, первый выход которой соединен с вторым входом шестнадцатой логической ячейки, второй выход пятнадцатой логической ячейки соединен с первым входом семнадцатой логической ячейки, первый выход восемнадцатой логической ячейки соединен с вторым входом двенадцатой логической ячейки, второй выход которой соединен с первым входом двадцатой логической ячейки, второй выход которой соединен с одно- именным входом тринадцатой логической ячейки, второй выход восемнадцатой логической ячейки соединен с одноименным входом двадцатой логической ячейки, второй выход четырнадцатой логи- ческой ячейки соединен с первым входом двадцать первой логической ячейки, второй выход тринадцатой логической ячейки соединен с одноименным входом двадцать первой логической ячейки, двадцать вторую - двадцать пятую логические ячейки, вторые выходы Шестнадцатой и двадцать первой логических ячеек и первый и второй выходы семнадцатой логической ячейки являются соответственно первым - четвертым выходам преобразователя, о т- личающийся тем, что, с целью упрощения преобразователя, пер

0

Q ,- s 35 4045 50

30

вый выход второй логической ячейки соединен с одноименным входом седьмой логической ячейки, второй выход восьмой логической ячейки соединен с первым входом двадцать второй логической ячейки, второй выход которой соединен с первым входом двадцать третьей логической ячейки, второй выход пятой логической ячейки соединен с первым входом четырнадцатой логической ячейки, первый выход двенадцатый логической ячейки соединен с вторым входом девятой логической ячейки, второй выход которой соединен с первым входом двадцать пятой логической ячейки, первый выход которой соединен с одноименным входом шестнадцатой логической ячейки, первши выход которой соединен с вторым входом двадцать третьей логической ячейки, первый и второй выходы четвертой логической ячейки соединены соответственно, с вторыми входами двадцать второй и двадцать пятой логических ячеек, второй выход двадцать пятой логической ячейки соединен с первым входом пятнадцатой логической ячейки, первый выход десятой логической ячейки соединен с одноименным входом двенадцатой логической ячейки, первый и второй выходы которой соединены с вторыми входами, соответственно седьмой и третьей логических ячеек, первый выход двадцатой логической ячейки соединен с вторым входом шестой логической ячейки, второй выход которой и первый выход двадцать первой логической ячейки соединены соответственно с первым и вторым входами двадцать четвертой логической ячейки, первый выход которой соединен с вторым входом семнадцатой логической ячейки, первый и второй входы первой, десятой и восемнадцатой, вторые входы пятой и одиннадцатой и первый вход девятнадцатой логических ячеек являются соответственно первым - девятым входами преобразователя, первые выходы восьмой и двадцать второй, первый и второй выходы двадцать третьей и второй выход двадцать четвертой логических ячеек являются соответственно пятым девятым выходами преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кодов | 1985 |

|

SU1264346A1 |

| Преобразователь кодов | 1985 |

|

SU1261122A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СРЕДЫ | 2003 |

|

RU2251141C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СРЕДЫ | 2006 |

|

RU2310902C1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ КМОП СУММАТОР | 2011 |

|

RU2454703C1 |

| Конвейерное устройство для умножения шестнадцатиразрядных чисел | 1984 |

|

SU1291970A1 |

| Ассоциативный запоминающий элемент | 1982 |

|

SU1057988A1 |

| Преобразователь параллельного унитарного кода в дифференциально-разностный код | 1988 |

|

SU1647907A1 |

| Счетчик адресации для прямого доступа к памяти | 1986 |

|

SU1388879A1 |

| Блок поиска информации для ассоциативного запоминающего устройства | 1982 |

|

SU1049973A1 |

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - упрощение преобразователя. Преобразователь содержит логические ячейки. Логическая ячейка содержит элемент ИЛИ и элемент И. Преобразователь кодов является многопороговым логическим элементом, реализующим на выходах пороговые функции с порогами, равными порядковым номерам выходов, от числа переменных, равного числу входов преобразователя. 2 ил.

фие. 1

| Преобразователь кодов | 1985 |

|

SU1261122A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь кодов | 1985 |

|

SU1264346A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-01-15—Публикация

1988-03-29—Подача