со

00 00 00

со

Изобретение относится к вычислительной технике и может быть применено для блочной передачи информации при прямом доступе к памяти, Цель изобретения - расширение функциональных возможностей за счет обеспечения побайтовой передачи информации в память и расширения адресного пространства при прямом доступе к памяти,

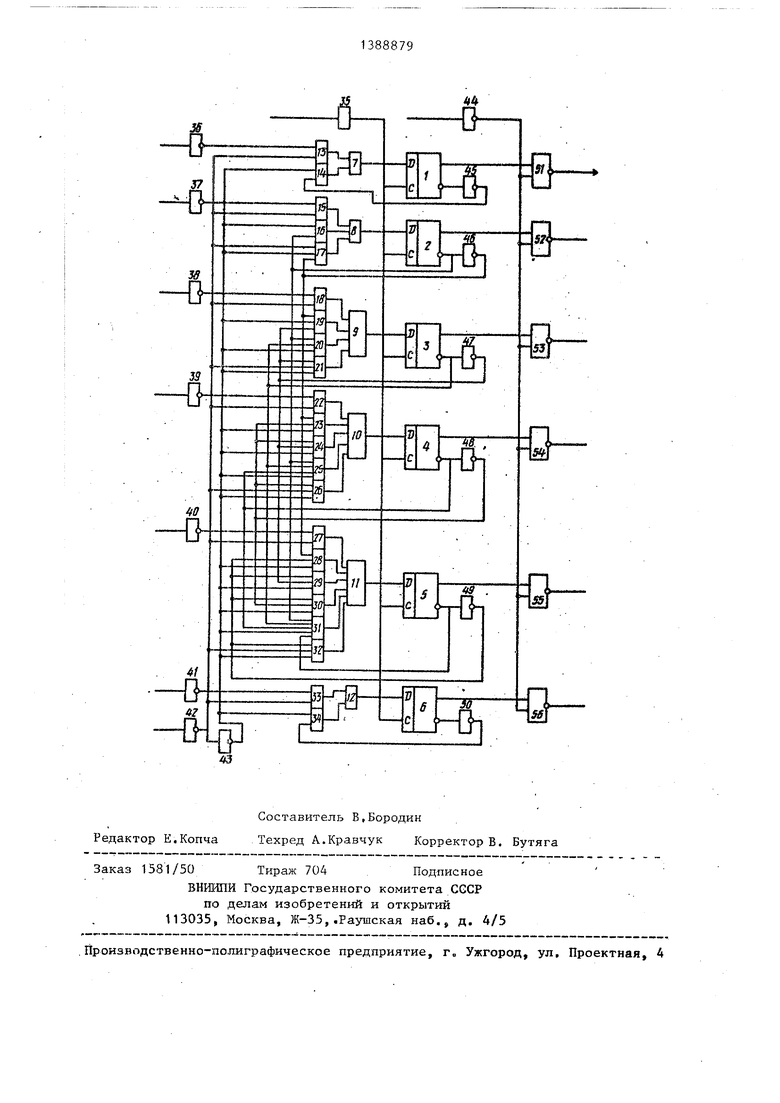

На чертеже изображена структурная схема счетчика адресации для прямого доступа к памяти.

Счетчик содержит шесть триггеров 1-6, шесть элементов 7-12 НЕ, двадцать два элемента 13-34 И, формирователь 35 импульсов,, выполненный на элементе И, пятнадцать элементов 36-50 НЕ и шесть магистральных передатчиков 51-56,

Высокий уровень сигнала на входе разрешения прямого доступа устанавливает выходы магистральных передатчиков 51-56 в высокоимпедансное состояние. При низком уровне сигнала на входе разрешения прямого доступа разрешается прохождение адреса для прямого доступа с выходов триггеров 1-6 через магистральные передатчики 51-56,

Информация, содержащаяся в разряде АДОО, указывает на выполнение операции с младшим байтом при низком логическом уровне сигнала АДОО или старшим байтом при высоком логическом уровне сигнала на линии АДОО, Таким образом, информация, содержащаяся в этом разряде, должна быть передана без изменения в течение всего цикла блочной передачи.

Для организации блочной передачи по 16-ти адресам необходимо четыре разряда счетчика адресации.

Разряд АД05 также передается без изменения в течение половины цикла адресации для прямого доступа к памяти и служит для расширения адресного пространства.

Количество адресуемых ячеек памя определяется количеством импульсов, поступающих на вход синхронизации и максимально может составлять 16 адресов.

Начальный адрес каждой передачи информации при прямом доступе к памяти определяется информацией, содежащейся на шинах А,Ц(05-00), защелкиваемой установкой из низкого логиче кого уровня в высокий логический уровень сигналов на входах синхронизации и разрешения счета.

Для организации блочного режима передачи прямого доступа к памяти необходимо наращивание адресов от исходного блоками дважды по 16, Блочный режим передачи информации существенно экономит время, необходимое для обновления содержимого памяти, так как для обращения к 32-м последовательным ячейкам памяти необходимо вырабатывать исходный адрес только г один раз,Для осуществления действия по нарагциванию адресов применяется предлагаемый счетчик адресации для прямого доступа памяти. Информация на шине АД05 при низком логическом 0 уровне обеспечивает адресацию к первым 16-ти адресам, при высоком логическом уровне - к последующим 16-ти адресам,

5 Формула изобретения

Счетчик адресации для прямого доступа к памяти, содержащий четыре триггера, шесть элементов НЕ, двенадцать элементов И, инверсные вько- ды с первого по четвертый триггеров соединены с входами с первого по четвертый элементов НЕ соответствен но, выход первого элемента НЕ соединен с первым входом первого элемента И, выход второго элемента НЕ сое-- динен с первыми входами с второго по пятый элементов И, .выход третьего элемента НЕ соединен с первыми входами с шестого по йосьмой элементов И и вторым входом третьего элемента И, выход четвертого элемента НЕ соединен с первыми входами девятого и .десятого элементов И и вторыми входами четвертого и седьмого элементов И, инверсный вьпсод четвертого триггера соединен с первыми входами одиннадцатого и двенадцатого элемен- тов И, отличающийся тем, что, с целью расширения функциональных возможностей за счет обеспечения побайтовой передачи информации в память и расширения адресного пространства при прямом доступе к памяти, в него введены два триггера, шесть магистральных передатчиков, формирователь импульса, шесть элементов ИЛИ, десять элементов И, одиннадцать элементов НЕ, вход синхрони0

5

0

5

0

5

зации счетчика через формирователь импульсоа соединен с входами синхронизации с первого по шестой Триггеров, прямые выходы которых соединены с информационными входами с первого по шестой магистральных передатчиков соответственно, выходы которых являются выходами счетчика, вход разрешения прямого доступа счетчика через пятый элемент НЕ соединен с входами управлением передачей с первого по шестой магистральных передатчиков, инверсный выход пятого триггера соединен с вторым входом двенадцатого элемента И, инверсный выход шестого, триггера через шестой элемент НЕ соединен с первым входом тринадцатого элемента И, инверсньй выход пятого триггера через седьмой элемент НЕ соединен с первым входом четырнадцатого элемента И и вторыми входами пятого, восьмого и десятого элементов И, инверсный выход второго триггера соединен с первыми входами пят- надцатого и шестнадцатого элементов И, вторым входом одиннадцатого элемента И, и третьим входом двенадцатого элемента И инверсный выход третьего триггера соединен с вторым входом шестнадцатого элемента И, третьим входом одиннадцатого элемей- та И и четвертым входом двенадцатого элемента И, выходы с восьмого по тринадцатый элементов НЕ являются информационными входами счетчика, выходы с восьмого по трйнадцатьй элементов НЕ соединены с первыми входами с семнадцатого по двадцать второй элементов И соответственно, выходы с первого по шестой элементов ИПН .соединены с информационными входами с первого по шестой триггеров соответственно, выходы первого .и семнадцатого элементов И соединены с первым и вторым входами первого элемента lUiH соответственно, выходы второго, пятнадцатого и восемнадцатого элементов И соединены с первого по третий входами второго элемента Ш1И соответственно, выходы третьего, шестого, шестнадцатого и девятнадцатого элементов И соединены с первого по четвертый входами третьего элемента ШШ соответственно, выходы четвертого седьмого, девятого, одиннадца- ,того и двадцатого элементов И соединены с первого по пятый входами четвертого элемента ШШ соответственно, выходы пятого, восьмого, десятого, двенадцатого, четырнадцатого и двадцать первого элементов И соединены с первого по шестой входами пятого элемента ИЛИ соответственно, выходы тринадцатого и двадцать второго элементов И соединены с первым и вторым входами шестого элемента ИЛИ, вход разрешения счета счетчика через четырнадцатый элемент НЕ соединен с входом пятнадцатого элемента НЕ, вторыми входами второго, шестого, девятого, четырнадцатого элементов И и вторыми входами с семнадцатого по двадцать второй элементов И, выход пятнадцатого элемента НЕ соединен с вторыми входами первого, тринадцатого и пятнадцатого элементов И, третьими входами с второго по десятый элементов И, третьими входами четырнадцатого и шестнадцатого элементов И, четвертым входом одиннадцатого элемента И и пятым входом двенадцатого элемента И,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1524061A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИЗОБРАЖЕНИЯ В ЭВМ | 2003 |

|

RU2256210C2 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| ТЕПЛОВИЗОР НА ОСНОВЕ "СМОТРЯЩЕЙ" МАТРИЦЫ ФОРМАТА 256×256 | 2008 |

|

RU2382516C2 |

| Запоминающее устройство | 1984 |

|

SU1243033A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| МИКРОЭВМ | 1994 |

|

RU2108619C1 |

| ТРЕХФАЗНЫЙ БЕСТРАНСФОРМАТОРНЫЙ НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 2020 |

|

RU2758443C1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

Изобретение относится к вычислительной технике, в частности для передачи информации при прямом доступе к памяти. Цель изобретения - расширение функциональных возможностей счетчика адресации зй счет обеспечения побайтовой передачи информации в память и расширения адресного пространства при адресации прямого доступа к памяти. Счетчик содержит шесть триггеров, шесть магистральных передатчиков, элементы И, ИЛИ и НЕ.- Счетчик предназначен для использования в устройствах, имеющих прямой доступ к памяти. Для согласования с каналом микроЭВМ магистральные передатчики имеют три состояния на выходе. Счетчик позволяет производить байтовую передачу информации. 1 ил.

Авторы

Даты

1988-04-15—Публикация

1986-09-10—Подача