Изобретение относится к импульс- ной технике и предназначено для использования в многоуровневых арифметических устройствах с инжекционным питанием.

Цель изобретения - расширение функциональных возможностей устройства, заключающееся в одновременном вьтолнении операций сложения и вычитания .

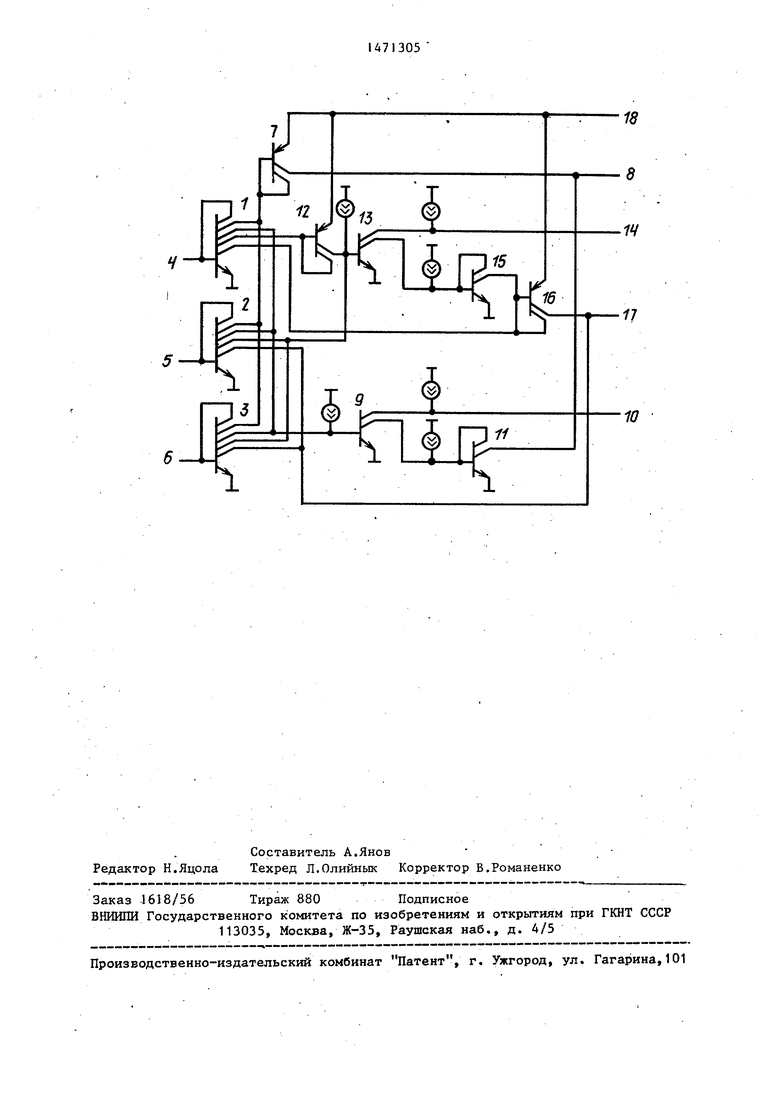

На чертеже приведена электрическая функциональная схема инжекцион- ного сумматора-вычитателяо

Инжекционньй сумматор-вычитатель содержит входные п-р-д-транзисторы 1-3, включенные по схеме токового отражения, базы которых соединены с входными шинами 4-6 операндов со- ответственно, а первые коллекторы с базой первого р-п-р-транзистора 7, коллектор которого соединен с выходной шиной 8 суммы, вторые коллекторы транзисторов 1-3 соединены с базой первого п-р-п-транзистора 9,первый коллектор которого соединен с выходной шиной 10 переноса, а второй - с базой второго п-р-п-транзистора 11, коллектор которого соединен с коллектором транзистора 7 и с выходной шиной 8 суммы, третий коллектор транзистора 1 соединен .с базой второго р-п-р-транзистора 12, коллектор которого соединен с третьими коллекторами транзисторов 2 и 3 и с базой третьего п-р-п-транзистора 13, пер- .вый коллектор которого соединен с выходной шиной 14 заема, а второй - с базой ч.етвертого п-р-п-транзисто

N-iA.

СО

о ел

pa 15, коллектор которого соединен с четвертым коллектором транзистора 1 и с базой третьего р-п-р-транзисто- ра 1.6, коллектор которого соединен с четвертыми коллекторами транзисторов 2 и 3 и с выходной шиной 17 разности, эмиттеры транзисторов 7, 12 и 16 соединены с шиной 18 питания В базы транзисторов 9, П, 13и15и в вы-. ходные шины 10 и 14 задаются токи инжектора, равные трем с половиной, четырем, половине, четырем, одному и одному уровню тока соответственно.

Различные уровни тока, задаваемые инжектором, обеспечиваются соответствующим соотнош ием площадей коллектора и эмиттера инжекционного р-п-р- транзисторао Транзистор, включенный по схеме токового отражения, пред- ставляет собой многоколлекторную транзисторную структуру, в которой соотношением площадей выходного коллектсра и коллектора обратной связи обеспечивается коэффициентом передачи тока, равным единице, то .есть выходной ток равен входному

Сумматор-вычитатель работает следующим образом.

Алгоритм реализации функций суммы Х переноса р разности W и заема V над операндами А,В,С имеет следующий вид:

21 А+В+С

при (А+В+С)б 31„;

р О

:Z. А+В+С-4 р - 1

W А-(В+С) V О

при (А+В+С) 31 ;

при Аь (В+С);

W (А+4)-(В+С)

V Г

при А(В+С),

где I - единичный уровень тока.

Операнды подаются на входные шины , 4-6,, На соединенных первых коллекторах входных транзисторов 1-3 происходит их суммирование. Ток, равньй сумме входных токов, отводится этими коллекторами от базы транзистора .7. А так как этот транзистор включен по схеме токового отражения, точно такой же ток выдается-в выходную шину 8 суммы. Такой же по величине -ток отводится соединенными вторыми коллек;:

торами входных транзисторов 1-3 от базы транзистора 9, включенного по схеме порогового детектора. Если этот отводимый ток будет, меньше или- равен 3 IP, транзистор 9 останется открытым. При этом он шунтирует своим первым коллектором выходную шину 10 переноса, а вторым - базу транзистора 11, включенного по схеме токового отражения, коллектор которого, соединенньй с выходной шиной 8 суммы, не оказывает никакого влияния на величину тока, протекающего по ней. Если же сумма входных токов будет больше или равна 41, транзистор 9 закрывается, так как в его базу инжектором задается ток,;, равный 3,5 1д, который в этом случае полностью отводится входными транзисторами. При этом в шину 10 переноса инжектором задается ток, равный I

открывается ранее шунтируе

мый транзистором 9 транзистор 11 и отводит от выходной шины 8 суммы ток, равньй 4 1. Таким образом, сразу осуществляется реализация алгоритма сложения и переноса.

Канал вычитания работает следующим образо м.

На входные шины 4-6 подаются операнды уменьшаемого, вычитаемого и заема соответственно. Ток, равньй по величине входному току умень- шаемого, поданного во входную шину 4, отводится четвертым коллектором входного транзистора 1 от базы транзистора 16, включенного по схеме токового отражения. Следовательно, такой же по величине ток будет задаваться в выходную шину 17 разности, откуда через коллекторы входных транзисторов 2 и 3 отводится ток, равньй сумме операндов, поступающих на шины 5 и 6 (вычитаемое и заем).В результате в выходной шине 17 формируется ток, равный разности входных операндов (B+C).. Ток, равньй по величине входному току, поступившему во входную шину 4, отводится входным транзистором 1 от базы транзистора 12, включенного по схеме токового отражения. Следовательно, такой же ток будет задаваться егр коллектором в базу транзистора 13, включенного по схеме токового детектора. От его базы также отводится через коллекторы транзисторов 2 и 3 ток, равньй сумме

вычитаемого и заема, а инжектором задается ток, равный 0,5 Т. При этом, если А-СВ+С) О, транзистор 13 открывается и своими коллекторами шунтирует выходную шину заема (V 0) и базу транзистора 15, последний закрывается.

Если А-(В+С) О, транзистор 13 закрывается, в выходную шину 14 инжектор задает ток, равньй I(,(), а открывшийся транзистор 15 отводит от базы транзистора 16 дополнительно ток, равньй 4 1. Этим достигается добавление к току уменьшаемого дополнительного тока, равного 4 1.Таким образом, реализуется функция вычитания W(A+4)-(B+C).

Формула изобретения 20

15

10

20

71305

в выходную шину переноса инжектором задаются токи, равные трем с половиной, четырем и одному уровню тока соответственно, эмиттер первого р-п-р- транзистора соединен с шиной питания, отличающийся тем , что, с целью расширения функциональных возможностей, в него введены второй р-п-р-транзистор, включенный по схеме токового отражения, база которого соединена с третьим коллектором первого входного п-р-п-транзистора, третий п-р-п-транзистор, включенньй 15 по схеме порогового детектора, база которого соединена с коллектором второго р-п-р-транзистора и с третьими коллекторами второго и третьего входных п-р-п-транзисторов, а первьй коллектор - с выходной шиной заема, чет- вертьй п-р-п-транзистор, включенньй

| название | год | авторы | номер документа |

|---|---|---|---|

| Инжекционный сумматор | 1988 |

|

SU1539992A1 |

| Одноразрядный сумматор-вычитатель | 1987 |

|

SU1424013A1 |

| Четырехуровневый сумматор-вычитатель | 1987 |

|

SU1422396A1 |

| Одноразрядный сумматор-вычитатель | 1986 |

|

SU1335982A1 |

| Мажоритарный элемент И @ Л типа | 1986 |

|

SU1406777A1 |

| Четырехуровневый однозарядный сумматор | 1984 |

|

SU1236463A1 |

| Нормализатор уровня | 1987 |

|

SU1429314A1 |

| Четырехзначный умножитель элементов поля Галуа GF(2 @ ) | 1990 |

|

SU1737443A1 |

| Одноразрядный сумматор на инжекционных элементах | 1985 |

|

SU1275430A1 |

| Двухразрядный двоичный умножитель инжекционного типа | 1983 |

|

SU1150626A1 |

Изобретение относится к импульсной технике и предназначено для использования в многоуровневых арифметических устройствах с инжекционным питанием. Цель изобретения - расширение функциональных возможностей. Инжекционный сумматор - вычитатель содержит три входных п-р-п-транзистора, включенных по схеме токового отражения, три р-п-р-транзистора и четыре п-р-п-транзистора. Введение второго и третьего р-п-р-транзисторов, новых связей, а также задание инжектором соответствующих уровней тока позволяют реализовать на выходах функции сложения и вычитания. 1 ил.

Инжекционньй сумматор-вычитатель, содержащий три входных п-р-п-транзистора и первый р-п-р-транзистор, включенные по схеме токового отражения, первый п-р-п-транзистор, включенньй по схеме токового детектора, второй п-р-п-транзистор, включенньй по схеме токового отражения, первые коллекторы входных п-р-п-транзисторов соединены с базой первого р-п-р-транзистора, а вторые коллекторы - с базой первого п-р-п-транзистора, первьй коллектор которого соединен с выходной шиной переноса, а второй .- с базой второго п-р-п-транзистора, коллектор которого соединен с коллектором первого р-п-р-транзистора и с вы- шиной суммы, в базу первого и второго п-р-п-транзисторов, а также

по схеме токового отражения, база которого соединена с вторым коллектором третьего п-р-п-транзистора, третий р-п-р-транзистор, включенньй по схеме токового отражения, база которого соединена с коллектором чет- верторого п-р-п-транзистора и с четвертым коллектором первого входного

п-р-п-транзистора, а коллектор - с четвертыми коллекторами второго и третьего входных п-р-п-транзисторов и с выходной шиной разности, в базу третьего, четвертого п-р-п-транзисторов и в выходную шину заема инжектором задаются токи,равные половине, четырем и одному уровню тока соответственно, змиттеры второго и третьего р-п-р-транзисторов соединены с шиной питания.

| Четырехуровневый сумматор-вычитатель | 1987 |

|

SU1422396A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Tich Dao Threshold and it applications to binary Symmetric Functions and multivalued logic | |||

| - IEEE Journal of Solid-State Circuits, 1977, vol | |||

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

1989-04-07—Публикация

1987-02-16—Подача