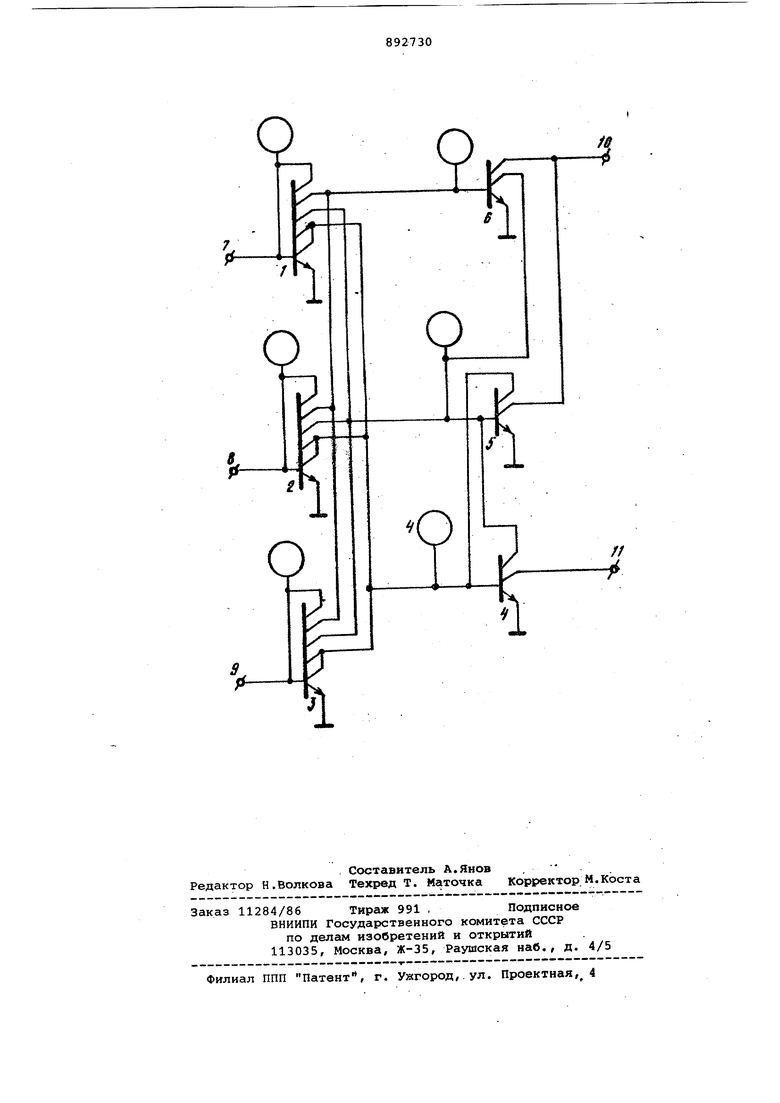

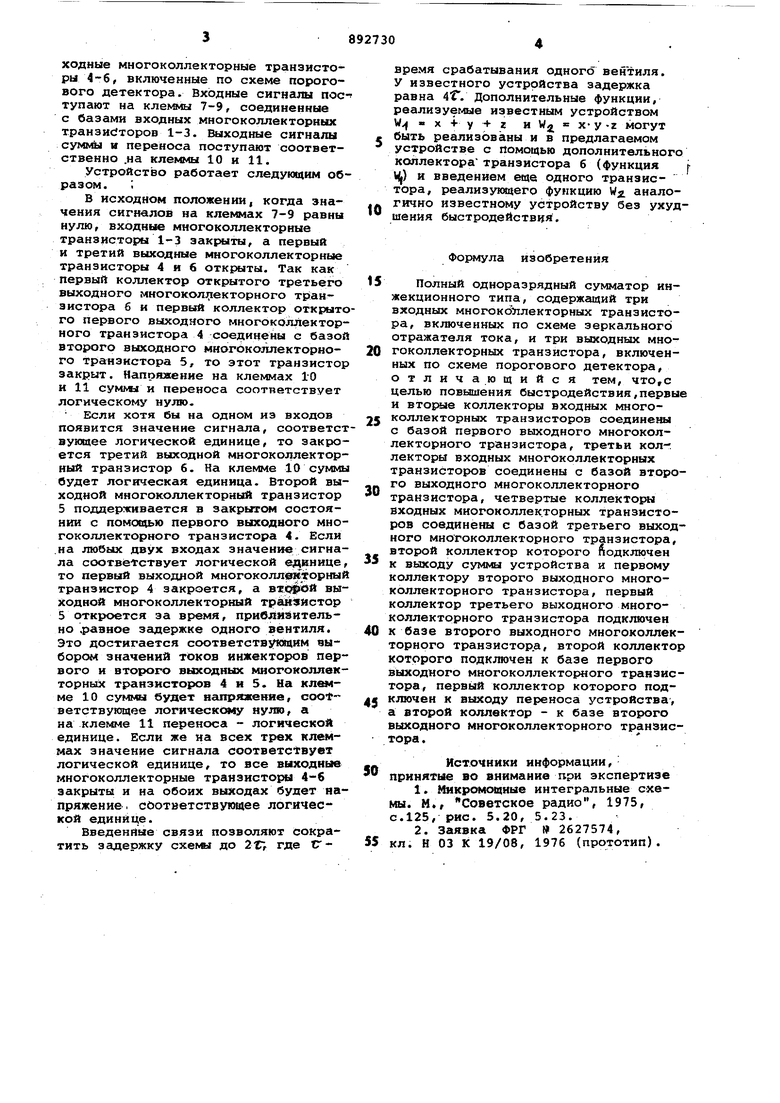

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных уст ройствах . Известны сумматоры, построенные на двоичных элементах интегральной инжекционной логики 1 Недостатками известных сумматоров являются большая сложность и низкое быстродействие. Известен также cyNwaTOp, содержащий три многоколлекторных транзистора, включенных по схегле зеркального отражателя тока, и четыре транзистора, включенных по схеме порогового детектора 2. Однако устройство имеет низкое быстродействие. Цель изобретения - повышение быст родействия. Для достижения поставленной цели в устройстве, содержащем три входных многоколлекторных транзистора,включенных по схеме зеркального отражате ля тока, и три выходных многоколлекторных транзистора, включенных по схеме порогового детектора, первые и вторые коллекторы входных многокол лекторных транзисторов соединены с базой первого выходного многоколлек торного транзистора, третьи коллекторы входных многоколлекторных транзисторов соединены с базой второго выходного многоколлекторного транзистора, четвертые коллекторы входных многоколлекторных транзисторов соединены с базой третьего выходного многоколлекторного TtiaH3HCTOpa, второй коллектор которого подключен к выходу суммы устройства и первому коллектору второго выходного многоколлекторного транзистора, первый коллектор третьего выходного многоколлекторного транзистора подключен к базе второго выходного многоколлекторного транзистора, второй коллектор которого подключен к базе первого выходного многоколлекторного транзистора, первый коллектор которого подключен к выходу переноса устройства, а второй коллектор. - к базе второго выходного многоколлекторного транзистора. На чертеже представлена принципиальная схема полного одноразрядного сумматора. Устройство содержит входные многоколлекторные транзисторы 1-3, включенные по схеме з.еркапьного отражателя тока, первый, второй, третий выходные многоколлекторные транзисторы 4-6, включенные по схеме порогового детектора. Входные сигналы поступают на кле№ш 7-9, соединенные с базами входных многоколлекторных транзис торов 1-3. Выходные сигналы cyMNOd и переноса поступают соответственно .на клеммы 10 и 11.

Устройство работает следующим образом. :

в исходном положении, когда значения сигналов на клеммах 7-9 равны нулю, входнью многоколлекторные транзисторы 1-3 закрыты, а первый и третий выходные многоколлекторные транзисторы 4 и б открыты. Так как первый коллектор открытого третьего выходного многоколлекторного транзистора б и первый коллектор открытого первого выходного многокОллекторного транзистора 4 соединены с базой второго выходного многбколлекторного транзистора 5, то этот транзистор закрыт. Напряжение на клеммах 10 и 11 сумки и переноса соотиетствует логическому нулю,

Если хотя бы на одном из входов появится значение сигнала, соответствующее логической единице, то закроется третий выходной многоколлекторный транзистор 6. На клемме 10 суммы будет логическая единица. Второй выходной многоколлекторный транзистор 5 поддерживается в закрытом состоянии с помощью первого выходного многоколлекторного транзистора 4. Если .на любых двух входах значение сигнала соответствует логической единице, то первый выходяой многоколлдаторный транзистор 4 закроется, а втО&Ой выходной многоколлекторный транзистор 5 откроется за время, приблизительно .равное задержке одного вентиля. Это достигается соответствующим выбором значений тОков инжекторов первого и второго выходных миогоколлекторных транзисторов 4 и 5. На 10 суммы будет нгшряжение, соответствующее логическому нулю, а на 11 переноса - логической единице. Если же на всех трех клеммах значение сигнала соответствует логической единице, то все выходные многоколлекторные транзисторы 4-6 закрыты и на обоих выходах будет напряжение . сйответствующее логической единице.

Введенные связи позволяют сократить задержку схемы до 2Т, где ТГвремя срабатывания одного вентиля. У известного устройства задержка равна 4f. Дополнительные функции, реализуемые известным устройством X + у + Z и W Ху-г могут быть реализованы и в предлагаемом устройстве с Помощью дополнительного коллектора транзистора б (функция JЦ) и введением еще одного транзистора, реализукяцего функцию W аналогично известному устройству без ухудшения быстродействияФормула изобретения

$ Полный одноразрядный сумматор инжекционного типа, содержащий три входных многоксЛтлекторных транзистора, вк/яоченных по схеме зеркального отражателя тока, и три выходных многоколлекторных транзистора, включенных по схеме порогового детектора, отличающийся тем, что,с целью повышения быстродействия,первые и втореое коллекторы входных многоколлекторн лх транзисторов соединены с базой первого выходного многоколлекториого транзистора, третьи кол-г лекторы входных многоколлекторных транзисторов соединены с базой второго выходного многоколлекторного транзистора, четвертые коллек±оры входных миогоколлек.торных транзисторов соединены с базой третьего выходного многоколлекторного транзистора, второй коллектор которого подключен к выходу суммы устройства и первому коллектору второго выходного многоколлекторного транзистора, первый коллектор третьего выходного многоколлекторного транзистора подключен к базе второго выходного многоколлекторного транзистора, второй коллектор которого подключен к базе первого выходного многоколлекторного транзистора, первый коллектор которого под4 ключей к выходу переноса устройства, а второй коллектор - к базе второго выходного многоколлекторного транзистора.

Источники информации,

принятые во внимание при экспертизе

1.Микромодные интегральные схемы. М., Советское радио, 1975,

с.125, рис. 5.20, 5.23.

2.заявка ФРГ 2627574,

кл. Н 03 К 19/08, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель двухразрядных двоичных чисел инжекционного типа | 1980 |

|

SU894704A1 |

| Одноразрядный сумматор-вычитатель | 1987 |

|

SU1424013A1 |

| Умножитель четверичный инжекционного типа | 1980 |

|

SU928651A1 |

| Четырехуровневый одноразрядный сумматор | 1982 |

|

SU1095174A1 |

| Одноразрядный комбинационный сумматор | 1981 |

|

SU981995A1 |

| Одноразрядный сумматор-вычитатель | 1986 |

|

SU1335982A1 |

| Многопороговый логический элемент | 1983 |

|

SU1132366A2 |

| Одноразрядный сумматор на инжекционных элементах | 1985 |

|

SU1275430A1 |

| Универсальный многозначный логический элемент инжекционного типа /его варианты/ | 1980 |

|

SU890558A1 |

| Четырехзначный умножитель элементов поля Галуа GF(2 @ ) | 1990 |

|

SU1737443A1 |

Авторы

Даты

1981-12-23—Публикация

1980-04-25—Подача