(i-l)p Lf ( 25

сл

4;; со со

4

о ел

31499405

сигналов управления сдвигом. Эта цель достигается путем организации в управляющем регистре внутренней асинхронной времяформующей цепи,

состоящей в каждом разряде из триггера 1, усилителя 5 и логического элемента 10. Такая цепь производит асинхронное формирование требуемых по длительности сигналов, управляю- JQ щих сдвигом в элементах памяти накопителя ЗУ. При этом, во-первых, импульсы на выходах сдвига управляющего

регистра уплотнены, во-вторых, во .времяформирзтощей цепи содержится идетификатор задержки переключения элементов памяти 28, благодаря чему при отклонении питающих инжекционных токов время срабат шания инжекционных элементов памяти хотя и изменяется, но соответственно изменяется и длительность формируемых импульсов, оставаясь всегда такой, какая необходима для надежного переключения элементов памяти. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

| Регистр сдвига для буферного запоминающего устройства | 1985 |

|

SU1432609A1 |

| Распределитель импульсов для многотактового запоминающего устройства на регистрах сдвига | 1978 |

|

SU752488A1 |

| Регистр для буферного запоминающего устройства | 1984 |

|

SU1170511A1 |

| Одновибратор | 1990 |

|

SU1750027A1 |

| Управляющий регистр для буферного запоминающего устройства | 1984 |

|

SU1231536A1 |

| Графический дисплей с контролем | 1984 |

|

SU1249526A1 |

| Ячейка памяти для регистра сдвига | 1978 |

|

SU752491A1 |

| Полупроводниковое запоминающее устройство | 1983 |

|

SU1142861A1 |

| Графический дисплей с контролем | 1988 |

|

SU1509929A1 |

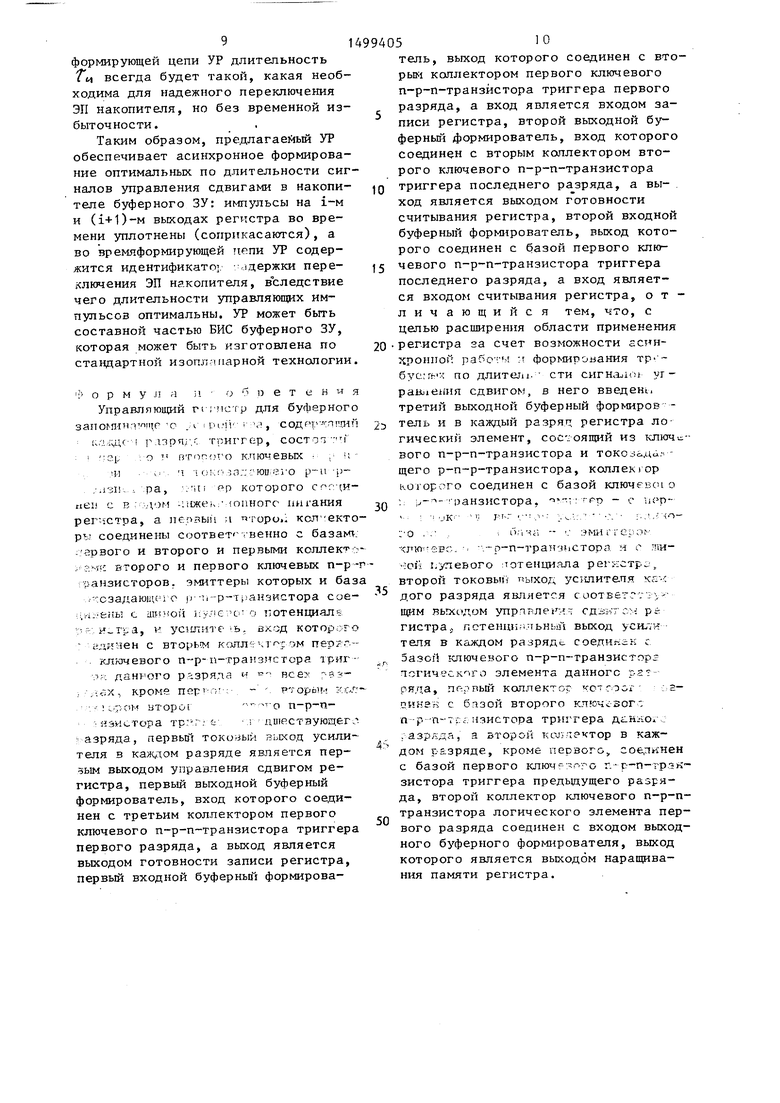

Изобретение относится к вычислительной технике и может быть использовано в БИС буферных запоминающих устройств типа FIFO на совмещенных транзисторных структурах (инжекционных схемах). Целью изобретения является расширение области применения регистра за счет обеспечения возможности асихронной работы и формирования требуемых по длительности сигналов управления сдвигом. Эта цель достигается путем организации в управляющем регистре внутренней асинхронной времяформующей цепи, состоящей в каждом разряде из триггера 1, усилителя 5 и логического элемента 10. Такая цепь производит асинхронное формирование требуемых по длительности сигналов, управляющих сдвигом в элементах памяти накопителя ЗУ. При этом, во-первых, импульсы на выходах сдвига управляющего регистра уплотнены, во-вторых, во времяформирующей цепи содержится идентификатор задержки переключения элементов памяти 28, благодаря чему при отклонении питающих инжекционных токов время срабатывания инжекционных элементов памяти хотя и изменяется, но соответственно изменяется и длительность формируемых импульсов, оставаясь всегда такой, какая необходима для надежного переключения элементов памяти. 3 ил.

Изобретение относится к вычислительной технике и может бьп ь использовано в буферных запоминаюп их уст- ройствах (ЗУ) типа FIFO на совмещенных п-р-п-р-транзисторных структурах (инжекционных схемах).

Цель изобретения - расширение области применения регистра за счет возможности асинхронной работы и формирования требуемых по длительности сигналов управления сдвигом.

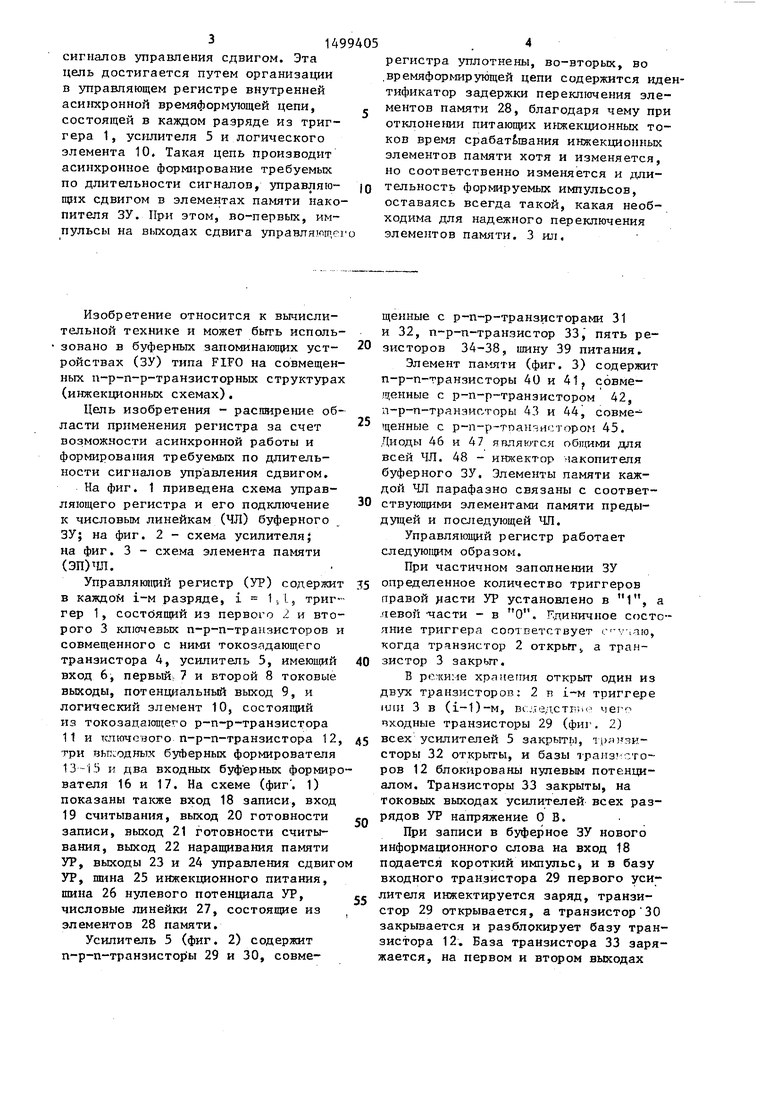

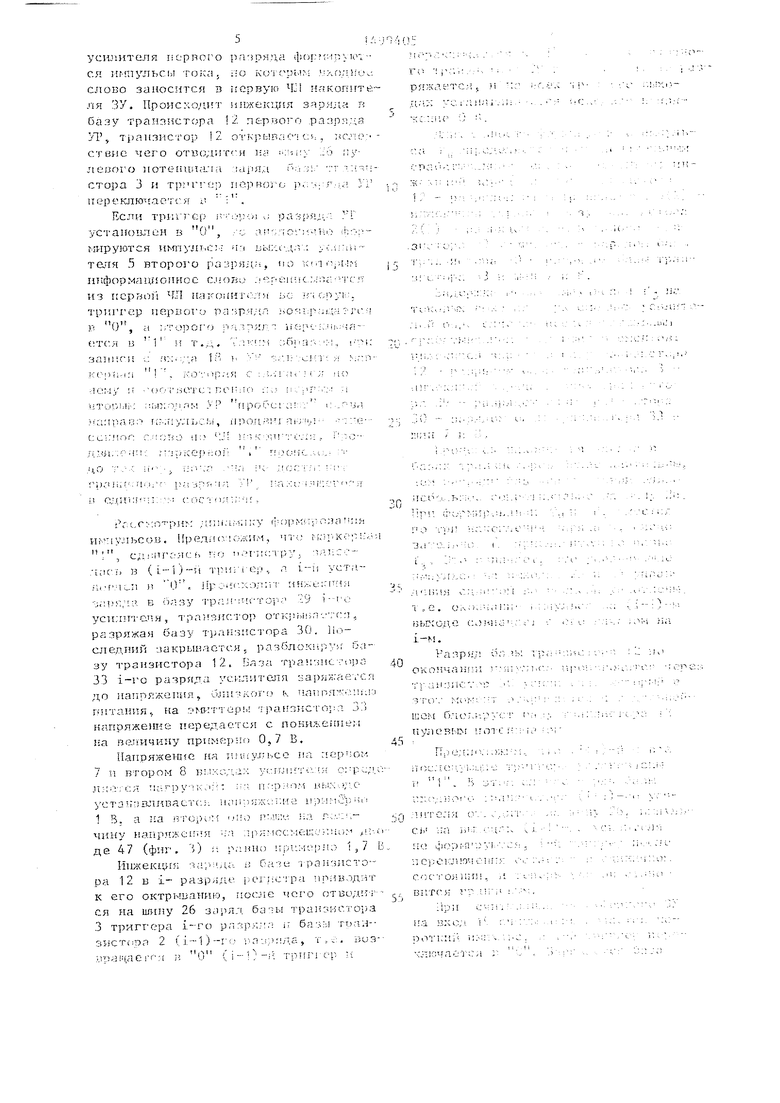

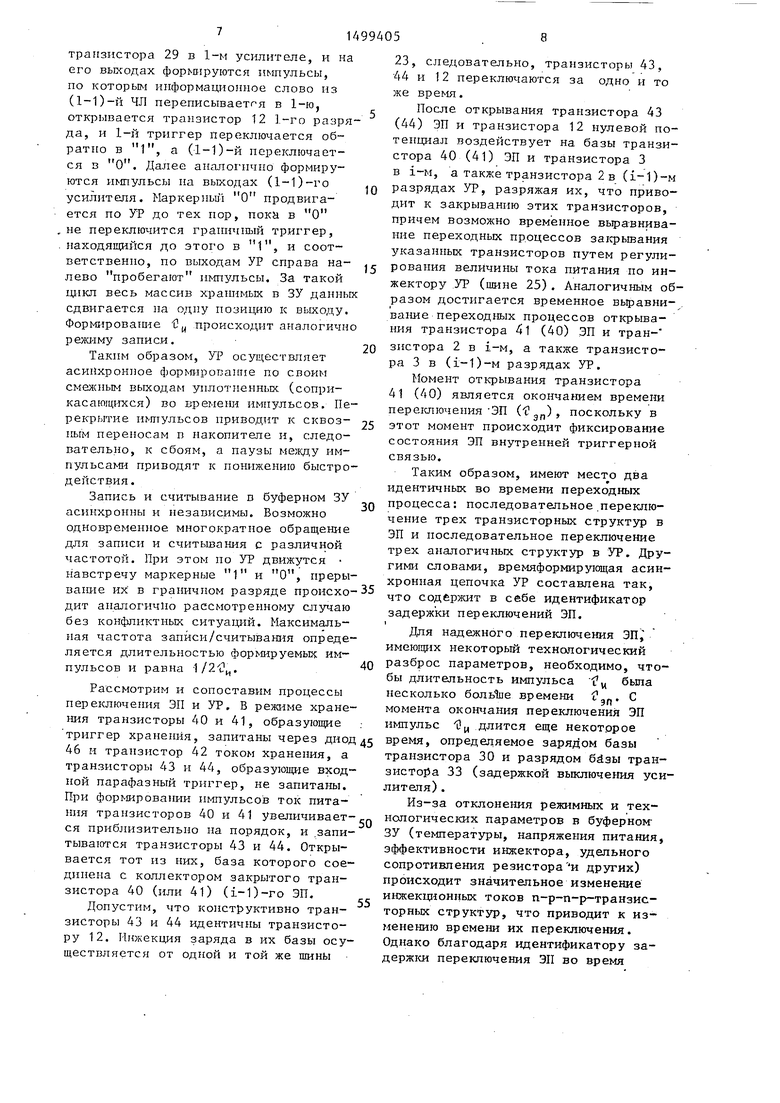

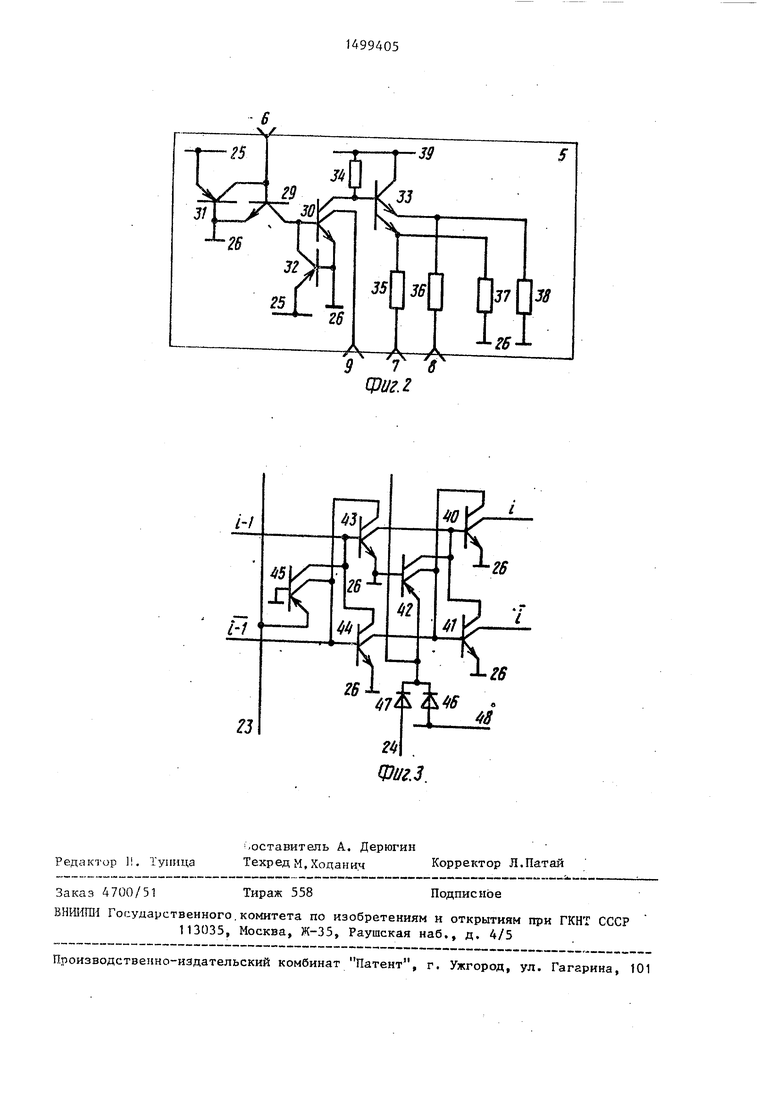

На фиг. 1 приведена схема управляющего регистра и его подключение к числовым линейкам (ЧЛ) буферного ЗУ; на фиг. 2 - схема усилителя; на фиг. 3 - схема элемента памяти

(эп)та.

Управляюнщй регистр (УР) содержит в каждом i-M разряде, i I/L, триггер 1, состоящий из первого 2 и второго 3 ключевых п-р-п-транзисторов и совмещенного с ними токозадающего транзистора 4, усилитель 5, имеющий вход 6, первый; 7 и второй 8 токовые выходы, потенциальный выход 9, и логический элемент 10, состоящий из токозада1оп(его р-п-р-транзистора 11 и тслючсвого п-р-п-транзистора 12 три вькодньш буферных формирователя 13-15 к два входных буф ерньк формирователя 16 и 17. На схеме (фиг . 1) показаны также вход 18 записи, вход 19 считывания, выход 20 готовности записи, выход 21 готовности считывания, выход 22 наращивания памяти УР, выходы 23 и 24 управления сдвиг ЗТ, Ш1на 25 иижекционного питания, шина 26 нулевого потенциала УР,

числовые линейки 27, состоящие из элементов 28 памяти.

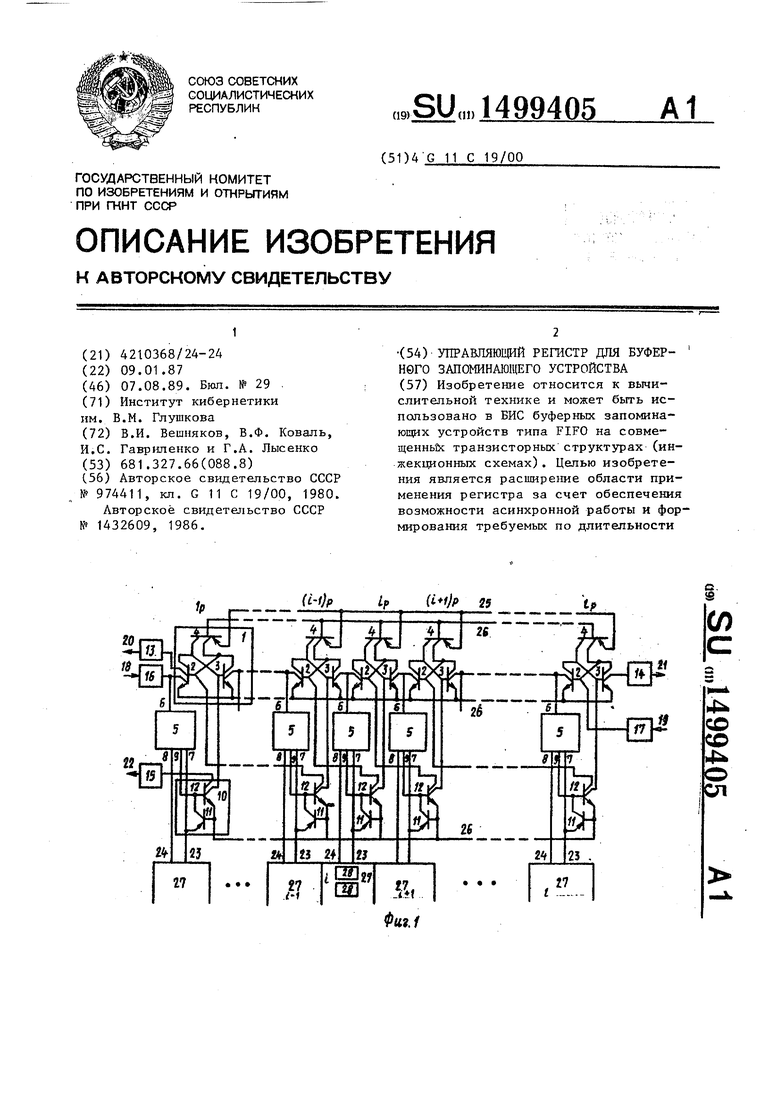

Усилитель 5 (фиг. 2) содержит п-р-п-транзистор ы 29 и 30, совме5

0

5 0 З п

щенные с р-п-р-транзисторами 31 и 32, п-р-п-транзистор 33, пять резисторов 34-38, шину 39 питания.

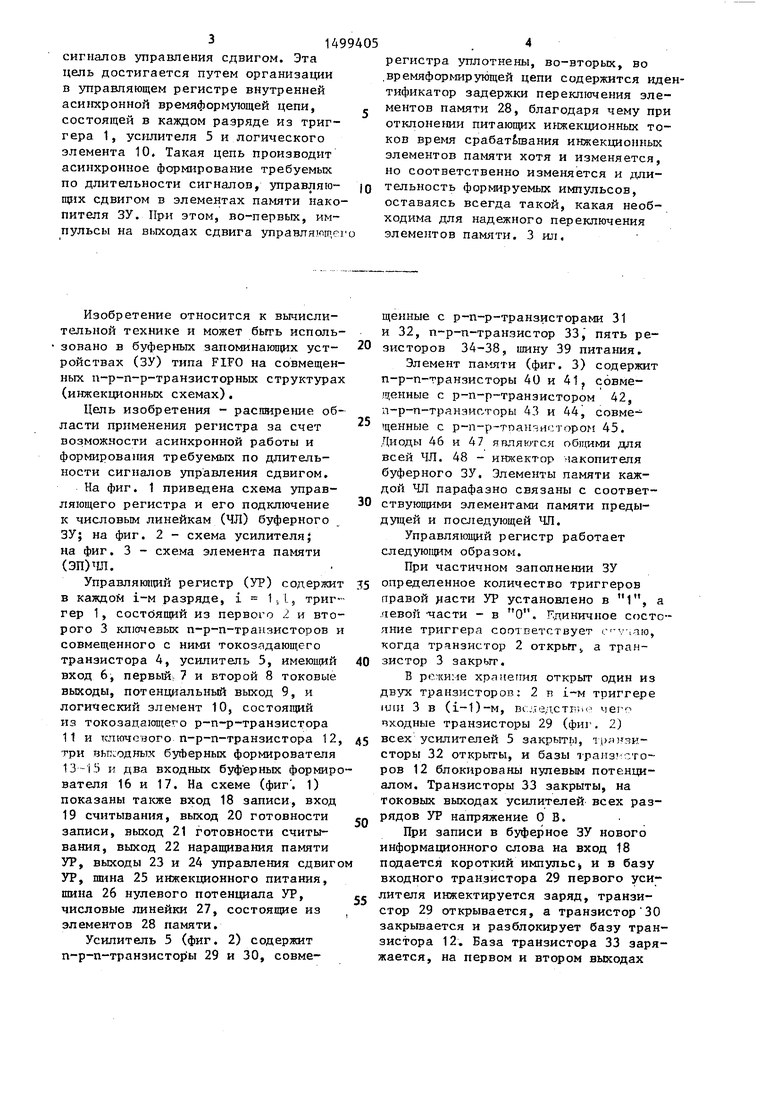

Элемент памяти (фиг. 3) содержит п-р-п-транзисторы 40 и 41 совме- ценные с р-п-р-транзистором 42, п-р-п-транзисторы 43 и 44, совмещенные с p-n-p-rnaHSHCTopof 45. Диоды 46 и 47 яиляются для всей ЧЛ. 48 - инжектор яакопителя буферного ЗУ. Элементы памяти каждой ЧЛ парафазно связаны с соответствующими элементами памяти предыдущей и последующей ЧЛ.

Управляющий регистр работает следующим образом.

При частичном заполнении ЗУ определенное количество триггеров правой ;насти УР установлено в 1, а левой части - в О, Единичное состояние триггера соответствует с -,аю, когда транзистор 2 открыт а транзистор 3 закрьп .

В режиме храиепия открыт один из двух транзисторов; 2 в i-м триггере Ш1И 3 в (1-1)-м, ви.гедст1 )Ч: чего входные транзисторы 29 (фиг, 2) всех усилителей 5 закрыты, 1рянзк- сторы 32 открыты, и базы транзисторов 12 блокированы нулевым потенциалом. Транзисторы 33 закрыты, на токовых выходах усилителей всех разрядов УР напряжение О В.

При записи в буферное ЗУ нового информационного слова на вход 18 подается короткий импульс и в базу входного транзистора 29 первого усилителя инжектируется заряд, транзистор 29 открывается, а транзистор 30 закрьшается и разблокирует базу транзистора 12. База транзистора 33 заряжается, на первом и втором выкодах

: асс;ап ри ; дииам;п;у фпрмчап:за а:;ь Иг.ч|ульсои. Ирел1(аожил1, лт;; rsai iKC ;: каа ;, сдапгаясь по arac i py тапсч- дас . в (L-i)-H TiMH i Kp, а ia ai уста- iii fa ;i л , Jip чаа;чо;1;г ;iH;-.e lairia

.;арада в оазу тра; чЧ1 -то ч1 i-aa ; усидитсия , тра. Гзистор .;а;:, разряжая базу транзистора -30, lici- следпий laKpLiHaoT Oi; разбло аа; у1- базу транзистора 12. База трамзис-дара 33 разряда усилителя зарялгаеч ся

до напряжения 5 6jHt ;Ko;ra) к Т1аппя а уа;| питания на :; МН 1 терь: ч(чанзястора За на.пряженне передастся с понил енн;; м На величину примерно 0,7 В.

Панряжеш е на 1ии1ул -,сс на аерпом

ся

устз п;)в:и-1састс;1 Haiianxuaaia iipi-iru.-;; ai 1 5. а на вторам Д о ад ;:е на л;лчч- чину нанряжсния ча ар;;; 1сс:ме ;:ч;аи):-- И аг де 47 (фиг. О и раино iipia-iaisHo 1,7 В Инжекния аарада iJ Oa -je транзлсто--

pa 12 в i- разряде i;eiaiC : pa привадит

к его октрьшанию, Hocjie лсг-о ОТБОД:ТГ Ся на шину 26 заря;|. ба ;ы транзистора 3 триггера i- го раарк.а. - к баз; Л ,н-- siiCTopa 2 ()-i4j ;1ааа; да, т.ч. воЗ i pai:i,aeia 4( i; I

10

транзистора 29 в 1-м усилителе, и на его выходах формируются импульсы, по которым ипформационное слово из (1-1)-и ЧЛ переписывается в 1-ю, открывается транзистор 12 1-го разряда, и 1-й триггер переключается обратно в 1, а (1-1)-й переключается в О. Далее аналогично формируются иьтульсы па выходах (1-1)-го усилителя. Маркерпьп О продвигается по У Р до тех пор, пока в О не переключится грапичпый триггер, находящийся до этого в 1, и соответственно, по выходам УР справа налево пробегают импульсы. За такой цикл весь массив хранимых в ЗУ данных сдвигается на одну позицию к выходу. Формирование f происходит аналогично режиму записи.

Таким образом, УР осуществляет асинхронное формиротзаН1 е по своим смежным выходам уплотненных (соприкасающихся) во времени импульсов. Перекрытие и myльcoв приводит к сквоз- 25

15

20

4 ж

т ж в н з

п

с

вательно, к сбоям, а паузы межд,у импульсами приводят к понижению быстродействия.

Запись и считывание в буферном ЗУ асинхронны и независимы. Возможно одновременное многократное обращение для записи и считьшания с различной частотой. При этом по УР движутся навстречу маркерные. 1 и О, прерывание их в граничном разряде происходит аналогично рассмотренному случаю без конфликтных ситуаций. Максимальная частота записи/считывания определяется длительностью формируемых импульсов и равна l/2 l p,.

Рассмотрим и сопоставим процессы переключения ЭП и УР. В режиме хранения транзисторы 40 и 41, образующие триггер хранения, запитаны через диод 46 и транзистор 42 током хранения, а транзисторы 43 и 44, образующие входной парафазный триггер, не запитаны. При формировании импульсов ток питания транзисторов 40 и 41 увеличивается приблизительно на порядок, и ,запи- тываются транзисторы 43 и 44. Открывается тот из них, база которого сое- динена с коллектором закрытого транзистора 40 (или 41) (i-1)-ro ЭП.

Допустим, что конструктивно транзисторы 43 и 44 идентичны транзистору 12. Иижекция заряда в их базы осуществляется от одпог и той же шины

0

5

5

0

0

0

5

45

50

5

23, следовательно, транзисторы 43, 44 и 12 переключаются за одно и то же время.

После открывания транзистора 43 (44) ЭП и транзистора 12 нулевой потенциал воздействует на базы транзистора 40 (41) ЭП и транзистора 3 в i-M, а также транзистора 2 в (i-1)-M разрядах УР, разряжая их, что приводит к закрыванию этих транзисторов, причем возможно временное выравнивание переходных процессов загфывания указанных транзисторов путем регулирования величины тока питания по инжектору УР (шине 25). Аналогичным образом достигается временное выравни- , вазше переходных процессов открывания транзистора 41 (40) ЭП и трав- зистора 2 в i-M, а также транзистора 3 в (i-1)-M разрядах УР.

Момент открывания транзистора 41 (40) является окончанием времени переключения ЗП (f

эп

) , поскольку в

этот момент происходит фиксирование состояния ЭП внутренней триггерной связью.

Таким образом, имеют два идентичных во времени переходных процесса: последовательное .переключение трех транзисторньк структур в ЭП и последовательное переключение трех аналогичных структур в УР, Другими словами, времяформиру1сяцая асинхронная цепочка УР составлена так, что содержит в себе идентификатор задержки переключений ЭП.

1

Для надежного переключения ЭП, имеющих некоторый технологический разброс параметров, необходимо, чтобы длительность импульса бьша несколько больЧпе времени , С момента око1гчания переключения ЭП импульс 1, длится еще некоторое время, определяемое зарядом базы транзистора 30 и разрядом бйэы транзистора 33 (задержкой выключения усилителя) .

Из-за отклонения режимных и технологических параметров в буферном- ЗУ (температуры, напряжения питания, эффективности инжектора, удельного сопротивления резистора и других) происходит значительное изменение инжек1щонных токов п-р-п-р-транзисторных структур, что приводит к изменению времени их переключения. Однако благодаря идентификатору за- держ1да переключения ЭП во время

формирующей цепи УР длительность Ti всегда будет такой, какая необходима для надежного переключения ЭП накопителя, но без временной избыточности.

Таким образом, предлагаейый УР обеспечивает асинхронное формирование оптимальных по длительности сил- налов управления сдвигами в накопителе буферного ЗУ: импульсы на i-м и (i+1)-M выходах регистра во времени уплотнены (соприкасаются), а во времяформирующей цепи УР содержится идентификато;. -мдержки переключения ЭП накопителя, вследствие чего длительности управляющих импульсов оптимальны. Y может быть составной частью БИС буферного ЗУ, которая может быть изготовлена по

стандартной изоплмиарной технологии.

; о р м у J а и о б D е т е н и я Управляющий Г1 гистр для буферного зaпo п т п 1rllP О ..v ги И i , содрр - оппотй

(1,.-;щс глзрпг,. триггер, состою - i

:2р - ВТГ1Г)Я О ключевых 5 ii

:ц V- I 1 СИ-; Г 33;: г юи-его -р- .-. .-. ра, ч-.п ер которого пеи с в : ;д ,)м -iiDKeb: шаногс пш ания per-.scTpa, а пепзыи а Topo.i ръ соединены соответ гвенно с база№. ; арвого и второго и первыми коллекто ;: гм с второго и первого ключевых п-рранзисторов. эмиттеры которых и баз .- сзадающс с --(-р-тр анзистора сое- ;i,rt. eiib; С ш1(ой iiy;iGV c ;o потенцияле ,-: , , и ус1шите Ь. вход котор;;го

адг нен с вторьм к( пер..ключевого П р-11-гранзистсра триг- ;г.я данного разряда и всеу р-ез- ; ЛоХ, кроме nepi-n; : - -- pfopciM К;&л-iirpOM ВТ op о . 4T-Q -,р

-. язистора t . дшествующег,л азряда, первьп выход усилителя в каяддом разряде является пер- дым вькодом управления сдвигом регистра, первый выходной буферный формирователь, вход которого соединен с третьим коллектором первого ключевого п-р-п транзистора триггера первого разряда, а выход является выходом готовности записи регистра, первый входной буферньй формирова

20

49940510

тель, выход которого соединен с вторым коллектором первого ключевого п-р-п-транзйстора триггера первого разряда, а вход является входом записи регистра, второй выходной буферный формирователь, вход которого соединен с вторым коллектором второго ключевого п-р-п-транзистора Q триггера последнего разряда, а выход является выходом готовности считывания регистра, второй входной буферный формирователь, выход которого соединен с базой первого клю- 5 чевого п-р-п-транзистора триггера последнего разряда, а вход является входом считывания регистра, о т 0

5

0

5

0

личающийся тем, что, с целью расширения области применения .регистра за счет возможности асинхроююй работы :t формирования бус- г Х по длитети. сти уг- ракиеиия сдвигоь), в него введена третий выходной буферный формиров - тель и в каждый разряд регистра логический элемент, сос .:оящий из ключ - вого п-р-п-транзистора и токозьдц.-. - щего р-п-р-транзистора, коллектор которого соединен с базой ключевсп о .; iJ- - -ранзистора. -:--рр - с ирр- - : U гьг./:,- : Л;/ -Л :,,1и-{о- : 0 . . .: оач;: -- 1. э мггepo

. - .р-п-гранзистора н г ш- -;oiii 1/улеБого :тотенциала регнстрс; второй токовы т ьгход ус}шите.пя Kfr-; дого разряда является с оответ-Г :;;,- щим выходом упрпвленил сдакг г,;-; рй гистрал пстендипльн ал выход - теля в каждом разряде соедимак с эазой ключевого п-р-п-транзисторг г1огическ 1Го элемента данного разряда, пг-рвьй коллектор ко - ;,- пикек с базой второго кл оч ;-Богс п-р- П-тг:;: нзистора триггера : .азряда, а второй ксхпяектор в каждом рй,зряде, кроме первого,, соединен с базой первого ключ -:-, п-р-п-трак- зистора триггера предьщущего разряда, второй коллектор ключевого п-р-п- транзистора логического элемента первого разряда соединен с входом выходного буферного форм11рователя, выход которого является выходом наращивания памяти регистра.

23

фцг.г

| Буферное запоминающее устройство | 1980 |

|

SU974411A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Регистр сдвига для буферного запоминающего устройства | 1985 |

|

SU1432609A1 |

Авторы

Даты

1989-08-07—Публикация

1987-01-09—Подача