Изобретение относится к технике электросвязи и может быть использовано в системах передачи дискретной информации данных и телемеханики.

Цель изобретения - повышение помехоустойчивости устройства.

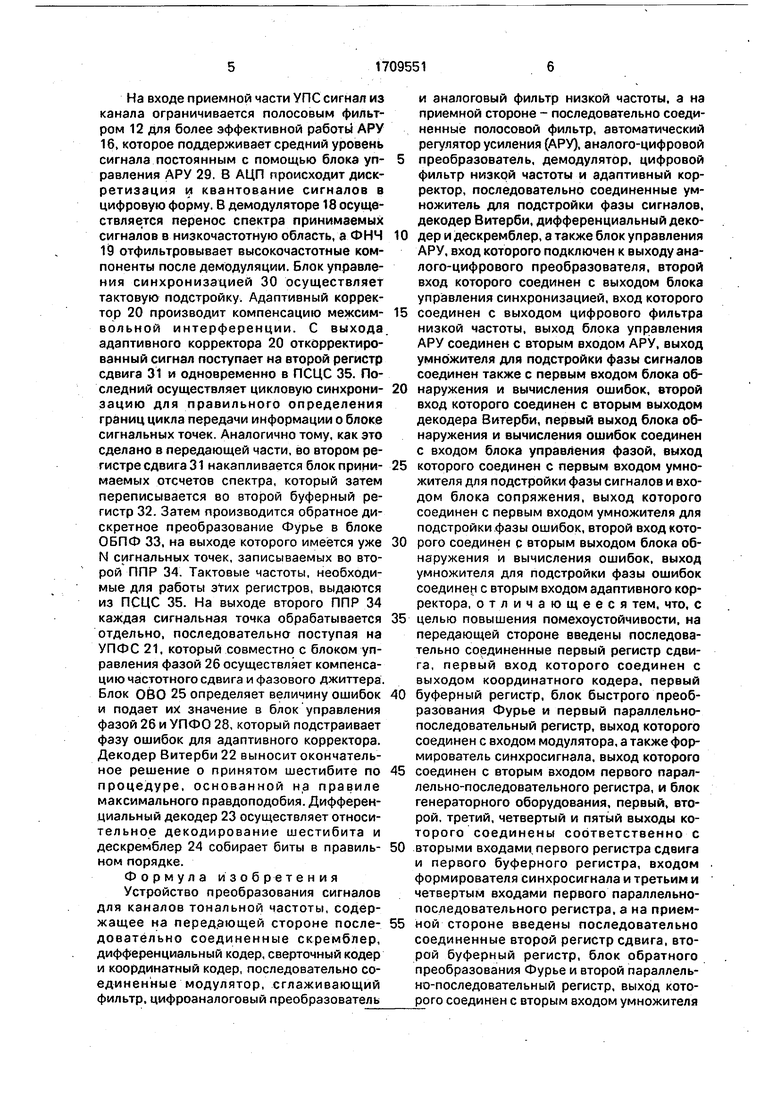

На чертеже представлена функциональная электрическая схема устройства преобразователя сигналов для каналов тональной частоты,

Устройство преобразования сигналов для каналов тональной частоты (УПС) содержит скремблер 1, дифференциальный кодер 2, сверточный кодер 3, координатный кодер 4, модулятор 5, сглаживающий фильтр 6, цифроаналоговый преобразователь (ЦАП)

7,аналоговый фильтр низкой частоты (ФНЧ)

8,первый регистр сдвига 9, первый буферный регистр 10, блок быстрого преобразования Фурье (БПФ) 11, первый параллельно-последовательный регистр (ППР) 12, блок генераторного оборудования (ГО) 13, формирователь синхросигнала 14, полобовой фильтр 16, автоматический регулятор усиления (АРУ) 16, аналого-цифровой преобразователь (дЦп) 17, демодулятор 18, цифровой фильтр низкой частоты 19, адаптивный корректор 20, умножитель для подстройки фазы сигнаяой (УПФС) 21, декодер Витерби 22, дифференциальный декодер 23, дескрёмблер 24, блок обнаружения и вычисления ошибок (ОВО) 25, блок управления фазой 26, блок сопряжения 27, умножитель для подстройки фазы ошибок (УПФО) 28, блок управления АРУ 29, блок управления синхронизацией 30, второй регистр сдвига 31, второй буферный регистр 32, блок обратного преобразования Фурье (ОБПФ) 33. второй параллельно-последовательный регистр 34, приемник сигналов цикловой синхронизации (ПСЦС) 35.

Устройство работает следующим образом.

Передаваемые данные поступают на вход скремблера 1, на выходе которого получается псевдослучайная последовательность, подаваемая на дифференциальный кодер 2 для относительного кодирования. Выходная последовательность дифференциального кодера 2 разделена на шести биты, из которых в сверточком кодере 3 образуется семибит с четырьмя не кодированными битами. После сверточного кодирования семибиты поступают в координатный кодер 4, где определяются координаты передаваемой точки из сигнат ного созвездия. На выходе координатного кодера 4 информация меняется со скоростью манипуляции, С этой же скоростью она записывается в первый регистр сдвига 9, на

тактовый вход которого подается частота сдвига, равная скорости манипуляции. В первом регистре сдвига 9 происходит формирование блока из N передаваемых сигнальных точек созвездия. Когда блок сформирован он. переписывается в первый буферный регистр 10, на тактовый вход которого подается частота в N раз меньше скорости манипуляции, а первый регистр сдвига 9 подготавливает новый блок. С помощью блока БПФ 11 производится дискретное преобразование Фурье информационного блока, находящегося в буферном регистре 10. Вычисляется спектр информационного блока и отсчеты этого спектра записываются в первый ППР 12. В этот же регистр одновременно записывается синхросигнал, поступающий от формирователя синхросигнала 14. Вся эта информация, получаемая в первом ППР 12, последовательно подается на модулятор 5, где происходит перенос отсчетов спектра сигнала и синхронизации в полосу частот канала тональной частоты. Сглаживающий фильтр 6 осуществляет оптимальное согласование передаваемых сигналов с шириной полосы канала ТЧ. В ЦАП 7 сигнал преобразуется в аналоговую форму. Аналоговый ФНЧ 8 отфильтровывает побочные продукты дискретизации ЦАП 7. Теперь информация о сигнальном блоке передается по канапу в течение N периодов манипуляции без уменьшения скорости передачи Данных и чем больше длина блока N из передаваемых точек сигнального созвездия, тем выше помехоустойчивость,

В данном случае происходит расширение базы сигналов, при котором полоса частот сигналов остается постоянной и определяется полосой канала ТЧ, а длительность передачи сигнальной точки увеличивается в N раз.

Для правильного определения границ цикла, в котором передается полная информация, о блоке сигнальных точек, служит синхросигнал, формируемый в передающей части УПС и выделяемый в приемной части с помощью ПСЦС 35. Он позволяет поблочно синхронизировать работу передатчика и приемника. Чтобы выделить время для передачи синхросигнала, скорость манипуляции на выходе передающей части несколько увеличивается, но при этом время передачи цикла остается прежним. Скорость манипуляции на выходе передающей части задается с помощью тактовой частоты, подаваемой на второй тактовый вход первого ППР 12 от блока генераторного оборудования 13./

На входе приемной части УПС сигнал из канала ограничивается полосовым фильтром 12 для более эффективной работы АРУ 16, которое поддерживает средний уровень сигнала постоянным с помощью блока управления АРУ 29. В АЦП происходит дискретизация и квантование сигналов в цифровую форму. В демодуляторе 18 осуществляется перенос спектра принимаемых сигналов в низкочастотную область, а ФНЧ 1i9 отфильтровывает высокочастотные компоненты после демодуляции. Блок управления синхронизацией 30 осуществляет тактовую подстройку. Адаптивный корректор 20 производит компенсацию межсимвольной интерференции. С выхода адаптивного корректора 20 откорректированный сигнал поступает на второй регистр сдвига 31 и одновременно в ПСЦС 35. Последний осуществляет цикловую синхронизацию для правильного определения границ цикла передачи информации о блоке сигнальных точек. Аналогично тому, как это сделано в передающей части, во втором регистре сдвига 31 накапливается блок принимаемых отсчетов спектра, который затем переписывается во второй буферный регистр 32. Затем производится обратное дискретное преобразование Фурье в блоке ОБПФ 33. на выходе которого имеется уже N сигнальных точек, записываемых во второй ППР 34. Тактовые частоты, необходимые для работы зtиx регистров, выдаются из ПСЦС 35. На выходе второго ППР 34 каждая сигнальная точка обрабатывается отдельно, последовательно поступая на УПФС 21, который совместно с блоком управления фазой 26 осуществляет компенсацию частотного сдвига и фазового джиггера. Блок обо 25 определяет величину ошибок и подает их значение в блок управления фазой 26 и УПФО 28, который подстраивает фазу ошибок для адаптивного корректора. Декодер Витерби 22 выносит окончательное решение о принятом шестибите по процедуре, основанной на правиле максимального правдоподобия. Дифференциальный декодер 23 осуществляет относительное декодирование шестибита и дескремблер 24 собирает биты в правильном порядке.

Формула изобретения Устройство преобразования сигналов для каналов тональной частоты, содержащее на передающей стороне последоватёльно соединенные скремблер, дифференциальный кодер, сверточный кодер и координатный кодер, последовательно соединенные модулятор, сглаживающий фильтр, цифроаналоговый преобразователь

и аналоговый фильтр низкой частоты, а на приемной стороне - последовательно соединенные полосовой фильтр, автоматический регулятор усиления (АРУ), аналого-цифровой преобразователь, демодулятор, цифровой фильтр низкой частоты и адаптивный корректор, последовательно соединенные умножитель для подстройки фазы сигналов, декодер Витерби, дифференциальный декодер и дескремблер, а также блок управления АРУ, вход которого подключен к выходу аналого-цифрового преобразователя, второй вход которого соединен с выходом блока управления синхронизацией, вход которого соединен с выходом цифрового фильтра низкой частоты, выход блока управления АРУ соединен с вторым входом АРУ, выход умножителя для подстройки фазы сигналов соединен также с первым входом блока обнаружения и вычисления ошибок, второй вход которого соединен с вторым выходом декодера Витерби, первый выход блока обнаружения и вычисления ошибок соединен с входом блока управления фазой, выход которого соединен с первым входом умножителя для подстройки фазы сигналов и входом блока сопряжения, выход которого соединен с первым входом умножителя для подстройки фазы ошибок, второй вход которого соединен р вторым выходом блока обнаружения и вычисления ошибок, выход умножителя для подстройки фазы ошибок соедине{1 с вторым входом адаптивного корректора, отличающееся тем, что, с целью повышения помехоустойчивости, на передающей стороне введены последовательно соединенные первый регистр сдвига, первый вход которого соединен с выходом координатного кодера, первый буферный регистр, блок быстрого преобразования Фурье и первый параллельнопоследовательный регистр, выход которого соединен с входом модулятора, а также формирователь синхросигнала, выход которого соединен с вторым входом первого параллельно-последовательного регистра, и блок генераторного оборудования, первый, второй, третий, четвертый и пятый выходы которого соединены соответственно с вторыми входами, первого регистра сдвига и первого буферного регистра, входом формирователя синхросигнала и третьим и четвертым входами первого параллельнопоследовательного регистра, а на приемной стороне введены последовательно соединенные второй регистр сдвига, второй буферный регистр, блок обратного преобразования Фурье и второй параллельно-последовательный регистр, выход которого соединен с вторым входом умножителя

7 17095518

для подетройхи фазы сигналов, а также при-сигналов цикловой синхронизации соединеемник сигналов цикловой синхронизации,ны соответственно с вторыми входами втовход которого объединен с первым входомрого регистра сдвига и второго буферного

второго регистра сдвига и подключен к вы-регистра, вторым и третьим входами второходу адаптивного корректора, первый, вто-5 го параллельно-последовательного регирой, третий и четвертый выходы приемникастра.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛИРОВАНИЯ И ДЕКОДИРОВАНИЯ ВИДЕОСИГНАЛОВ | 1996 |

|

RU2172566C2 |

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ВИДЕОСИГНАЛОВ, КОДИРОВАННЫХ В РАЗНЫХ ФОРМАТАХ | 1996 |

|

RU2171548C2 |

| МНОГОКАНАЛЬНОЕ ПРИЕМНО-ДЕМОДУЛИРУЮЩЕЕ УСТРОЙСТВО ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ СИСТЕМ СВЯЗИ | 2005 |

|

RU2305375C2 |

| Устройство для регенерации биимпульсных сигналов | 1989 |

|

SU1688413A1 |

| ЦИФРОВОЙ МОДЕМ КОМАНДНОЙ РАДИОЛИНИИ ЦМ КРЛ | 2013 |

|

RU2548173C2 |

| Устройство передачи данных | 1990 |

|

SU1723671A1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2001 |

|

RU2185029C1 |

| Кодек для системы связи с многократной фазовой модуляцией | 1987 |

|

SU1629992A1 |

Изобретение относится к технике связи и может быть использовано в.системах передачи данных и телемеханики. Цель - повышение помехоустойчивости. Устр-во содержит на передающей стороне скремб- лер 1, кодеры 2-4, модулятор 5, сглаживающий фильтр 6. ЦАП 7, ФНЧ 8, a на приемнойстороне ПФ 15, АРУ 16, АЦП 17, демодулятор 18, ФНЧ 19, адаптивный корректор 20, умножитель для подстройки фазы сигналов 21, декодер Витерби 22, дифференциальный декодер 23, дескремблер 24, блок обнаружения и вычисления ошибок 25, блок управления фазой 26, блок сопряжения 27, умножитель для подстройки фазы ошибок 28, блок управления АРУ 29, блок управления синхронизацией 30. Цель достигается введением на передающей стороне регистра сдвига 9, буферного регистра 10, блока быстрого преобразования Фурье 1, параллельно-последовательного регистра 12 и блока генераторного оборудования 13, a на приемной стороне регистра сдвига 31, буферного регистра 32, блока обратного преобразования Фурье 33, параллельно- последовательного регистра 34 и приемника сигналов цикловой синхронизации 35. За счет введенных блоков в устр-ве из сигнальных точек составляется блок из N элементов, производится вычисление N отсчетов спектра этого блока и их последовательная передача. 1 ил.'•' ^^I01ел

| Kamitoke Т., Kawamura S | |||

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| with a single-Chip High-Speed Digital signal processor | |||

| Торфодобывающая машина с вращающимся измельчающим орудием | 1922 |

|

SU87A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Rec | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-01-30—Публикация

1989-12-12—Подача