Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении систем передачи данных.

Цель изобретения - повышение достоверности за счет обеспечения контроля исправности устройства во время работы без нарушения связи с аппаратурой передачи данных.

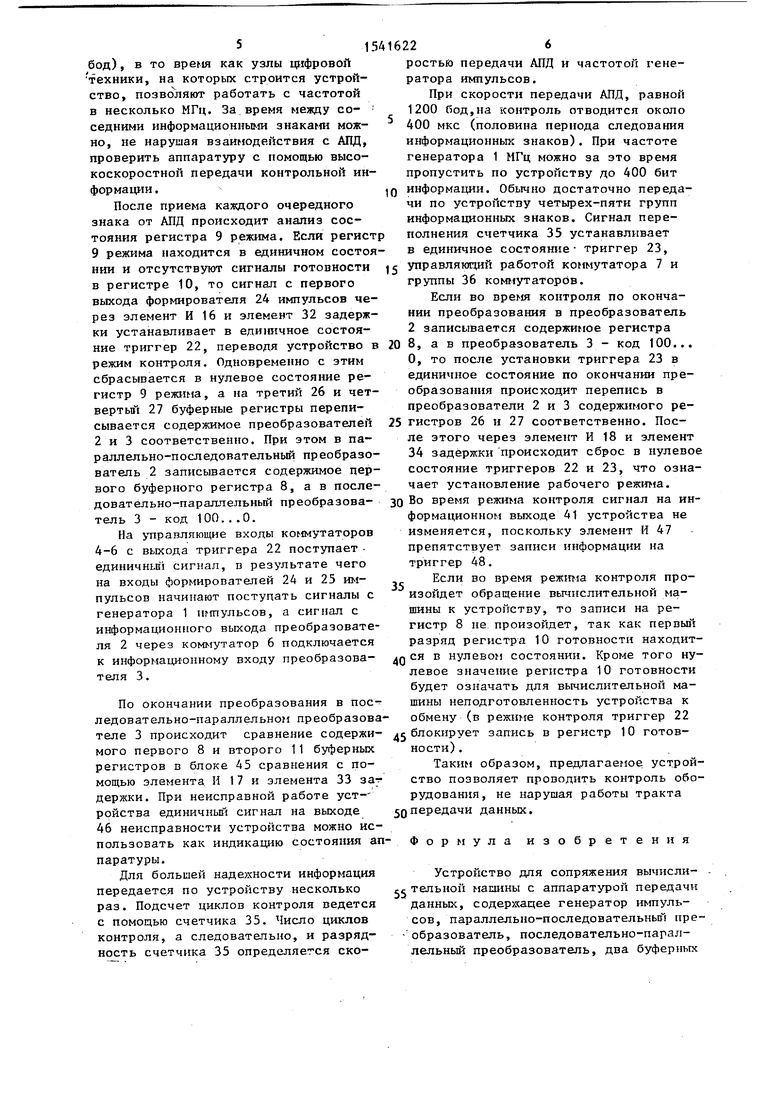

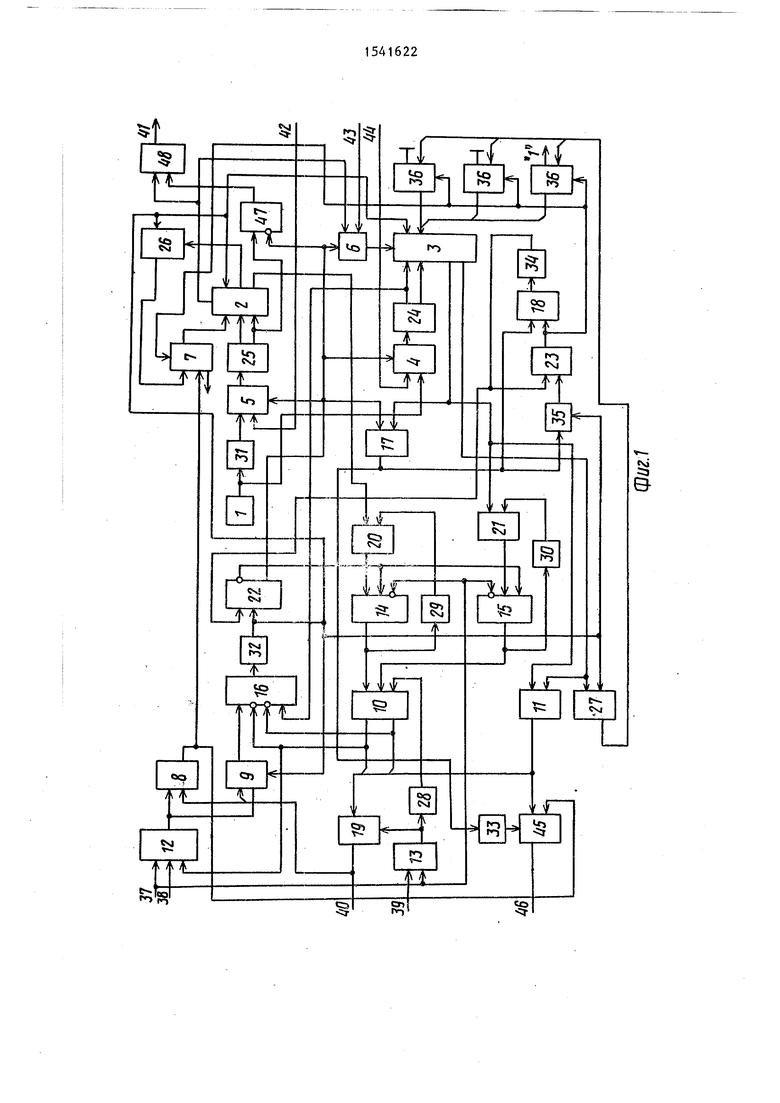

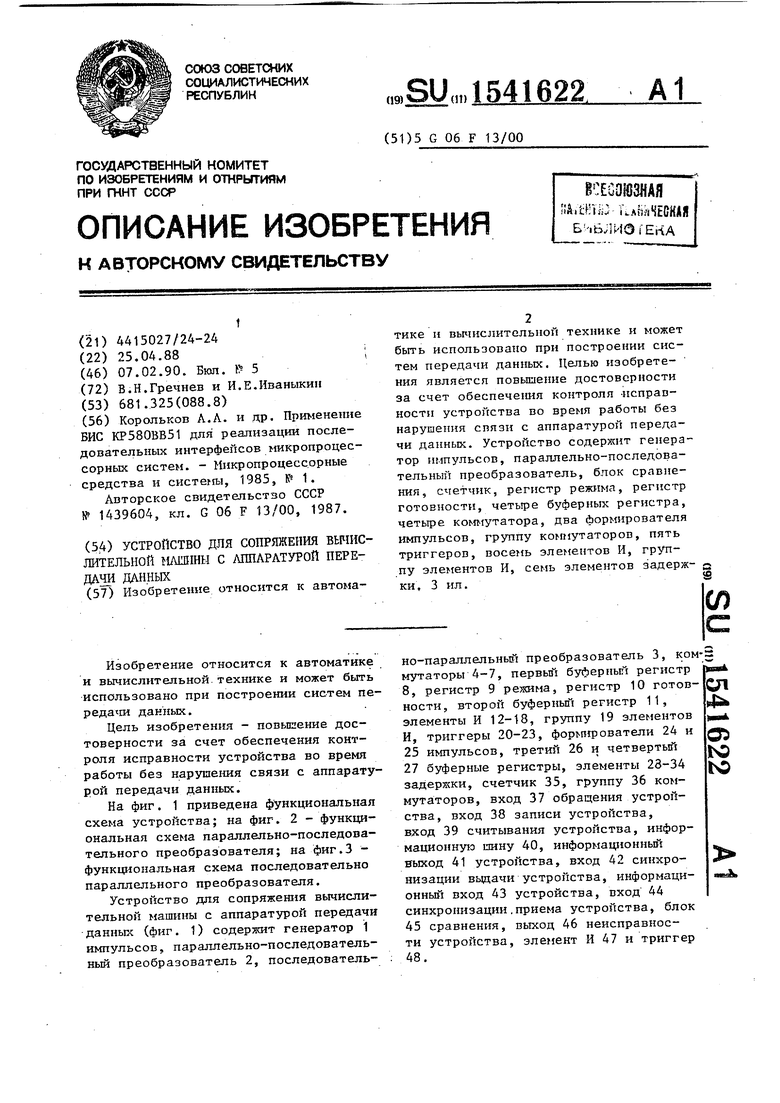

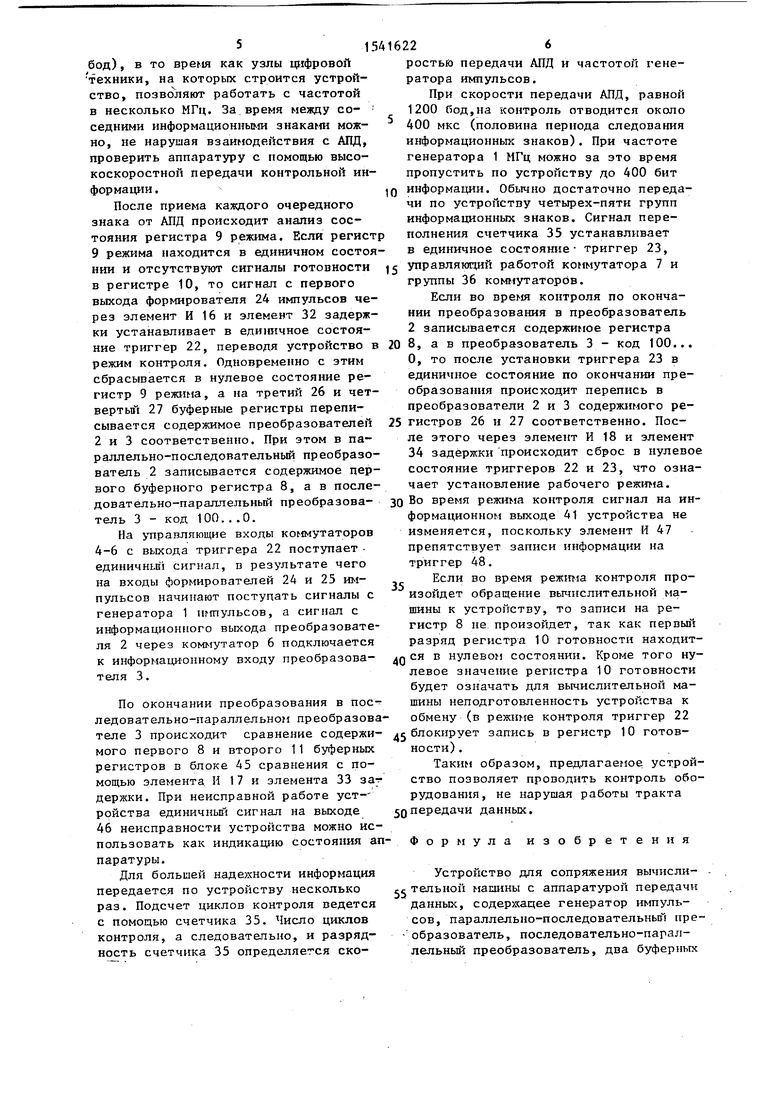

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - функциональная схема параллельно-последовательного преобразователя; на фиг.З - функциональная схема последовательно параллельного преобразователя.

Устройство для сопряжения вычислительной машины с аппаратурой передачи данных (фиг. 1) содержит генератор 1 импульсов, параллельно-последовательный преобразователь 2, последовательно-параллелышй преобразователь 3, коммутаторы 4-7, первый буферный регистр 8, регистр 9 режима, регистр 10 готовности, второй буферный регистр 11, элементы И 12-18, группу 19 элементов И, триггеры 20-23, формирователи 24 и 25 импульсов, третий 26 и четвертый 27 буферные регистры, элементы 23-34 задержки, счетчик 35, группу 36 коммутаторов, вход 37 обращения устройства, вход 38 записи устройства, вход 39 считывания устройства, информационную шину 40, информационный выход 41 устройства, вход 42 синхронизации выдачи устройства, информационный вход 43 устройства, вход 44 синхронизации.приема устройства, блок 45 сравнения, выход 46 неисправности устройства, элемент И 47 и триггер 48.

сд

Јъ

сэ

КС 1C

1

3154

Параллельно-последовательный преобразователь 2 (фиг. 2) содержит регистр 49 сдвига и элементы И 50 и ИЛИ 51.

Последовательно-параллельный преобразователь 3 (фиг. 3) содержит регистр 52 сдвига, элемент И 53, элемент 54 задержки и элемент ИЛИ 55. Первый элемент 28 задержки необходим для обеспечения надежного приема содержимого регистра 10 готовности в вычислительную машину. Четвертый элемент 31 задержки необходим, чтобы в режиме контроля сначала произошла пе- репись информации из преобразователя 2 в преобразователь 3 и только потом осуществился сдвиг в преобразователе 2. Первый 8 и второй 11 буферные регистры содержат по К разрядов, где К 2 определяется количеством биЈ информации, передаваемой из вычислительной машины в устройство и обратно. Регистр 9 режима одноразрядный, регистр 10 готовности двухразрядный. Третий 26 2 и четвертый 27 буферные регистры содержат по (К+l) разрядов. Устройство предназначено для работы в системах, где сигналы на входы 42 и 44 синхронизации устройства поступают в одно и то же время.

Устройство для сопряжения вычислительной машины с аппаратурой передачи данных работает следующим образом.

Существуют два режима работы: рабо-, чий режим и режим контроля, который устанавливается на одноразрядном регистре 9 режима признаком, поступающим из вычислительной машины по информационной шине 40. Нулевое значение д признака означает рабочий режим устройства, единичное значение - режим контроля.

Обычное состояние устройства - рабочий режим. В этом режиме информация,4 поступающая из вычислительной машины по информационной шине 40, при наличии единичных сигналов на входах 37 и 38 обращения и записи устройства и .в первом разряде регистра 10 ГОТОВНОС-C тн записывается на первый буферный регистр 8 и регистр 9 режима (в регистр 9 режима записывается нулевая информация). В начале работы устройства устанавливаются в нулевое состояние четвертый 22 и пятый 23 триггеры. Коммутатор г пропускает на вход формирователя 25 иппупьсов сигналы с входа 42 синхронизации выдачи устройства.

0

1

0 5 Q

д

5 Q

6224

Эти сигналы и определяют работу параллельно-последовательного преобразователя 2, на группу информационных входов которого по окончании преобразования записывается информация с выходов первого буферного регистра 8, которая поступает через коммутатор 7. Сигнал конца преобразования параллельно-последовательного преобразователя 2 записывается на первый триггер

20,с выхода которого записывается через элемент И 14 в первый разряд регистра 10 готовности (для обеспечения надежности записи готовности в регистр 10 элемент И 14 запрещает запись в регистр 10 во время обращения из вычислительной машины к устройству)

В рабочем режиме коммутатор 4 пропускает на вход формирователя 24 импульсов сигналы с входа 44 синхронизации приема устройства. Эти сигналы управляют работой последовательно-параллельного преобразователя 3. По окончании преобразования накопленная информация, поступившая по информационному входу 43 устройства, записывается на второй буферный регистр 11. Сигнал конца преобразования устанавливает в единичное состояние триггер

21.При отсутствии в этот момент обращения к устройству со стороны вычислительной машины происходит установка в единичное состояние второго разряда регистра 10 готовности с: помощью элемента И 15 (после установки в единичное состояние триггеров регистра

10 готовности осуществляется сброс в нулевое состояние триггеров 20 и 21 через элементы 29 и 30 задержки.

При поступлении единичного сигнала на входы 37 и 39 обращения и чтения устройства происходит считывание содержимого регистра 10 готовности и второго буферного регистра 11 через группу 19 элементов FI в информационную шину 40 устройства для передачи в вычислительную машину. По окончании преобразования в последовательно-параллельный преобразователь 3 записывается код 1000...О через группу 36 коммутаторов.

При поступлении в регистр 9 режима единичного сигнала устройство готовится перейти в режим контроля. Контроль основан на том, что как правило, аппаратура передачи данных (АПД) имеет относительно низкую скорость передачи (1200 бод, 2400 бод, 9600

бод), в то вреня как узлы цифровой техники, на которых строится устройство, позволяют работать с частотой в несколько МГц. За время между соседними информационными знаками можно, не нарушая взаимодействия с АПД, проверить аппаратуру с помощью высокоскоростной передачи контрольной информации.

После приема каждого очередного знака от АПД происходит анализ состояния регистра 9 режима. Если регист

При скорости передачи АПД, равной 1200 бод,на контроль отводится около 400 мкс (половина периода следования информационных знаков). При частоте генератора 1 МГц можно за это время пропустить по устройству до 400 бит Q информации. Обычно достаточно передачи по устройству четырех-пяти групп информационных знаков. Сигнал переполнения счетчика 35 устанавливает в единичное состояние- триггер 23,

9 режима находится в единичном состоянии и отсутствуют сигналы готовности J5 Управляющий работой коммутатора 7 и в регистре 10, то сигнал с первого группы 36 коммутаторов, выхода формирователя 24 импульсов че- Если во время контроля по оконча- рез элемент И 16 и элемент 32 задерж- нии преобразования в преобразователь ки устанавливает в единичное состоя- 2 записывается содержимое регистра ние триггер 22, переводя устройство в 20 8, а в преобразователь 3 - код 100... режим контроля. Одновременно с этим 0, то после установки триггера 23 в сбрасывается в нулевое состояние ре- единичное состояние по окончании пре- гистр 9 режима, а на третий 26 и чет- образования происходит перепись в

преобразователи 2 и 3 содержимого ре- 25 гистров 26 и 27 соответственно. После этого через элемент И 18 и элемент 34 задержки происходит сброс в нулевое состояние триггеров 22 и 23, что означает установление рабочего режима. 30 Во время режима контроля сигнал на информационном выходе 41 устройства не изменяется, поскольку элемент И 47 препятствует записи информации на триггер 48.

Если во время режима контроля произойдет обращение вычислительной машины к устройству, то записи на регистр 8 не произойдет, так как первый разряд регистра 10 готовности находит- дд ся в нулевом состоянии. Кроме того нулевое значение регистра 10 готовности будет означать для вычислительной маПо окончании преобразования в пос- шины неподготовленность устройства к ледовательно-параллельном преобразова- обмену (в режиме контроля триггер 22 теле 3 происходит сравнение содержи- деблокирует запись в регистр 10 готовности) .

Таким образом, предлагаемое устройство позволяет проводить контроль оборудования, не нарушая работы тракта 5опередачи данных.

вертый 27 буферные регистры переписывается содержимое преобразователей 2 и 3 соответственно. При этом в параллельно-последовательный преобразователь 2 записывается содержимое первого буферного регистра 8, а в последовательно-параллельный преобразователь 3 - код 100...0.

На управляющие входы коммутаторов 4-6 с выхода триггера 22 поступает единичный сигнал, н результате чего на входы формирователей 24 и 25 импульсов начинают поступать сигналы с генератора 1 импульсов, а сигнал с информационного выхода преобразователя 2 через коммутатор 6 подключается к информационному входу преобразователя 3.

35

мого первого 8 и второго 11 буферных регистров в блоке 45 сравнения с помощью элемента И 17 и элемента 33 за- держки. При неисправной работе уст- ройства единичный сигнал на выходе 46 неисправности устройства можно использовать как индикацию состояния аппаратуры.

Для большей надежности информация передается по устройству несколько раз. Подсчет циклов контроля ведется с помощью счетчика 35. Число циклов контроля, а следовательно, и разрядность счетчика 35 определяется скоФормула изобретения

Устройство для сопряжения вычислите тельной машины с аппаратурой передачи данных, содержащее генератор импульсов, параллельно-последовательный пре- - образователь, последовательно-параллельный преобразователь, два буферных

ростьй передачи АПД и частотой генератора импульсов.

При скорости передачи АПД, равной 1200 бод,на контроль отводится около 400 мкс (половина периода следования информационных знаков). При частоте генератора 1 МГц можно за это время пропустить по устройству до 400 бит информации. Обычно достаточно передачи по устройству четырех-пяти групп информационных знаков. Сигнал переполнения счетчика 35 устанавливает в единичное состояние- триггер 23,

5 Управляющий работой коммутатора 7 и группы 36 коммутаторов, Если во время контроля по оконча- нии преобразования в преобразователь 2 записывается содержимое регистра 0 8, а в преобразователь 3 - код 100... 0, то после установки триггера 23 в единичное состояние по окончании пре- образования происходит перепись в

дд

35

Формула изобретения

Устройство для сопряжения вычислите тельной машины с аппаратурой передачи данных, содержащее генератор импульсов, параллельно-последовательный пре- - образователь, последовательно-параллельный преобразователь, два буферных

регистра, регистр готовности, два триггера, четыре коммутатора, четыре элемента задержки, шесть элементов И, два формирователя импульсов, регистр режима, причем первый вход первого элемента И соединен с первым входом второго элемента И, с инверсными входами третьего и четвертого элементов И и является входом устройства для подключения к выходу обращения вычислительной машины, вторые входы первого и второго элементов И являются входами устройства для подключения соответственно к выходам записи и чте- ния вычислительной машины, первые информационные входы первого и второго коммутаторов являются входами устройства для подключения соответственно к выходам синхронизации выдачи и синхронизации приема аппаратуры передачи данных, первый информационный вход третьего коммутатора является входом устройства для подключения к информационному выходу аппаратуры передачи данных, при этом вход записи регистра режима соединен с входом записи первого буферного регистра и с выходом первого элемента И, третий вход которого соединен с первым формационным выходом регистра ГОТОР- ности, установочный вход которого динен с выходом первого элемента , держки, вход которого соединен с лп ходом второго элемента И, единичный выход первого триггера соединен с первым входом третьего эпемзнта И, выход которого соединен с первым информационным входом регистра готовности и с входом второго элемента за- держки, выход которого соединен с ну левым входом первого триггера, единичный вход которого соединен с выходом конца преобразования параллельно-последовательного преобразовате- ля, первый и второй синхровходы которого соединены соответственно с первым и вторым выходами первого формирователя импульсов, вход запуска которо го соединен с выходом первого комму- татора, информационный выход параллельно-последовательного преобразователя соединен с вторым информационным входом третьего коммутатора, выход ко которого соединен с информационным входом последовательно-параллельного преобразователя, первый и второй сип- хровходы которого соединены соответственно с первым и вторым выходами

второго формирователя импульсов, вход запуска которого соединен с выходом второго коммутатора, единичный выход второго триггера соединен с первым входом четвертого элемента И, выход которого соединен с втор.ым информационным входом регистра готовности и с входом третьего элемента задержки, выход которого соединен с пулевым входом второго триггера, единичный вход которого соединен с выходом конца преобразования последовательно- параллельного преобразователя, группа информационных выходов которого соединена с группой информационных входов второго буферного регистра, отличающееся тем, что, с целью повышения достоверности за счет обеспечения контроля исправности устройства во время работы без нарушения связи с аппаратурой передачи данных, в устройство ьведоны два буферных регистра, три триггера, счетчик, блок сравнения, два элемента И, группа элементов И, три элемента задержки, группа коммутаторов, причем выходы элементов И группы, группы информационных входов первого буферного регистра, информационный вход регистра режима образуют группу входов-выхо- Т.ОБ устройства для подключения к группе информационных входов-выходов ппч слительной машины, выход блока сравнения является выходом устройства для подключения к входу неисправности вычислительной машины, выход третьего триггера является выходом устройства для подключения к информационному входу аппаратуры передачи данных при этом выход генератора импульсов соединен с вторым информационным входом второго коммутатора и с входом четвертого элемента задержки, выход которого соединен с вторым информационным входом первого коммутатора, управляющий вход которого соединен с управляющими входами второго и третьего коммутаторов,, с инверсным входом пятого элемента И, с первым входом шестого элемента И и с единичным выходом четвертого триггера, единичный вход которого соединен с входами записи третьего и четвертого буферных регистров , параллельно-последовательного преобразователя, последовательно-параллельного преобразователя, с установочными входами счетчика, регистра режима и с выходом пятого элемента за

держки, вход которого соединен с выходом седьмого элемента И, первый инверсный вход которого соединен с первым информационным выходом регистра готовности, второй информационный выход которого соединен с вторым инверсным входом седьмого элемента И, первый и второй входы которого соединены соответственно с вторым выходом второго формирователя импульсов и с информационным выходом регистра режима, второй вход четвертого элемента И соединен с вторым входом третьего элемента И и с нулевым выходом четвер того триггера, нулевой вход которого соединен с нулевым входом пятого триггера и с выходом шестого элемента задержки, вход которого соединен с выходом восьмого элемента И, первый вход которого соединен с единичным выходом пятого триггера, с управляющим входом четвертого коммутатора, с управляющими входами коммутаторов группы, выходы которых соединены с группой информационных входов последовательно-параллельного преобразователя, группа информационных выходов которого соединена с группой информационных входов четвертого буферного регистра, группа информационных выходов которого соединена с первыми информационными входами коммутаторов группы, вторые информационные входы которых (кроме первого коммутатора из группы коммутаторов) подключены к шине нулевого потенциала устройства, второй информационный вход первого коммутатора из группы коммутаторов подключен к шине единичного потенциала устройства, выход конца преобразования последовательно- параллельного преобразователя соединен с вторым входом шестого элемента И и с входом записи второго буферного

0

5 $

5

0

5

0

регистра, группа информационных выходов которого соединена с первой группой информационных входов блока сравнения, вторая группа информационных входов которого соединена с труп- пой информационных выходов первого буферного регистра и с первой группой информационных входов (кроме старшего разряда) четвертого коммутатора, группа выходов которого соединена с группой информационных входов параллельно-последовательного преобразователя, группа информационных выходов которого соединена с группой информационных входов третьего буферного регистра, группа информационных выходов которого соединена с второй группой информационных входов четвертого коммутатора, старший разряд первой группы информационных входов которого подключен к шине единичного потенциала устройства, второй выход первого формирователя импульсов соединен с входом пятого элемента И, выход которого соединен с синхровходом третьего триггера, информационный вход которого соединен с информационным выходом параллельно-последовательного преобразователя, разрешающий вход блока сравнения соединен с выходом седьмого элемента задержки, вход которого соединен с выходом шестого элемента И, с вторым входом восьмого элемента И и со счетным входом счетчи- ка, выход переполнения которого соединен с единичным входом пятого триггера, группа информационных выходов второго буферного регистра, первый и второй информационные выходы регистра готовности соединены с первыми входами элементов И группы, вторые входы которых соединены с выходом второго элемента И.

I

кбл.го

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с аппаратурой передачи данных | 1987 |

|

SU1439604A1 |

| Устройство для сопряжения вычислительной машины с аппаратурой передачи данных | 1989 |

|

SU1679492A1 |

| Устройство для ввода-вывода информации при обработке физических величин | 1981 |

|

SU966683A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1980 |

|

SU918944A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

| Устройство для сопряжения абонента с каналом связи | 1987 |

|

SU1508218A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1990 |

|

SU1727126A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для сопряжения электронно-вычислительной машины с каналами связи | 1984 |

|

SU1244670A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении систем передачи данных. Целью изобретения является повышение достоверности за счет обеспечения контроля исправности устройства во время работы без нарушения связи с аппаратурой передачи данных. Устройство содержит генератор импульсов, параллельно-последовательный преобразователь, блок сравнения, счетчик, регистр режима, регистр готовности, четыре буферных регистра, четыре коммутатора, два формирователя импульсов, группу коммутаторов, пять триггеров, восемь элементов И, группу элементов И, семь элементов задержки. 3 ил.

Кйл.П

51

K6JI.Z5 (zv Выход)

/TffA.ZS

(1ибыхио) KGfl.l

к бл.21

г

50

ЬЗ-1

W-Z

Ш-К

k I

Фиг. г

Фиг.З

| Корольков А.Л | |||

| и др | |||

| Дисковая паровая турбина | 1922 |

|

SU580A1 |

| - Микропроцессорные средства и системы, 1985, № 1 | |||

| Устройство для сопряжения вычислительной машины с аппаратурой передачи данных | 1987 |

|

SU1439604A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-07—Публикация

1988-04-25—Подача