СО

со о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с аппаратурой передачи данных | 1988 |

|

SU1541622A1 |

| Устройство для сопряжения вычислительной машины с аппаратурой передачи данных | 1989 |

|

SU1679492A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1981 |

|

SU1012234A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1980 |

|

SU918944A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для сопряжения электронно-вычислительной машины с каналами связи | 1984 |

|

SU1244670A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с периферийными устройствами | 1985 |

|

SU1285484A1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| Устройство для контроля микропроцессорной системы | 1984 |

|

SU1221655A1 |

Изобретение относится ic автоматике и вычислительной технике, может быть использовано при построении сис- теь передачи данных и позволяет повысить контролепригодность устройства. Устройство для сопряжения вычислительной машины с аппаратурой передач55 данных содержит генератор импульсов, параллельно-последовательиьп преобразователь и последовательно-параллельный преобразователь,делитель частоты, пять коммутаторов,буферные регистры 10,11 .регистры режима и готовности,два триггера 14,15,два формирователя импульсов 16, 17, четыре элемента задержки 18-21, дешифратор 22 адреса и шесть элементов И 23-28. 1 з.п. ф-лы, 3 ил. S

9U2..1

Изобретен ге относится к автоматгз- ке и вычислительной технике и может бьгть использовано при построении систем передачи данных.

Целью изобретения является повышение контролеприго/и ости устройства за счет организап.тш иигейфа передаваемой информации II орган1;зацин не- тактового контроля прохол дения инфор - мации по устройству.

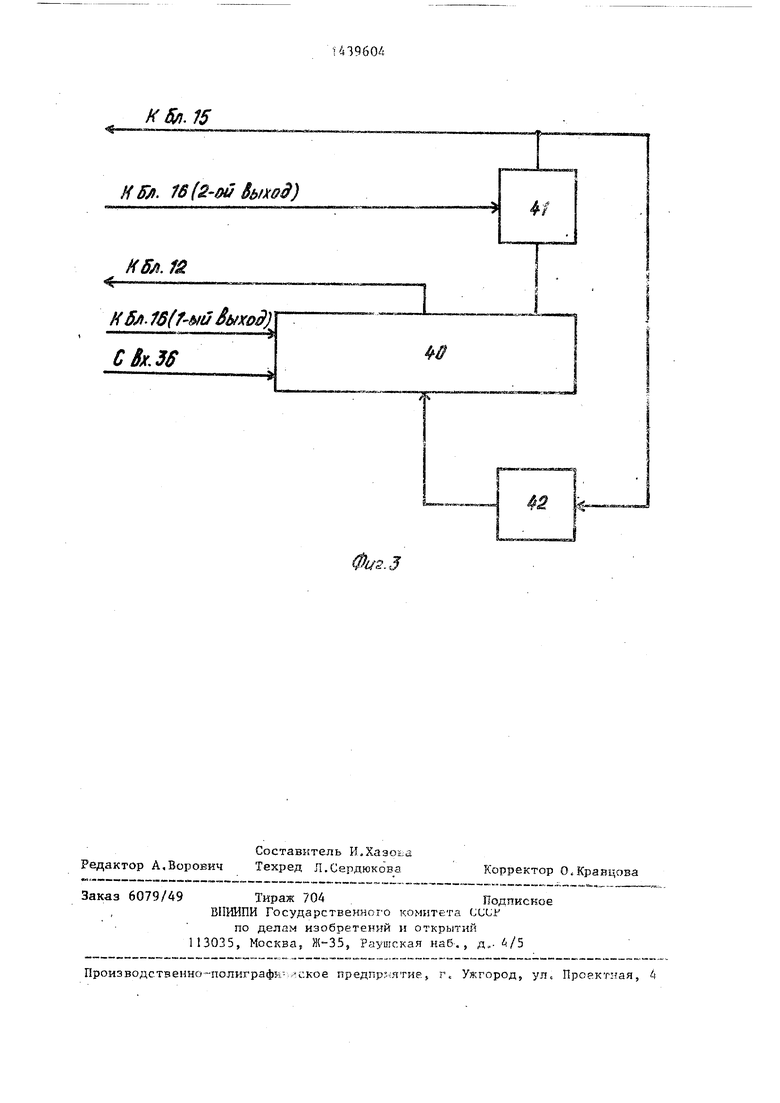

На фиг.1 приведена фушсциональная

схема устройстваj на фиг,

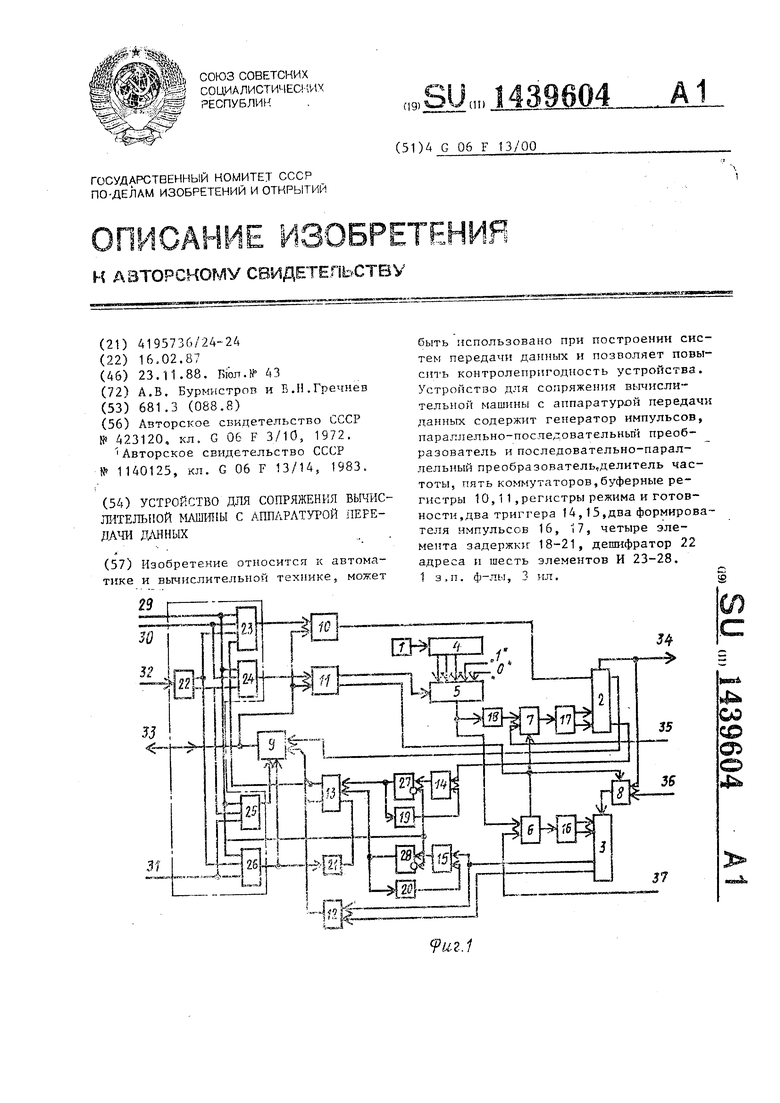

-- вариант функциональной cxei -ft параллельно15

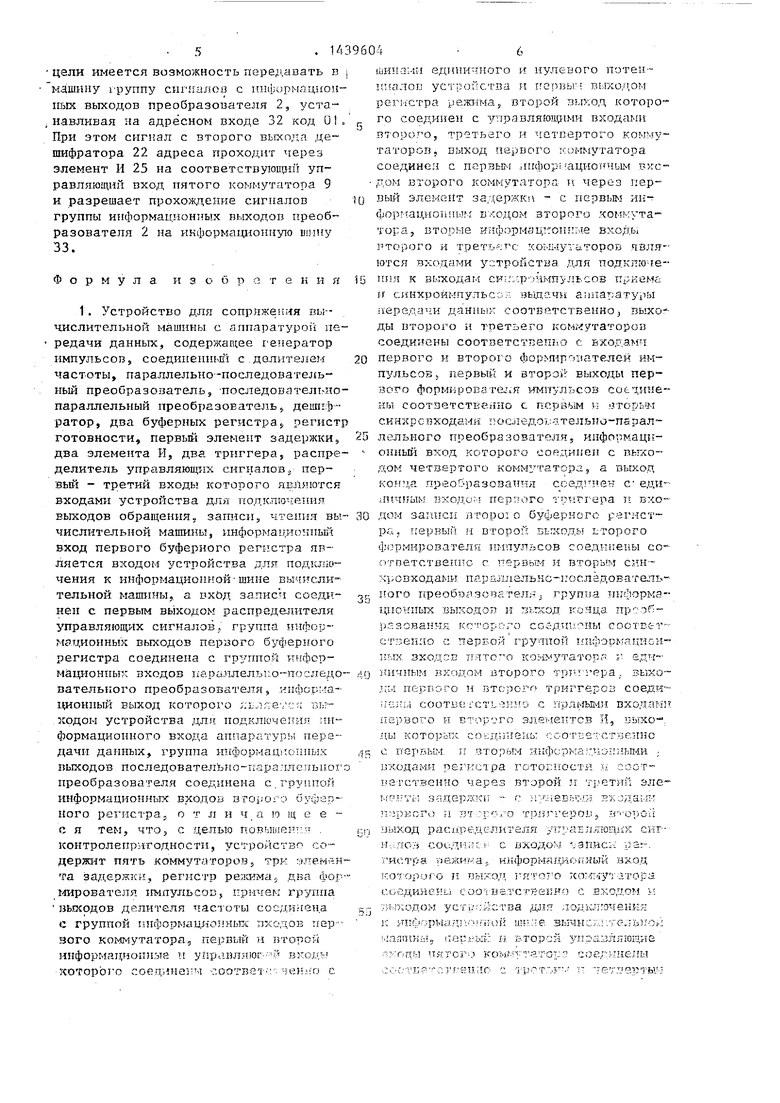

последонательного преобразователя; на. фиг.З - вариант фупгдионалыюй последовательно-параллешьного преобразователя.

Устройство для сопряжения вычислительной машины с аппаратурой /тередачи : 20 данных (фиг.1) содержит генератор t импульсов, параллельно-последовательный преобразовател. 2 . ггоследователь- но-параллельный преобразователь 3,

Для этой цели на вход ния и вход 30 зали:..н ггсд жите л ЬИЫР импульсы., на а 32 поступает код О, а н

онную пшну

код уТГрЕ

ва. При этом формирз ется втором выходе дейшфрато открываете злемент И 24 щеа слово поетулае ; на р старший разряд которого

3f

делитель 4 частоты, Kobw-iyvaTopH 5-9, 23 ботой ког-мутаторов 6-8. первый буферный регистр Ю,, регистр 11 режима, второй бi фepыьrf регистр 12, регистр 13 готовности, второй и первьш триггеры 14 и 15, формирователи 16 и 17 шпульсоВу первый, третий, второй, четвертый, элементы 18-21 задержки, распределитель управляющих сигналов, состоящий из де- Ешифратора 22 адреса, эламеитов И 23- 26, кроме того, устройство сбдсфжиг второй и первьп элементы И .27 и 28.. вход 29 обращения, в5сод 30 залкси, вход 31 считывания, адресный вкод 32,. информационную шину 33, информащюн- ный выход 34, вход 35 сиихропизащл AQ вьщачи, информационный вход 36, вход 37 синхронизатдии прием.а,

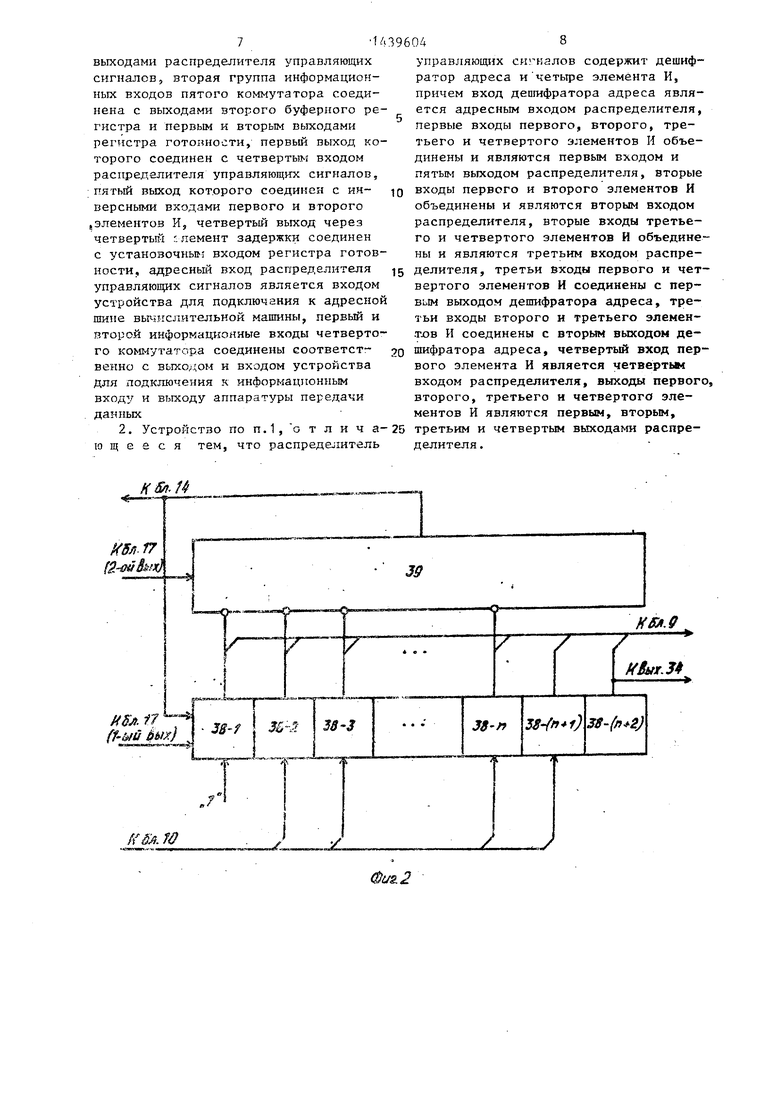

11араллельно-последова1 ельньи преобразователь 3 (фиг,2) содержит (п+2) разрядный регистр 38 сдви: % а, где п дз; разрядность преобразуемого параллельного кода, и элемент И 39.

Последовательно-параллельный пре- . образователь 2 (фиг.З) содержит (n-i-1)- разрядный регистр 40 сдвига, ;, Лймект , И 41 и элемент 42 задержки.

Устройство может работать Б цвух

режимах - работы и контроля,, Режим

работы, определяется словом, поступаю- щим КЗ вычислительной машины на регистр

11 режима но информ.йционнсй шине 33. Нулевое значение старшего разряда

управляющего слова (признака задания

режима контроля) означает -бочий ряВ рабочем реяаше на ; форнировате.ггя 16 импульс рой комментатор б поступа сигиальз err аппаратуры пе 30 (АИД) с входа 37 сиггхрон ма. На вход второго фopь импульсов через третий к поступают тактовые сигна входа 35 сшгхроиизации в

В дараллельпо-последо преобразователь 2 и посл паратшельньнЧ преобразова лом иачалы/ых. устанойб т- устаназлизается код 10GO

ШгфоркациЯ; пеобход1ам дачи в АЦП, поступает из иой машины по KHmopMajijro При этом на вход, 29 30 записи nocTynaiOT пол иульсы, а на адресиьпЧ ;8 .пает код 00. На керном ратора 22 адреса формир ный снгка.я и при наличи сигнала iia .гшшоде перво гистра 13 через элемент Е, тггатся sam. ci- информап регистр 10 зь-дачи,

По сигналу кскца иуе параллельно-последовате разователя 2 осуздествля Б прбобразова ель 2 кнф гистра 10 н установка в состояние триггера 14. момеь-т оР/)ащение к устр

им устройст;за, единичное значеи .-е режим KOHTpOjiH. Остальные разряды управляют скоростью работы устройства в релотме .контроля. Коды разрядов признаков задания режима работы тактовых час го Г означают следующее: 000- работа со скоростью 1200 5од; 001 - работа, со скоростью 2400 бод; 010 - работа со скоростью 4800 бод; 011 -ну- лавое значение тактового сигнала , 100- единичное значение тактового сигнала.

Б начале работы устаиавливлатся релшм работы устройства.

Для этой цели на вход .29 обращения и вход 30 зали:..н ггсдаюг сл положите л ЬИЫР импульсы., на адресньш вход 32 поступает код О, а на и.чформащ- онную пшну

код уТГрЕБ. .Я:ОщеГО CJtO

ва. При этом формирз ется сйх нал на втором выходе дейшфратоуа 22 адреса.-, открываете злемент И 24 и управляю - щеа слово поетулае ; на регистр 11, старший разряд которого управляет раf

3 ботой ког-мутаторов 6-8. Q

з;

,

В рабочем реяаше на ;.зход первого форнировате.ггя 16 импульсов через второй комментатор б поступают тактовые сигиальз err аппаратуры передачи данных 0 (АИД) с входа 37 сиггхронизацни приема. На вход второго фopьfflpoвaтejш 17 импульсов через третий коммутатор 7. поступают тактовые сигналы от ЛИД со входа 35 сшгхроиизации выдачи.

В дараллельпо-последопательпый преобразователь 2 и последовательно- паратшельньнЧ преобразователь 3 сигна лом иачалы/ых. устанойб т- (не показаны) устаназлизается код 10GOOODOO.

ШгфоркациЯ; пеобход1амагг для передачи в АЦП, поступает из зычислитель- иой машины по KHmopMajijroiJHOK шине 33.: При этом на вход, 29 ое ращения н вход 30 записи nocTynaiOT положительные ин- иульсы, а на адресиьпЧ ;8хо/ 32 достУ .пает код 00. На керном зыходе ..ешиф- ратора 22 адреса формируется единичный снгка.я и при наличии едз-гничного сигнала iia .гшшоде первого разряда регистра 13 через элемент И 23 осущест- Е, тггатся sam. ci- информаппч на ггерзый регистр 10 зь-дачи,

По сигналу кскца иуеоЕразованш; параллельно-последовате.г1ыюго преоб разователя 2 осуздествляетсрг запись Б прбобразова ель 2 кнформа.ции с регистра 10 н установка в единичное состояние триггера 14. Если в этот момеь-т оР/)ащение к устройстгу не производится 5 то сигнал с выхода триггера 14 через элемент И 27 устанавливает в единичное, состояние п.ервый разряд регистра 13,разрешая занись очередного информационного слова на регистр 10, Сигнал с выхода элемента И 27 через элемент 19 задержки устанав лива.ет в нулевое состояние триггер 1 Если при установке триггера 14 производилось обращение к устройству, то установка первого разряда регистра 13 в единичное состояние происходит после установки сигнала на входе 29 обращения в нулевое состояние.

Информация, принятая в преобразователь 2 с регистра 10, передается в АПД по тактоньП сигналам со входа 35 синхронизации вьщачи с информационного выхода 34.

Информация, поступающая от АПД с информационного входа 36, проходит через KOKTvjyraTop 8 на информационный вход последовательно-параллельного преобразователя 3, По накоплении информационного слова сигнал конца преобразования устанавливает в единич- ное состояние триггер 15 и записывает информацшо с информационного выхода преобразователя 3 на регистр 12 При этом в преобразователь 3 записывается код 10000000 и он снова готов принимать информацию.

Состояние триггера 15 записьтается на регистр 13 через элемент И.28 так же, как и состояние триггера 14 через элемент И 27. Установка триггера t5 в нулевое состояние происходит сигналом с выхода элемента И 28 через элемент 20 задержки.

Считывание информации с регистров

12и 13 осуществляется подачей положительных импульсов на вход 29 обращения и вход 31 считывания при нулевом коде на адресном входе 32. При этом на первом выходе дешифратора 22 адреса формируется единичньп сигнал,

(Который проходит через элемент И 26 иа соответствующий управллюш.ий вход пятого коммутатора 9, разрешая прохождение информации с регистров 12 и

13на информационную шину 33. Сигнал с выхода элемента Н 26 через элемент 21 задержки устанавливает в нулевое состояние регистр 13.

I

Взаимодействие вьиислительной машины с устроксгпом осуществляется следутогаим образом. За одно обращение

к устройству происходит вьщача информации и считывание информации.

Период обращения к устройству выбирается несколько меньше периода формирования сигнала конца преобразования преобразователей 2 и 3. Поэтому не при обращении из ycтpoйcтвa будет считываться информация, полученная от АПД, и не при каждом обращении устройству будет нужна очередная порция информации для передачи в АПД.

Наличие единичного сигнала во втором разряде регистра 13 означает, что на регистре 12 находится очередное информационное слово, принятое от АДЦ.

Наличие единичного сигнала в пер- ,вом разряде регистра 13 означает, что

информация, передаваемая из машины, принята на регистр 10 и к следующему обращению необходимо подготовить очередное информационное слово. .

Длительность задержки элемента 21

выбирается таким образом, чтобы регистр 13 установился в нулевое состояние до снятия единичного состояния сигнала на входе 29 обращения.

В режиме контроля, когда старший

разряд регистра 11 устанавливается в единичное состояние, информационный выход преобразователя 2 через коммутатор 8 поступает на информационный вход преобразователя 3. Таким обра

зом, информация, переданная из вычис

лительной машины, возвращается обратно и создается возможность организации сравнения принятой информации с переданной для определения правильности работы устройства.

В этом режиме работа преобразователей 2 и 3 тактируется сигналами с выхода коммутатора 5. На информационные входы коммутатора 5 поступают последователыюсти сигналов, соответствующие скорости передачи данных 1200, 2400 и 4800 бод, которые формируются делителем 4. Эти последовательности соответствуют реальным скоростям работы АПД и проверка может осуществляться на любой скорости.

Кроме того, подключение к информационным входам коммутатора 5 шин единичного и нулевого потенциалов устройства позволяет формировать такто

вую последовательность синхронно с обращениями к устройству .и осущестб лять контроль работы преобразователя 2 при каждом такте работы. Для гтой

цели имеется возможность передавать в машину 1 руппу cnrnajiofl с нпформацион- ных выходов преобразователя 2, уста, навливая на адресном входе 32 код 01, При этом сигнал с второго выхода дешифратора 22 адреса проходит через элемент И 25 на соответствугаищй управляющий вход пятого коммутатора 9 и разрешает прохождение сигналов группы информационных выходов преобразователя 2 на информационную тину 33.

Формула и 3 о б р а т е и и я 15

20

выходов обращения, записи, чтения вы- 30 дом записи нторо о буферного реглет- числительной машины, 1шформацио П1ьм вход первого буферного регистра является входом устройства для ПОДКЛЕ - чения к информацион1- ой-шине вычислительной машины,, а вхЬд залиси соеди- 35 ней с первым выходом распределителя управляющих сигналов, группа информационных выходов первого б5гфер1юго регистра соединена с группой информационных входов 1гараллел7л ю-последо 40 вателыюго преобразователя, инфориа- гщонный выход которого ;:1:лке ; :::я выходом устройства для подключения пн- формационного входа аппаратур-л передачи дапнь х, группа информациопньзх /js;, выходов последоват льно-1гараллспыюг о преобразователя соединена с.группой информационные: входов aroijoro буферного регистра., о т л и ч а ю щ е е , первы и второй выходы LTOporo фсфмирователя импул7 сов соединены со- отпетствепис с первьм и вторым син- хровходами параллельнс-посладователь- иого преобис13отз телЯ; групиа пкформа- цпонных выходов п зьпсод к:онца прообрЕЗОВаНИЯ KC i OpOrO СОЙД:1 1 НЫ COOTEtTст-зенпо с перБой группой иттфэрмацнои- пых входсн 11лте о коммутатора ; единичным входом второго тпт Т гера . выходы перпс/го и второго триггеров соедк- iKiKbi cooTBercTL- HMo с гсрлмыми входам первого и втор го элет теитсв Н, ныхо-. ды которьпс соь;дииеиь: соо цетственно с пегшы;. п вторым иифсрка/пюЕпгьгми ; входами pej trcTpa готогтюсти и соот- lie-rcTBGHHo через второй п г ;-етий эле- .ir-jrvt; з ;деряк1Г - с ;г .иеБЬ : к5 в г;эдамт- n:jpBorv) м ВТ :гол о TjJHrrepoiij 1г О; ой выход распределителя угграгилюдих сиг- соеднас н с влодоь; этлс: уаг-. гистра икфорыйгшояный вход

с я тем, что, с целью повышенг. , контролепригодности, устройство содержит пять коммутаторов 5 три эпемлн- та задержзси, регистр реясимал два формирователя 1Шпульсоо5 причем группа выходов делителя частоты сосди.чена с группой пнформацконных тжодов пер-- эого кoм iyтaтopa5 первый и ВТОРОЙ информациоппые н управляю -- xoTopbi o соецинепы соответ;:- чек.с О с

5

шИ1Е-а1-1И единичного и нулевого потеп- 1ПШЛОП устройства и ггер1зым вьосодог- periiCTpa уежгма, второй в .р-.од которого соединен с уаравлжоартми входами второго, третьего я четвертого ком.у таторов, выход первого коммутатора соединен с парвыг-г лпфор; ациоиным BJCC- дом второго коммутатора и через первый элемент за, ;,ержк - с первь ии- форг- ацноппым входом второго коммутатора, вторые информац :оп че входы рторого и третье Ч; коыиугаторов являются входами устройства для подкпюче-- 1П1я к выходам сн;пср : ймпульсов пркем и синхроимпульсе)у; зьздачи аппаратуры ьередачи данных соответственноj вкхо: - ды второго и третьего комг-гутаторов соединены соответстгзетП О с входам; первого и второго фop шpo:laтeлeй импульсов 5 первый и второй выходы пер- формироватш1Я импульсов coti.HHe- ны соотзетствелно с. ncpsf sM н торьм синхрсБХодами ;оследо1:-1тельно-парал 0 лельиого преобразователя, ииформадп- OHHbtsi вход которого сойдинен с выходом четвертого коммутатора, а выход ,a преоГ: разозат1Т1Л сседгиен с единичным входо;- пср;зого rpiirrepa it вхо0

дом записи нторо о буферного реглет-

, первы и второй выходы LTOporo фсфмирователя импул7 сов соединены со- отпетствепис с первьм и вторым син- хровходами параллельнс-посладователь- иого преобис13отз телЯ; групиа пкформа- цпонных выходов п зьпсод к:онца прообрЕЗОВаНИЯ KC i OpOrO СОЙД:1 1 НЫ COOTEtTст-зенпо с перБой группой иттфэрмацнои- пых входсн 11лте о коммутатора ; единичным входом второго тпт Т гера . выходы перпс/го и второго триггеров соедк- iKiKbi cooTBercTL- HMo с гсрлмыми входам первого и втор го элет теитсв Н, ныхо-. ды которьпс соь;дииеиь: соо цетственно с пегшы;. п вторым иифсрка/пюЕпгьгми ; входами pej trcTpa готогтюсти и соот- lie-rcTBGHHo через второй п г ;-етий эле- .ir-jrvt; з ;деряк1Г - с ;г .иеБЬ : к5 в г;эдамт- n:jpBorv) м ВТ :гол о TjJHrrepoiij 1г О; ой выход распределителя угграгилюдих сиг- соеднас н с влодоь; этлс: уаг-. гистра икфорыйгшояный вход

КО ГОриГО п выход 1 Я Г ОТ О jCO - ii iy r-iTOpa

соедине.; соочые.тс гне1 ко с ЕКОДОМ и ; ьп:одом устрсйстиа дл лодклгоченкя к я 1формад ;-/ н)й Ш1лле вычис; ;.ктель;/Ог; . ueps-bii:; и второй З пра.;зллюцне )ЦУ пятог о ком -п: т;1тот: соег П1епы

;C ;; VlJP -4 :TI eiT;jO с i UOT F . П ЕТ; вКТЫЧ

выходами распределителя управляющих сигналов, вторая группа информационных входов пятого коммутатора соединена с выходами второго буферного регистра и первым и вторым выходами регистра готовности, первый выход которого соединен с четвертым входом распределителя управляющих сигналов, пятый выход которого соединен с инверсными входами первого и второго |Элементов И, четвертый выход через четвертый г.лемент задержки соединен с установочные входом регистра готовности, адресный вход распределителя управляющих сигналов является входом устройства для подключения к адресной шине вычислительной машины, первый и второй информационные входы четвертого коьшутатора соединены соответственно с выходом и входом устройства Для подключения к информационным входу и выходу аппаратуры передачи данных

л-./

.17 {,-{fi/StfK)

И 5л Ц

ff-&ifU &ЫХ)

38 f SB-R 38-3

ffSji. W

управляющ11х сигналов содержит дешифратор адреса и четьфе элемента И, причем вход дешифратора адреса является адресным входом распределителя, первые входы первого, второго, третьего и четвертого элементов И объединены и являются первым входом и пятым выходом распределителя, вторые

0 входы первого и второго элементов И объединены и являются вторым входом распределителя, вторые входы третьего и четвертого элементов И объединены и являются третьим входом распре5 делителя, третьи входы первого и четвертого элементов И соединены с первым выходом дешифратора адреса, третьи входы второго и третьего элементов И соединены с вторым выходом де0 шифратора адреса, четвертый вход первого элемента И является четвёртым входом распределителя, выходы первого, второго, третьего и четвертого элементов И являются первым, вторым,

5 третьим и четвертым выходами распределителя .

У8SS fn i)

з8-()

J

Фи&.2

«6.15

HS jt. 16 (ё &й Выход)

Н5л. 1й

И 1б()

cix,6

| УСТРОЙСТВО ДЛЯ ВВОДА И ВЫВОДА ИНФОРМАЦИИ | 1972 |

|

SU423120A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1983 |

|

SU1140125A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-23—Публикация

1987-02-16—Подача