Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении систем передачи данных.

Целью изобретения является повышение достоверности работы устройства.

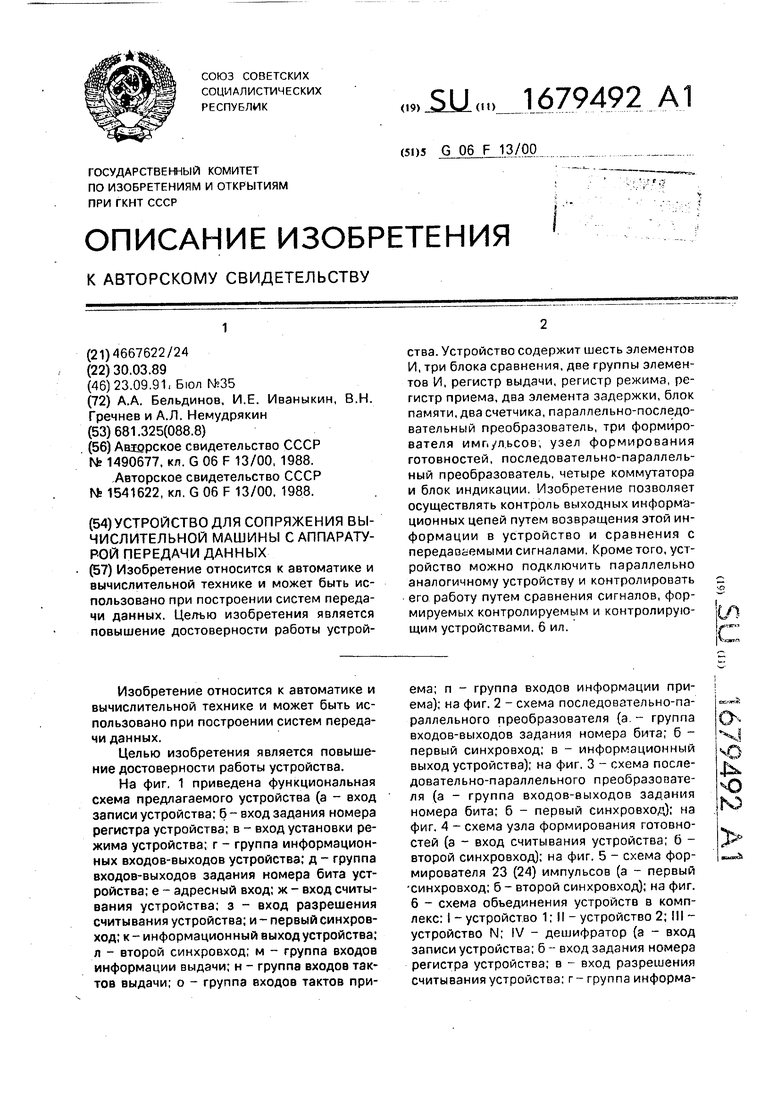

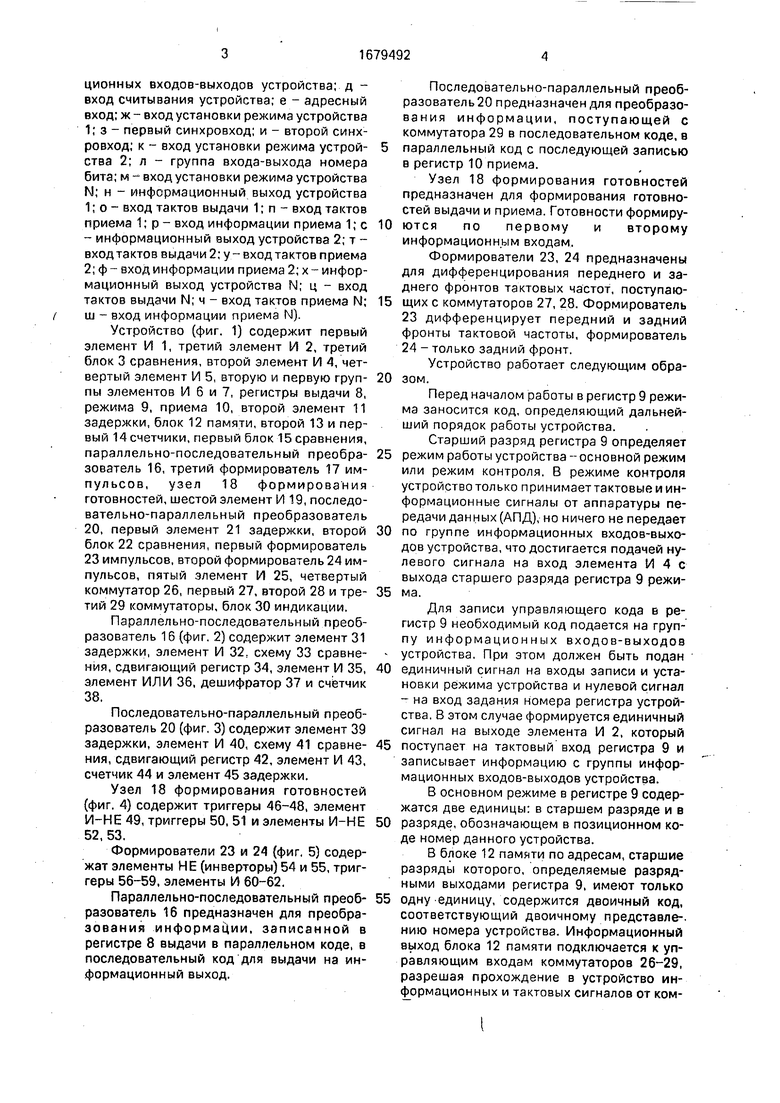

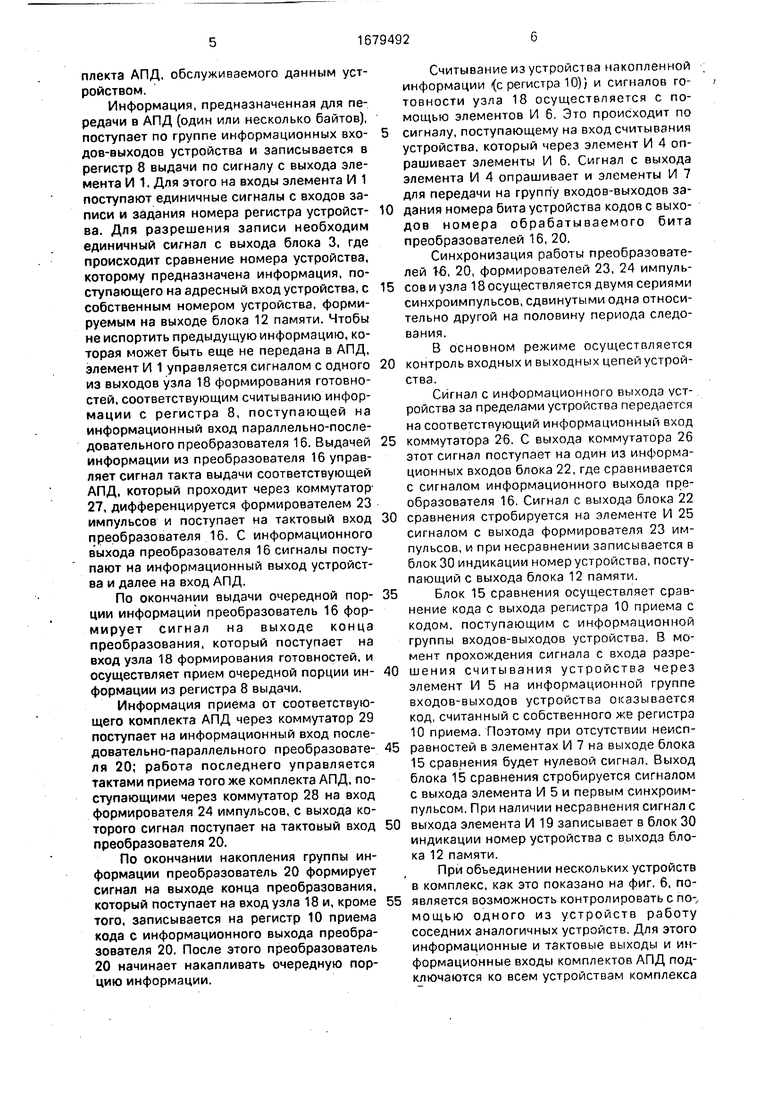

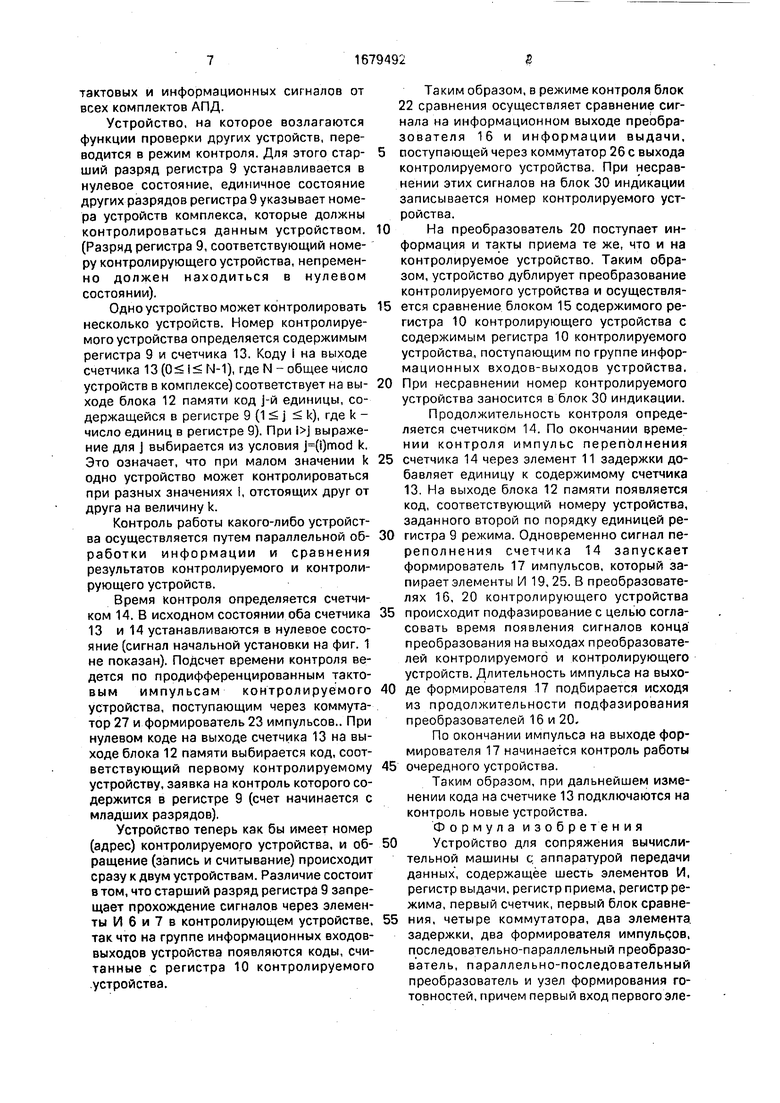

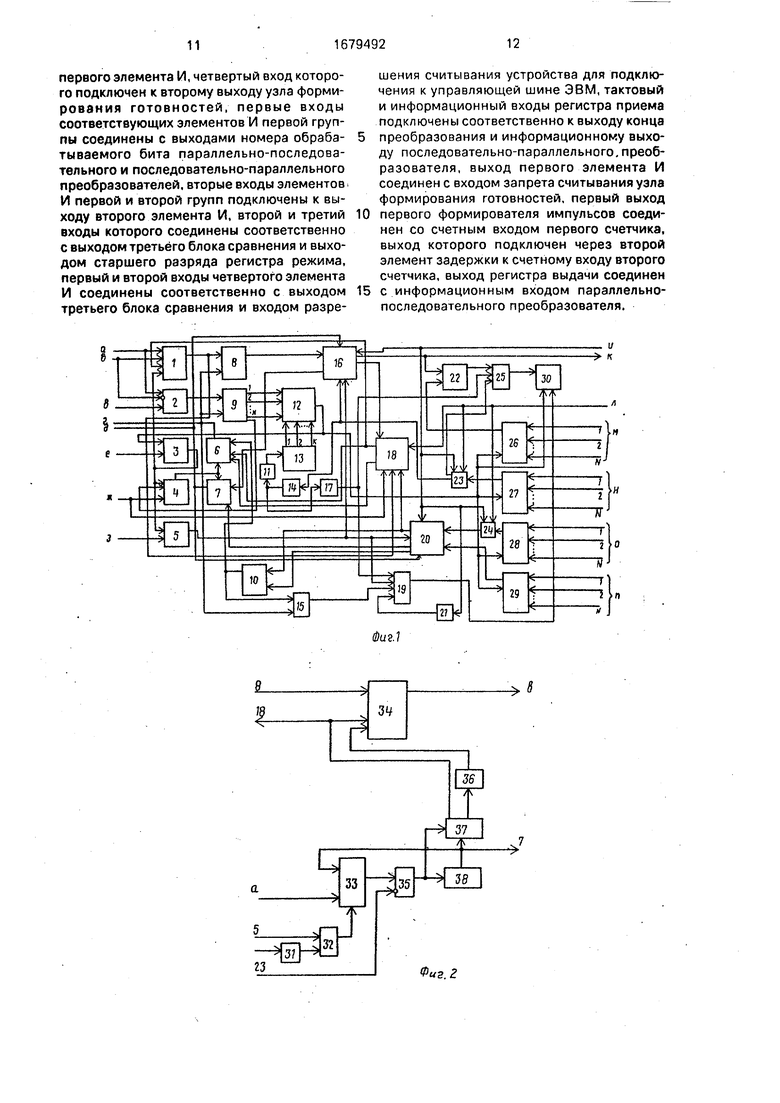

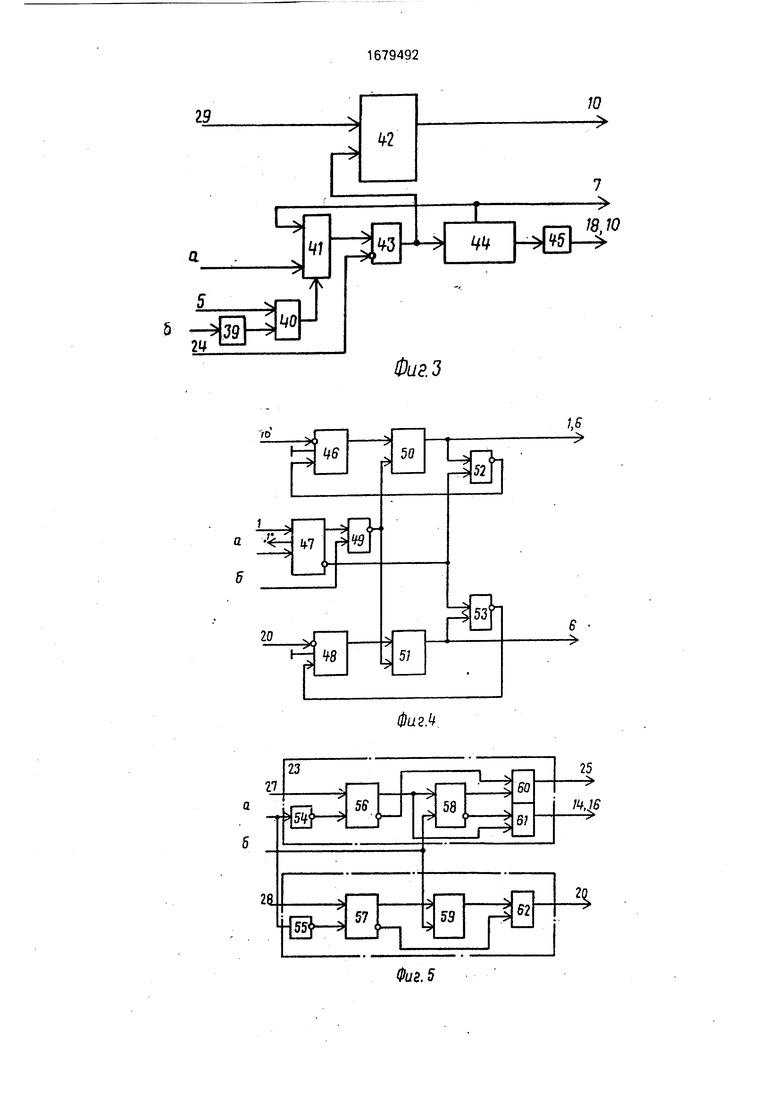

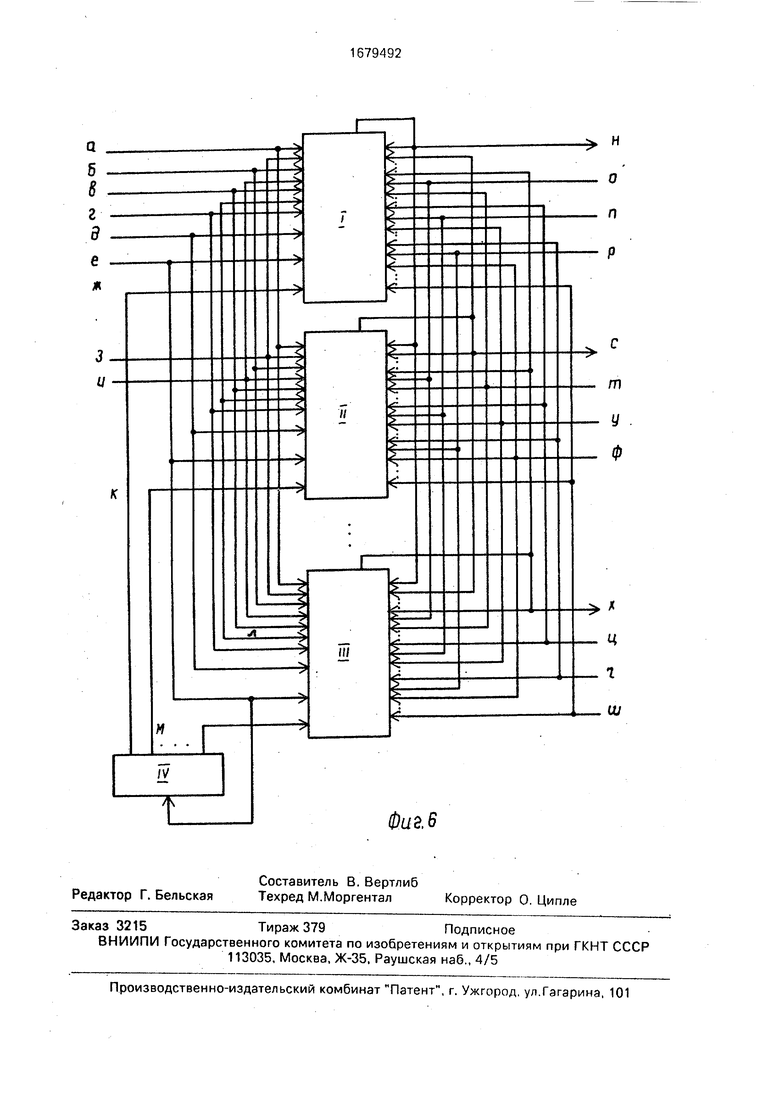

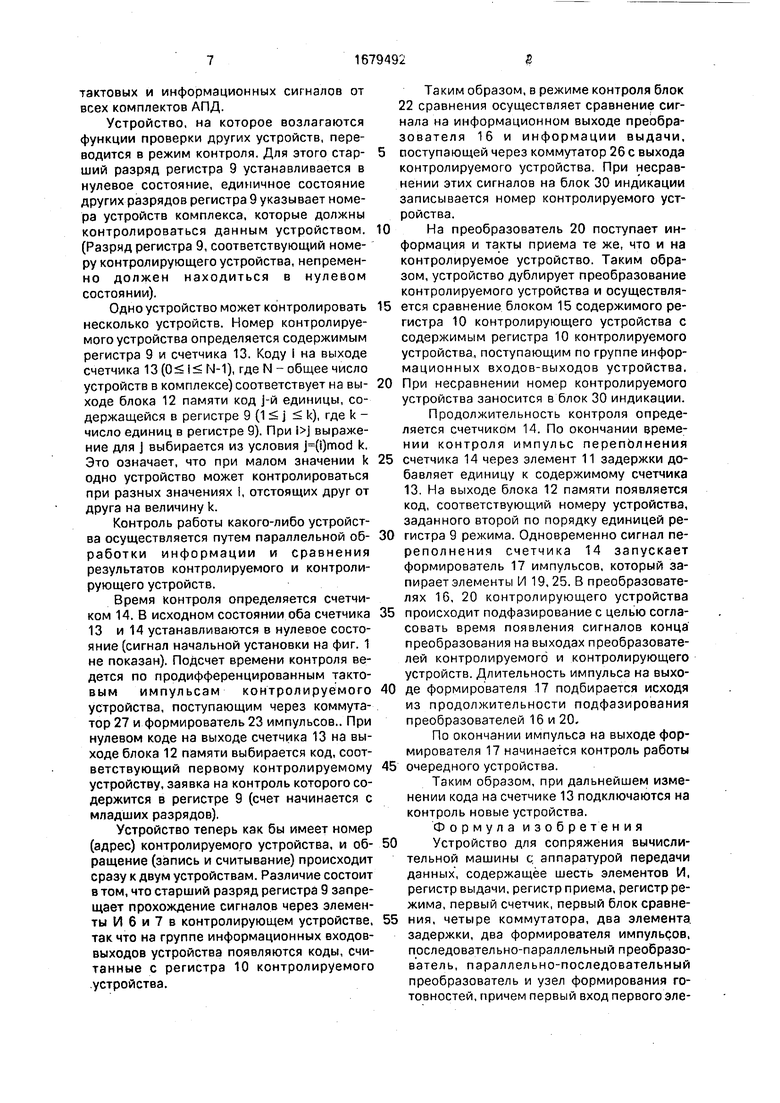

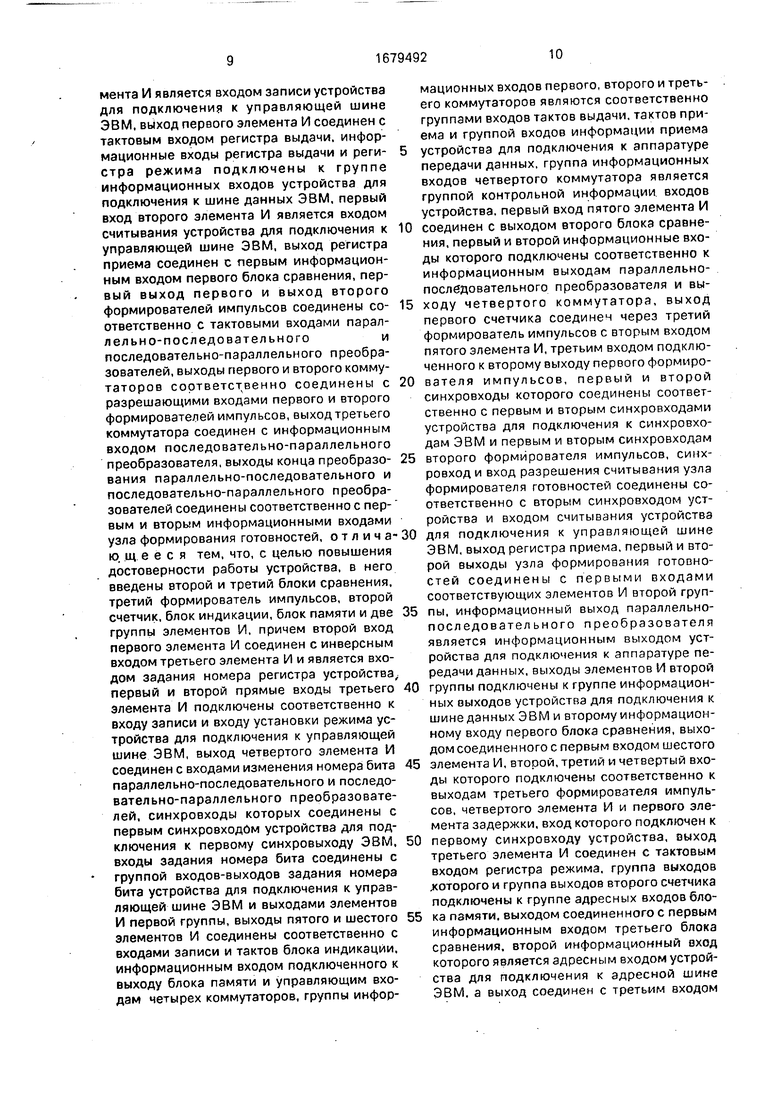

На фиг. 1 приведена функциональная схема предлагаемого устройства (а - вход записи устройства; б - вход задания номера регистра устройства; в - вход установки режима устройства; г - группа информационных входов-выходов устройства; д - группа входов-выходов задания номера бита устройства; е - адресный вход; ж - вход считывания устройства; з - вход разрешения считывания устройства; и - первый синхров- ход; к-информационный выход устройства; л - второй синхровход; м - группа входов информации выдачи; н - группа входов тактов выдачи; о - группа входов тактов приема; п - группа входов информации приема); на фиг. 2 - схема последовательно-параллельного преобразователя (а - группа входов-выходов задания номера бита; б - первый синхровход; в - информационный выход устройства); на фиг. 3 - схема последовательно-параллельного преобразователя (а - группа входов-выходов задания номера бита; б - первый синхровход); на фиг. 4 - схема узла формирования готовностей (а - вход считывания устройства; б - второй синхровход); на фиг. 5 - схема формирователя 23 (24) импульсов (а - первый синхровход; б - второй синхровход); на фиг. 6 - схема объединения устройств в комплекс: I - устройство 1; II - устройство 2; III - устройство N; IV - дешифратор (а - вход записи устройства; б - вход задания номера регистра устройства; в - вход разрешения считывания устройства; г - группа информаО-xj

О

ю

го

ционных входов-выходов устройства; д - вход считывания устройства; е - адресный вход; ж - вход установки режима устройства 1; з - первый синхровход; и - второй синх- ровход; к - вход установки режима устройства 2; л - группа входа-выхода номера бита; м - вход установки режима устройства N; н - информационный выход устройства 1; о - вход тактов выдачи 1; п - вход тактов приема 1; р - вход информации приема 1; с - информационный выход устройства 2; т - вход тактов выдачи 2; у- вход тактов приема 2; ф - вход информации приема 2; х - информационный выход устройства N; ц - вход тактов выдачи N; ч - вход тактов приема N; ш - вход информации приема N).

Устройство (фиг. 1) содержит первый элемент И 1, третий элемент И 2, третий блок 3 сравнения, второй элемент И 4, четвертый элемент И 5, вторую и первую группы элементов И 6 и 7, регистры выдачи 8, режима 9, приема 10, второй элемент 11 задержки, блок 12 памяти, второй 13 и первый 14 счетчики, первый блок 15 сравнения, параллельно-последовательный преобразователь 16, третий формирователь 17 импульсов, узел 18 формирования готовностей, шестой элемент И 19, последовательно-параллельный преобразователь 20, первый элемент 21 задержки, второй блок 22 сравнения, первый формирователь 23 импульсов, второй формирователь 24 импульсов, пятый элемент И 25, четвертый коммутатор 26, первый 27, второй 28 и третий 29 коммутаторы, блок 30 индикации.

Параллельно-последовательный преобразователь 16 (фиг. 2) содержит элемент 31 задержки, элемент И 32. схему 33 сравнения, сдвигающий регистр 34, элемент И 35, элемент ИЛИ 36, дешифратор 37 и счетчик 38.

Последовательно-параллельный преобразователь 20 (фиг. 3) содержит элемент 39 задержки, элемент И 40, схему 41 сравнения, сдвигающий регистр 42, элемент И 43, счетчик 44 и элемент 45 задержки.

Узел 18 формирования готовностей (фиг. 4) содержит триггеры 46-48, элемент И-НЕ 49, триггеры 50, 51 и элементы И-НЕ 52, 53.

Формирователи 23 и 24 (фиг. 5) содержат элементы НЕ (инверторы) 54 и 55, триггеры 56-59, элементы И 60-62.

Параллельно-последовательный преобразователь 16 предназначен для преобразования информации, записанной в регистре 8 выдачи в параллельном коде, в последовательный код для выдачи на информационный выход.

Последовательно-параллельный преобразователь 20 предназначен для преобразования информации, поступающей с коммутатора 29 в последовательном коде, в

параллельный код с последующей записью в регистр 10 приема.

Узел 18 формирования готовностей предназначен для формирования готовностей выдачи и приема. Готовности формиру0 ются по первому и второму информационным входам.

Формирователи 23, 24 предназначены для дифференцирования переднего и заднего фронтов тактовых частот, поступаю5 щих с коммутаторов 27, 28. Формирователь

23дифференцирует передний и задний фронты тактовой частоты, формирователь

24- только задний фронт.

Устройство работает следующим обра0 зом.

Перед началом работы в регистр 9 режима заносится код, определяющий дальнейший порядок работы устройства.

Старший разряд регистра 9 определяет

5 режим работы устройства - основной режим или режим контроля. В режиме контроля устройство только принимает тактовые и информационные сигналы от аппаратуры передачи данных (АПД), но ничего не передает

0 по группе информационных входов-выходов устройства, что достигается подачей нулевого сигнала на вход элемента И 4 с выхода старшего разряда регистра 9 режи5 ма.

Для записи управляющего кода в регистр 9 необходимый код подается на группу информационных входов-выходов - устройства, При этом должен быть подан

0 единичный сигнал на входы записи и установки режима устройства и нулевой сигнал - на вход задания номера регистра устройства, В этом случае формируется единичный сигнал на выходе элемента И 2, который

5 поступает на тактовый вход регистра 9 и записывает информацию с группы информационных входов-выходов устройства.

В основном режиме в регистре 9 содержатся две единицы: в старшем разряде и в

0 разряде, обозначающем в позиционном коде номер данного устройства.

В блоке 12 памяти по адресам, старшие разряды которого, определяемые разрядными выходами регистра 9, имеют только

5 одну единицу, содержится двоичный код, соответствующий двоичному представле-. нию номера устройства. Информационный выход блока 12 памяти подключается к управляющим входам коммутаторов 26-29, разрешая прохождение в устройство информационных и тактовых сигналов от комплекта АПД, обслуживаемого данным устройством.

Информация, предназначенная для передачи в АПД (один или несколько байтов), поступает по группе информационных вхо- дов-выходов устройства и записывается в регистр 8 выдачи по сигналу с выхода элемента И 1. Для этого на входы элемента И 1 поступают единичные сигналы с входов записи и задания номера регистра устройст- ва. Для разрешения записи необходим единичный сигнал с выхода блока 3, где происходит сравнение номера устройства, которому предназначена информация, поступающего на адресный вход устройства, с собственным номером устройства, формируемым на выходе блока 12 памяти. Чтобы не испортить предыдущую информацию, которая может быть еще не передана в АПД, элемент И 1 управляется сигналом с одного из выходов узла 18 формирования готовно- стей, соответствующим считыванию информации с регистра 8, поступающей на информационный вход параллельно-последовательного преобразователя 16. Выдачей информации из преобразователя 16 управляет сигнал такта выдачи соответствующей АПД, который проходит через коммутатор 27, дифференцируется формирователем 23 импульсов и поступает на тактовый вход преобразователя 16. С информационного выхода преобразователя 16 сигналы поступают на информационный выход устройства и далее на вход АПД.

По окончании выдачи очередной пор- ции информации преобразователь 16 формирует сигнал на выходе конца преобразования, который поступает на вход узла 18 формирования готовностей, и осуществляет прием очередной порции ин- формации из регистра 8 выдачи.

Информация приема от соответствующего комплекта АПД через коммутатор 29 поступает на информационный вход последовательно-параллельного преобразовате- ля 20; работа последнего управляется тактами приема того же комплекта АПД, поступающими через коммутатор 28 на вход формирователя 24 импульсов, с выхода которого сигнал поступает на тактовый вход преобразователя 20.

По окончании накопления группы информации преобразователь 20 формирует сигнал на выходе конца преобразования, который поступает на вход узла 18 и, кроме того, записывается на регистр 10 приема кода с информационного выхода преобразователя 20. После этого преобразователь 20 начинает накапливать очередную порцию информации.

Считывание из устройства накопленной информации (с регистра 10)} и сигналов готовности узла 18 осуществляется с помощью элементов И 6. Это происходит по сигналу, поступающему на вход считывания устройства, который через элемент И 4 опрашивает элементы И 6. Сигнал с выхода элемента И 4 опрашивает и элементы И 7 для передачи на группу входов-выходов задания номера бита устройства кодов с выходов номера обрабатываемого бита преобразователей 16, 20.

Синхронизация работы преобразователей 16, 20, формирователей 23, 24 импульсов и узла 18осуществляется двумя сериями синхроимпульсов, сдвинутыми одна относительно другой на половину периода следования.

В основном режиме осуществляется контроль входных и выходных цепей устройства.

Сигнал с информационного выхода устройства за пределами устройства передается

на соответствующий информационный вход коммутатора 26. С выхода коммутатора 26 этот сигнал поступает на один из информационных входов блока 22, где сравнивается с сигналом информационного выхода преобразователя 16. Сигнал с выхода блока 22 сравнения стробируется на элементе И 25 сигналом с выхода формирователя 23 импульсов, и при несравнении записывается в блок 30 индикации номер устройства, поступающий с выхода блока 12 памяти.

Блок 15 сравнения осуществляет сравнение кода с выхода регистра 10 приема с кодом, поступающим с информационной группы входов-выходов устройства. В момент прохождения сигнала с входа разрешения считывания устройства через элемент И 5 на информационной группе входов-выходов устройства оказывается код, считанный с собственного же регистра 10 приема. Поэтому при отсутствии неисправностей в элементах И 7 на выходе блока 15 сравнения будет нулевой сигнал. Выход блока 15 сравнения стробируется сигналом с выхода элемента И 5 и первым синхроимпульсом. При наличии несравнения сигнал с выхода элемента И 19 записывает в блок 30 индикации номер устройства с выхода блока 12 памяти.

При объединении нескольких устройств в комплекс, как это показано на фиг. 6, появляется возможность контролировать с по- мощью одного из устройств работу соседних аналогичных устройств. Для этого информационные и тактовые выходы и информационные входы комплектов АПД подключаются ко всем устройствам комплекса

тактовых и информационных сигналов от всех комплектов АПД.

Устройство, на которое возлагаются функции проверки других устройств, переводится в режим контроля. Для этого старший разряд регистра 9 устанавливается в нулевое состояние, единичное состояние других разрядов регистра 9 указывает номера устройств комплекса, которые должны контролироваться данным устройством. (Разряд регистра 9, соответствующий номеру контролирующего устройства, непременно должен находиться в нулевом состоянии).

Одно устройство может контролировать несколько устройств. Номер контролируемого устройства определяется содержимым регистра 9 и счетчика 13. Коду i на выходе счетчика 13(0 i N-1), где N - общее число устройств в комплексе) соответствует на выходе блока 12 памяти код j-й единицы, содержащейся в регистре 9 (1 j k), где k - число единиц в регистре 9). При выражение для J выбирается из условия j(i)mod k. Это означает, что при малом значении k одно устройство может контролироваться при разных значениях 1, отстоящих друг от друга на величину k.

Контроль работы какого-либо устройства осуществляется путем параллельной обработки информации и сравнения результатов контролируемого и контролирующего устройств.

Время контроля определяется счетчиком 14. В исходном состоянии оба счетчика 13 и 14 устанавливаются в нулевое состояние (сигнал начальной установки на фиг. 1 не показан). Подсчет времени контроля ведется по продифференцированным тактовым импульсам контролируемого устройства, поступающим через коммутатор 27 и формирователь 23 импульсов.. При нулевом коде на выходе счетчика 13 на выходе блока 12 памяти выбирается код, соответствующий первому контролируемому устройству, заявка на контроль которого содержится в регистре 9 (счет начинается с младших разрядов).

Устройство теперь как бы имеет номер (адрес) контролируемого устройства, и обращение (запись и считывание) происходит сразу к двум устройствам. Различие состоит в том, что старший разряд регистра 9 запрещает прохождение сигналов через элементы И 6 и 7 в контролирующем устройстве, так что на группе информационных входов- выходов устройства появляются коды, считанные с регистра 10 контролируемого устройства.

Таким образом, в режиме контроля блок 22 сравнения осуществляет сравнение сигнала на информационном выходе преобразователя 16 и информации выдачи,

поступающей через коммутатор 26 с выхода контролируемого устройства. При несравнении этих сигналов на блок 30 индикации записывается номер контролируемого устройства.

0 На преобразователь 20 поступает информация и такты приема те же, что и на контролируемое устройство. Таким образом, устройство дублирует преобразование контролируемого устройства и осуществля5 ется сравнение блоком 15 содержимого регистра 10 контролирующего устройства с содержимым регистра 10 контролируемого устройства, поступающим по группе информационных входов-выходов устройства.

0 При несравнении номер контролируемого устройства заносится в блок 30 индикации. Продолжительность контроля определяется счетчиком 14. По окончании време- нии контроля импульс перепЬлнения

5 счетчика 14 через элемент 11 задержки добавляет единицу к содержимому счетчика 13. На выходе блока 12 памяти появляется код, соответствующий номеру устройства, заданного второй по порядку единицей ре0 гистра 9 режима. Одновременно сигнал переполнения счетчика 14 запускает формирователь 17 импульсов, который запирает элементы И 19, 25. В преобразователях 16, 20 контролирующего устройства

5 происходит подфазирование с целью согласовать время появления сигналов конца преобразования на выходах преобразователей контролируемого и контролирующего устройств. Длительность импульса на выхо0 де формирователя 17 подбирается исходя из продолжительности подфазирования преобразователей 16 и 20.

По окончании импульса на выходе формирователя 17 начинается контроль работы

5 очередного устройства.

Таким образом, при дальнейшем изменении кода на счетчике 13 подключаются на контроль новые устройства.

Формула изобретения

0 Устройство для сопряжения вычислительной машины с аппаратурой передачи данных, содержащее шесть элементов И, регистр выдачи, регистр приема, регистр режима, первый счетчик, первый блок сравне5 ния, четыре коммутатора, два элемента задержки, два формирователя импульсов, последовательно-параллельный преобразователь, параллельно-последовательный преобразователь и узел формирования го- товностей, причем первый вход первого элемента И является входом записи устройства для подключения к управляющей шине ЭВМ, выход первого элемента И соединен с тактовым входом регистра выдачи, информационные входы регистра выдачи и реги- стра режима подключены к группе информационных входов устройства для подключения к шине данных ЭВМ, первый вход второго элемента И является входом считывания устройства для подключения к управляющей шине ЭВМ, выход регистра приема соединен с первым информационным входом первого блока сравнения, первый выход первого и выход второго формирователей импульсов соединены со- ответственно с тактовыми входами параллельно-последовательногоипоследовательно-параллельного преобразователей, выходы первого и второго коммутаторов соответственно соединены с разрешающими входами первого и второго формирователей импульсов, выход третьего коммутатора соединен с информационным входом последовательно-параллельного преобразователя, выходы конца преобразо- вания параллельно-последовательного и последовательно-параллельного преобразователей соединены соответственно с первым и вторым информационными входами узла формирования готовностей, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности работы устройства, в него введены второй и третий блоки сравнения, третий формирователь импульсов, второй счетчик, блок индикации, блок памяти и две группы элементов И, причем второй вход первого элемента И соединен с инверсным входом третьего элемента И и является входом задания номера регистра устройства первый и второй прямые входы третьего элемента И подключены соответственно к входу записи и входу установки режима устройства для подключения к управляющей шине ЭВМ, выход четвертого элемента И соединен с входами изменения номера бита параллельно-последовательного и последовательно-параллельного преобразователей, синхровходы которых соединены с первым синхровходом устройства для подключения к первому синхровыходу ЭВМ, входы задания номера бита соединены с группой входов-выходов задания номера бита устройства для подключения к управляющей шине ЭВМ и выходами элементов И первой группы, выходы пятого и шестого элементов И соединены соответственно с входами записи и тактов блока индикации, информационным входом подключенного к выходу блока памяти и управляющим входам четырех коммутаторов, группы информационных входов первого, второго и третьего коммутаторов являются соответственно группами входов тактов выдачи, тактов приема и группой входов информации приема устройства для подключения к аппаратуре передачи данных, группа информационных входов четвертого коммутатора является группой контрольной информации входов устройства, первый вход пятого элемента И соединен с выходом второго блока сравнения, первый и второй информационные входы которого подключены соответственно к информационным выходам параллельно- последовательного преобразователя и выходу четвертого коммутатора, выход первого счетчика соединен через третий формирователь импульсов с вторым входом пятого элемента И, третьим входом подключенного к второму выходу первого формиро- вателя импульсов, первый и второй синхровходы которого соединены соответственно с первым и вторым синхровходами устройства для подключения к синхровхо- дам ЭВМ и первым и вторым синхровходам второго формирователя импульсов, синх- ровход и вход разрешения считывания узла формирователя готовностей соединены соответственно с вторым синхровходом устройства и входом считывания устройства для подключения к управляющей шине ЭВМ, выход регистра приема, первый и второй выходы узла формирования готооно- стей соединены с первыми входами соответствующих элементов И второй группы, информационный выход параллельно- последовательного преобразователя является информационным выходом устройства для подключения к аппаратуре передачи данных, выходы элементов И второй группы подключены к группе информационных выходов устройства для подключения к шине данных ЭВМ и второму информационному входу первого блока сравнения, выходом соединенного с первым входом шестого элемента И, второй, третий и четвертый входы которого подключены соответственно к выходам третьего формирователя импульсов, четвертого элемента И и первого элемента задержки, вход которого подключен к первому синхровходу устройства, аыход третьего элемента И соединен с тактовым входом регистра режима, группа выходов .которого и группа выходов второго счетчика подключены к группе адресных входов блока памяти, выходом соединенного с первым информационным входом третьего блока сравнения, второй информационный вход которого является адресным входом устройства для подключения к адресной шине ЭВМ. а выход соединен с третьим входом

первого элемента И, четвертый вход которого подключен к второму выходу узла форми- рования готовностей, первые входы соответствующих элементов И первой группы соединены с выходами номера обрабатываемого бита параллельно-последовательного и последовательно-параллельного преобразователей, вторые входы элементов И первой и второй групп подключены к выходу второго элемента И, второй и третий входы которого соединены соответственно с выходом третьего блока сравнения и выходом старшего разряда регистра режима, первый и второй входы четвертого элемента И соединены соответственно с выходом третьего блока сравнения и входом разре0

5

шения считывания устройства для подключения к управляющей шине ЭВМ, тактовый и информационный входы регистра приема подключены соответственно к выходу конца преобразования и информационному выходу последовательно-параллельного, преобразователя, выход первого элемента И соединен с входом запрета считывания узла формирования готовностей, первый выход первого формирователя импульсов соединен со счетным входом первого счетчика, выход которого подключен через второй элемент задержки к счетному входу второго счетчика, выход регистра выдачи соединен с информационным входом параллельно- последовательного преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с аппаратурой передачи данных | 1988 |

|

SU1541622A1 |

| Устройство для сопряжения вычислительной машины с аппаратурой передачи данных | 1987 |

|

SU1439604A1 |

| Многоканальное устройство дляпЕРЕдАчи и пРиЕМА диСКРЕТНОй иН-фОРМАции | 1972 |

|

SU832752A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для ввода информации | 1983 |

|

SU1109732A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1520531A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1462315A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении систем передачи данных. Целью изобретения является повышение достоверности работы устройства. Устройство содержит шесть элементов И, три блока сравнения, две группы элементов И, регистр выдачи, регистр режима, регистр приема, два элемента задержки, блок памяти,два счетчика, параллельно-последовательный преобразователь, три формирователя имп/льсов, узел формирования готовностей, последовательно-параллельный преобразователь, четыре коммутатора и блок индикации. Изобретение позволяет осуществлять контроль выходных информационных цепей путем возвращения этой информации в устройство и сравнения с передаваемыми сигналами. Кроме того, устройство можно подключить параллельно аналогичному устройству и контролировать его работу путем сравнения сигналов, формируемых контролируемым и контролирующим устройствами.6 ил. Л |«-тг,-, |С

Фиг. 2

а 6

| Устройство для сопряжения абонента с каналом передачи данных | 1988 |

|

SU1490677A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения вычислительной машины с аппаратурой передачи данных | 1988 |

|

SU1541622A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1991-09-23—Публикация

1989-03-30—Подача