Изобретение относится к вычисли™ тельной технике, в частности к запоминающим устройствам, может быть использовано при изготовлении и испытании блоков памяти и является усовершенствованием изобретения по К 1365134.

Целью изобретения является расширение области применения устройства за счет увеличения парка проверяемых блоков памяти.

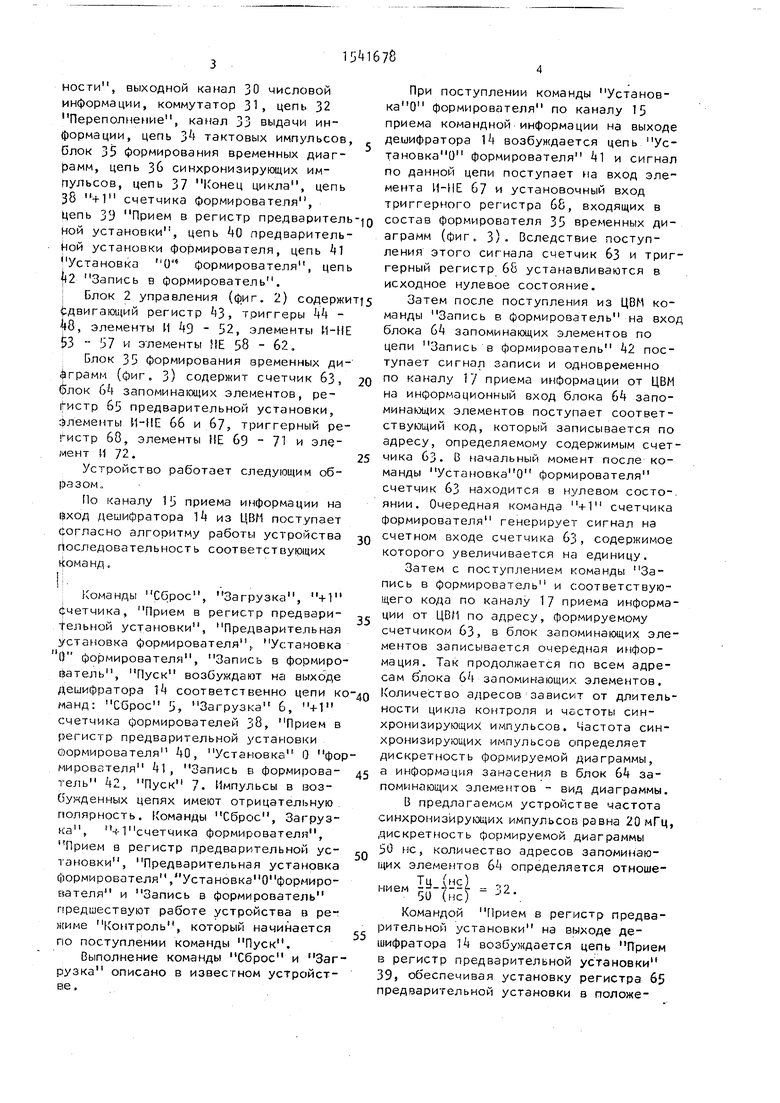

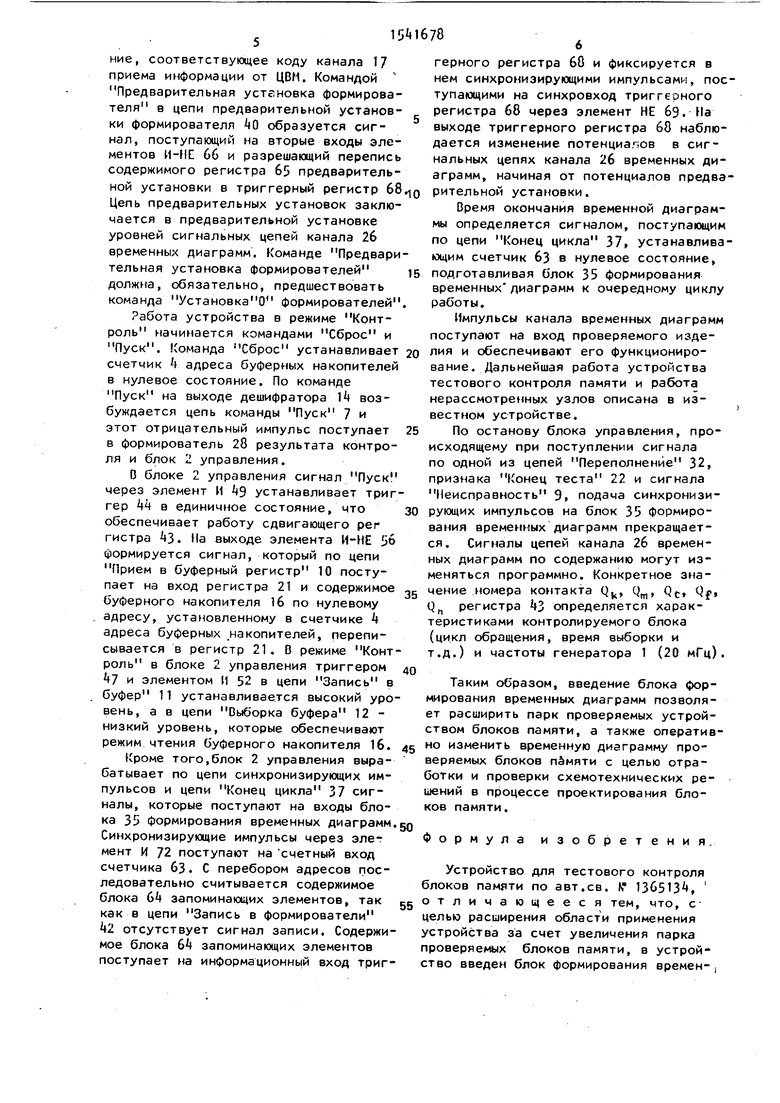

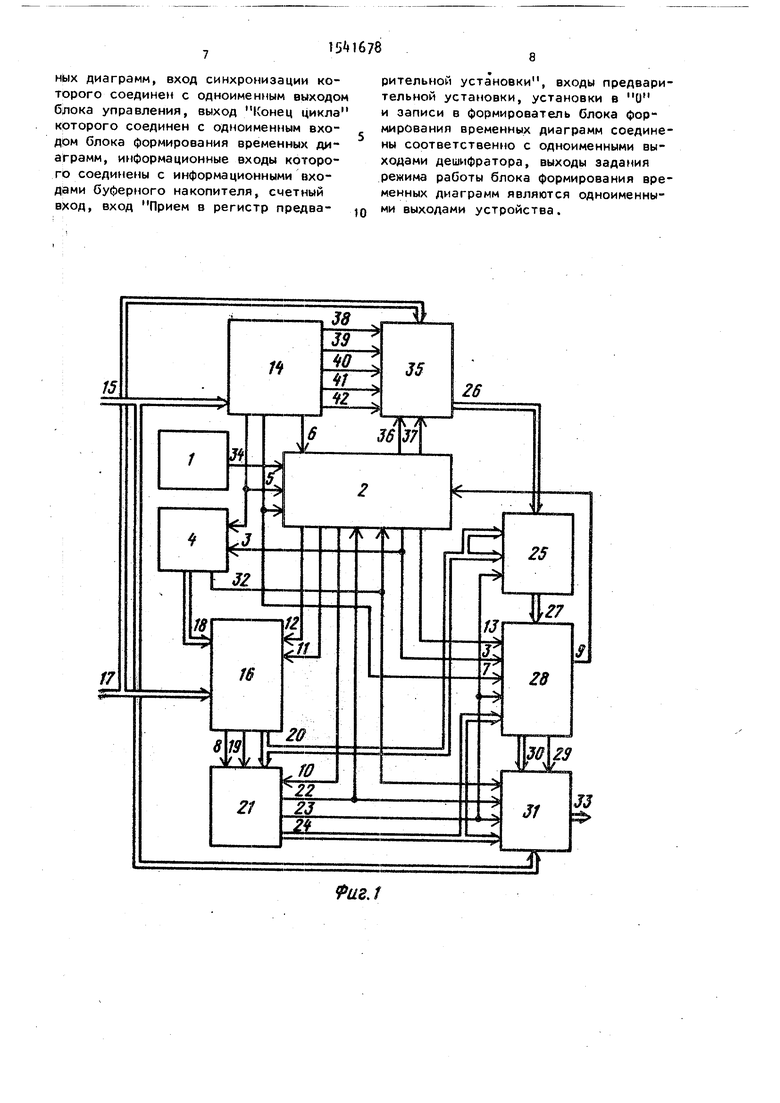

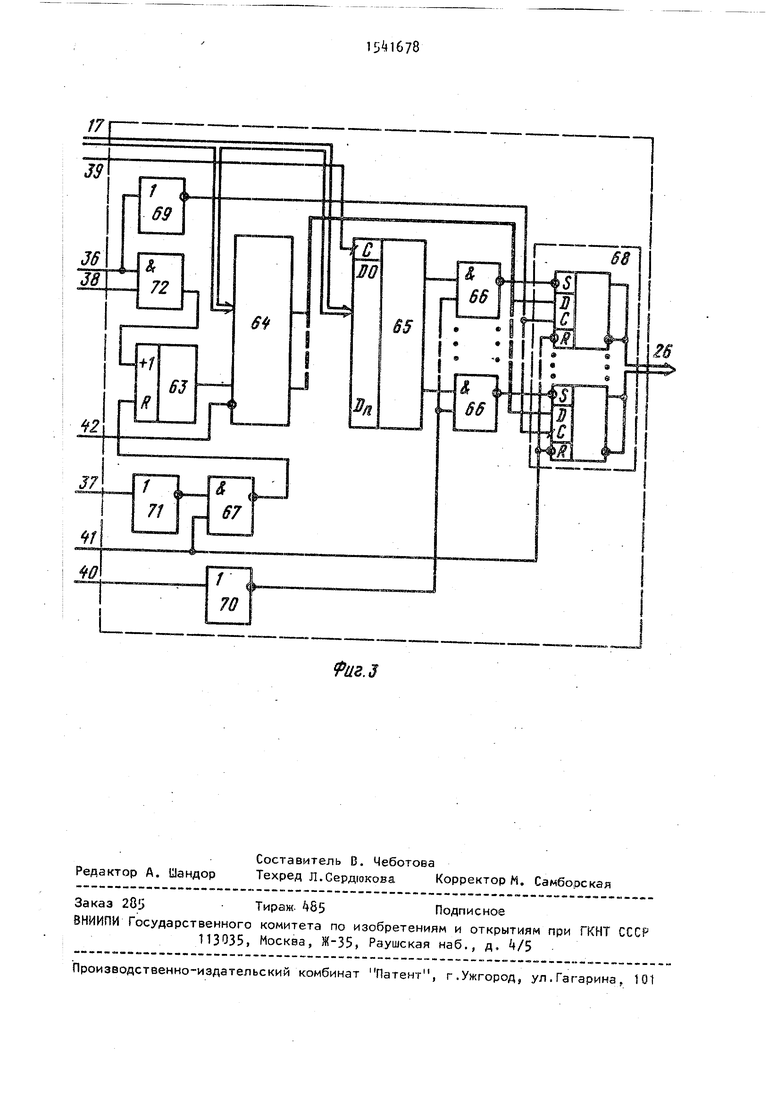

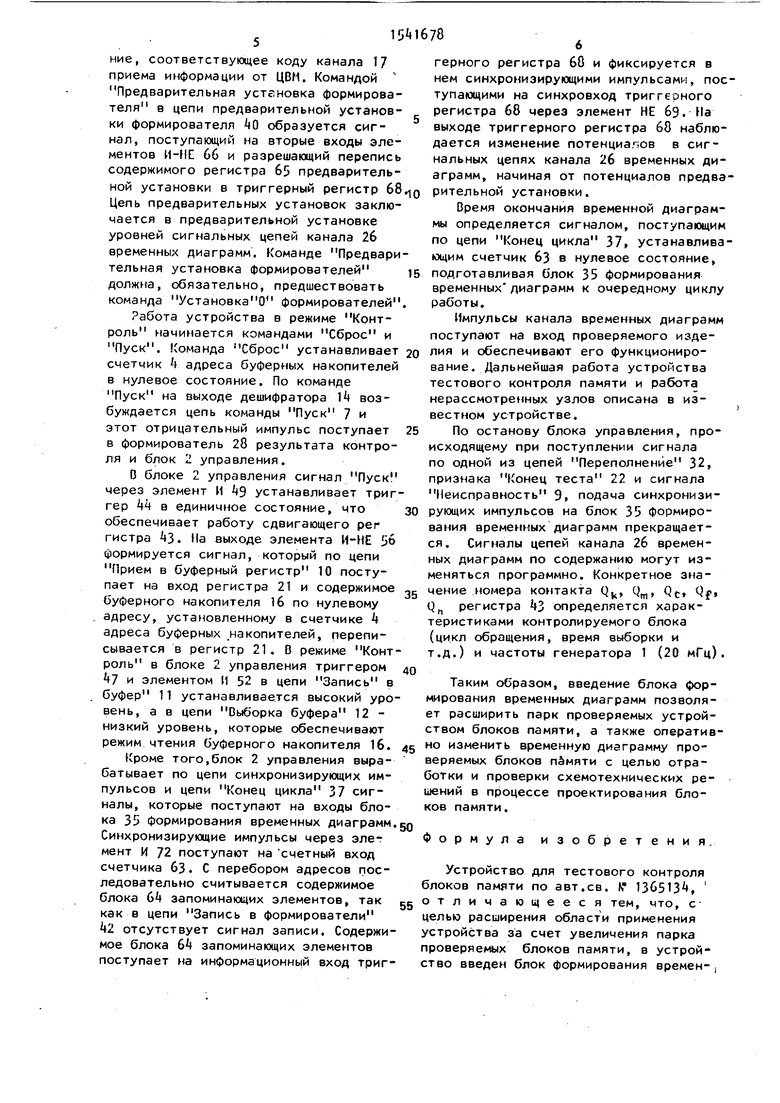

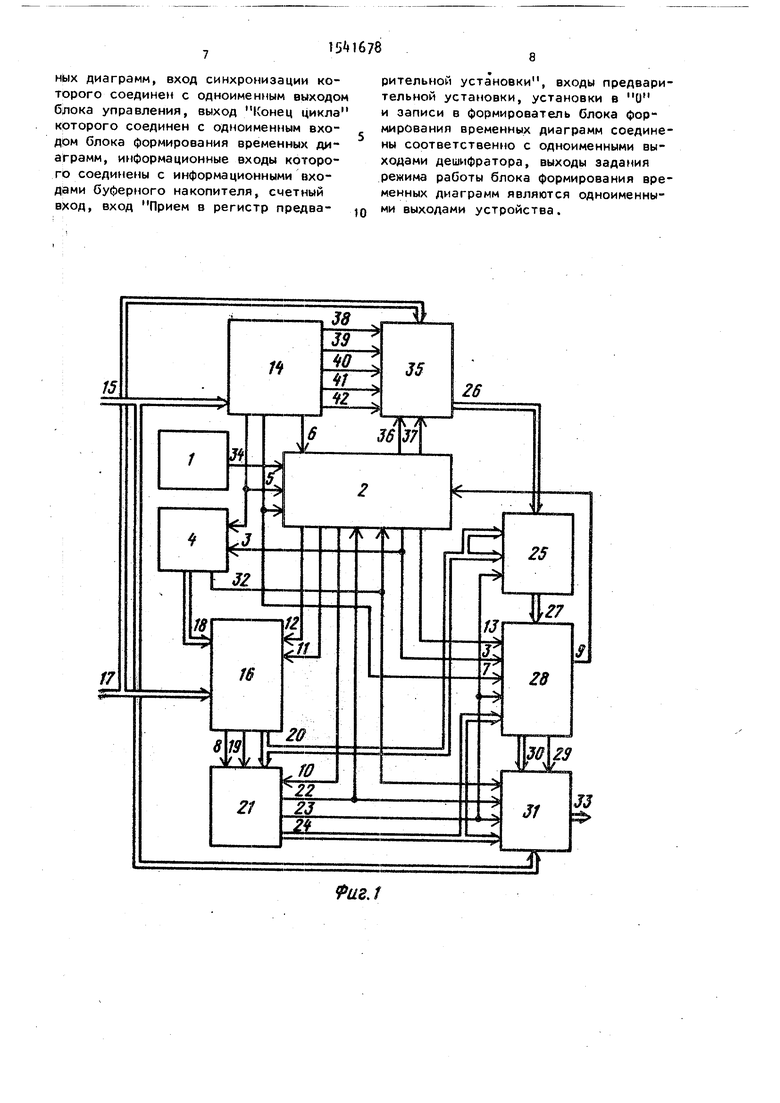

На фиг. 1 представлена схема устройства для тестового контроля блоков памяти; на фиг. 2 - схема блока управления; на фиг. 3 схема блока формирования временных диаграмм.

Устройство для тестового контроля блоков памяти содержит генератор 1, блок 2 управления, цепь 3 СИ1, счетчик 4 адреса буферных накопителей, цепь 5 команды Сброс, цепь 6 команды Загрузка, цепь 7 команды Пуск, цепь 8 буферного накопителя

признака Конец теста, цепь 9 сигнала Неисправность, цепь 10 сигнала Прием в буферный регистр, цепь 11 сигнала Запись в буфер, цепь 12 сигнала Вьйорка буфера, цепь 13 сигнала Опрос схемы сравнения, дешифратор 14, канал 15 приема командной информации, буферный накопитель 16, канал 17 приема информации от ЦОМ, канал 18 счетиика адреса буферных накопителей, цепь 19 информации режима обращения буферного накопителя, канал 20 адресной и числовой информации буферного накопителя, регистр 21, цепь 22 признака Конец теста регистра, цепь 23 информации режима обращения регистра, канал 24 адресной и числовой информации регистра, проверяемое изделие 25, выход 26 задания режима, входной канал 27 числовой информации, формирователь 28 результатов контроля, цепь 29 Триггер неисправ

00

кэ

носги, выходной канал 30 числовой информации, коммутатор 31, цепь 32 Переполнение, канал 33 выдачи информации, цепь 34 тактовых импульсов, блок 35 формирования временных диаграмм, цепь 36 синхронизирующих импульсов, цепь 37 Конец цикла, цепь 38 +1 счетчика формирователя, Цепь ЗУ Прием в регистр предваритель Ной установки, цепь 40 предварительной установки формирователя, цепь 41 Установка О формироватепя, цепь 42 Запись в формирователь.

Блок 2 управления (фиг. 2) содержи двигающий регистр 43, триггеры 44 - 48, элементы И 49 - 52, элементы И-НЕ Ј3 - 57 и элементы НЕ 58 - 62.

Блок 35 формирования временных ди- фграмм (фиг. 3) содержит счетчик 63 , блок 64 запоминающих элементов, регистр 65 предварительной установки, Элементы И-НС 66 и 67, триггерный регистр 68, элементы НЕ 69 71 и элемент И /2.

Устройство работает следующим образом.

По каналу 15 приема информации на йход дешифратора 1 из ЦВМ поступает Согласно алгоритму работы устройства Нюследовательность соответствующих

команд, I

Команды Сброс, Загрузка, +1 Счетчика, Прием в регистр предвари- тельной установки, Предварительная установка формирователя, Установка (} формирователя, Запись в формиро- Е атель, Пуск возбуждают на выходе дешифратора 14 соответственно цепи ко манд: Сброс 5, Загрузка 6, +1 счетчика формирователей 38, Прием в регистр предварительной установки оормирователя 40, Установка 0 формирователя 41, Запись в формирова- гель 42, Пуск 7. Импульсы в возбужденных цепях имеют отрицательную полярность. Команды Сброс, Загрузка, счетчика формирователя, Прием в регистр предварительной ус- тановки, Предварительная установка формирователя,Установка 0 формиро- Е ателя и Запись в формирователь предшествуют работе устройства в ре- миме Контроль, который начинается по поступлении команды Пуск.

Выполнение команды Сброс и Загрузка описано в известном устройстве .

При поступлении команды Установка формирователя по каналу 15 приема командной информации на выходе дешифратора 14 возбуждается цепь Ус- тановка 0 формирователя 41 и сигнал по данной цепи поступает на вход элемента И-НЕ 67 и установочный вход триггерного регистра 68, входящих в состав формирователя 35 временных диаграмм (фиг. 3) « Вследствие поступления этого сигнала счетчик 63 и триггерный регистр 68 устанавливаются в исходное нулевое состояние.

Затем после поступления из ЦВМ команды Запись в формирователь на вхо блока 64 запоминающих элементов по цепи Запись в формирователь 42 поступает сигнал записи и одновременно по каналу 17 приема информации от ЦВМ на информационный вход блока 64 запоминающих элементов поступает соответствующий код, который записывается по адресу, определяемому содержимым счетчика 63. В начальный момент после команды Установка 0 формирователя счетчик 63 находится в нулевом состоянии. Очередная команда +1 счетчика формирователя генерирует сигнал на счетном входе счегчика 63, содержимое которого увеличивается на единицу.

Затем с поступлением команды Запись в формирователь и соответствующего кода по каналу 1/ приема информации от ЦВМ по адресу, формируемому счетчиком 63, в блок запоминающих элементов записывается очередная информация. Так продолжается по всем адресам блока 64 запоминающие элементов. Количество адресов зависит от длительности цикла контроля и частоты синхронизирующих импульсов. Частота синхронизирующих импульсов определяет дискретность формируемой диаграммы, а информация занесения в блок 64 запоминающих элементов - вид диаграммы.

В предлагаемом устройстве частота синхронизирующих импульсов равна 20 мГц дискретность формируемой диаграммы 50 не, количество адресов запоминающих элементов 64 определяется отноше № -

Командой Прием в регистр предварительной установки на выходе дешифратора 14 возбуждается цепь Прием в регистр предварительной установки 39, обеспечивая установку регистра 65 предварительной установки в положение, соответствующее коду канала 17 приема информации от ЦВМ. Командой Предварительная установка формирователя в цепи предварительной установки формирователя 40 образуется сигнал, поступающий на вторые входы элементов И-НЕ 66 и разрешающий перепись содержимого регистра 65 предварительгерного регистра 60 и нем синхронизирующими тупающими на синхровх регистра 68 через эле выходе триггерного ре дается изменение поте нальных цепях канала аграмм, начиная от по

ной установки в триггерный регистр рительной установки.

Цепь предварительных установок заключается в предварительной установке уровней сигнальных цепей канала 26 временных диаграмм. Команде Предварительная установка формирователей должна, обязательно, предшествовать команда Установка 0 формирователей.

Работа устройства в режиме Контроль начинается командами Сброс и

Время окончания вр мы определяется сигна по цепи Конец цикла ющим счетчик 63 в нул 15 подготавливая блок 35 временных диаграмм к работы.

Импульсы канала вр поступают на вход про

герного регистра 60 и фиксируется в нем синхронизирующими импульсами, поступающими на синхровход триггеоного регистра 68 через элемент НЕ 69. На выходе триггерного регистра 68 наблюдается изменение потенциалов в сигнальных цепях канала 26 временных диаграмм, начиная от потенциалов предварительной установки.

Время окончания временной диаграммы определяется сигналом, поступающим по цепи Конец цикла 37, устанавливающим счетчик 63 в нулевое состояние, подготавливая блок 35 формирования временных диаграмм к очередному циклу работы.

Импульсы канала временных диаграмм поступают на вход проверяемого изде

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Имитатор канала | 1987 |

|

SU1425675A2 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Имитатор канала | 1987 |

|

SU1467555A1 |

| Имитатор канала | 1983 |

|

SU1174927A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287236A1 |

| Автоматизированная система контроля | 1989 |

|

SU1695269A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано при изготовлении и испытании блоков памяти. Целью изобретения является расширение области применения устройства за счет увеличения парка проверяемых блоков памяти. Устройство для тестового контроля блоков памяти содержит генератор, блок управления, счетчик адреса буферных накопителей, дешифратор, буферный накопитель, регистр, формирователь результатов контроля, коммутатор. Введение в устройство блока формирования временных диаграмм позволяет производить проверку блоков памяти, требующих для работы различные временные диаграммы. 3 ил.

Пуск. Команда Сброс устанавливает 20 лия и обеспечивают его функциониро- счетчик 4 адреса буферных накопителей в нулевое состояние. По команде Пуск на выходе дешифратора 14 возбуждается цепь команды Пуск 7 и этот отрицательный импульс поступает 25 в формирователь 28 результата контроля и блок 2 управления.

В блоке 2 управления сигнал Пуск через элемент И 49 устанавливает триг30

40

rep 44 в единичное состояние, что обеспечивает работу сдвигающего per гистра 43. На выходе элемента И-НЕ 56 формируется сигнал, который по цепи Прием в буферный регистр 10 поступает на вход регистра 21 и содержимое буферного накопителя 16 по нулевому адресу, установленному в счетчике 4 адреса буферных .накопителей, переписывается в регистр 21. В режиме Контроль в блоке 2 управления триггером 4 и элементом И 52 в цепи Запись в буфер 11 устанавливается высокий уровень, а в цепи Выборка буфера 12 - низкий уровень, которые обеспечивают режим чтения буферного накопителя 16. 45

Кроме того,блок 2 управления вырабатывает по цепи синхронизирующих импульсов и цепи Конец цикла 37 сигналы, которые поступают на входы блока 35 формирования временных диаграмм.зд Синхронизирующие импульсы через элемент И 72 поступают на счетный вход счетчика 63. С перебором адресов последовательно считывается содержимое блока 64 запоминающих элементов, так gg как в цепи Запись в формирователи 42 отсутствует сигнал записи. Содержимое блока 64 запоминающих элементов поступает на информационный вход тригвание. Дальнейшая работа устройства тестового контроля памяти и работа нерассмотренных узлов описана в известном устройстве.

По останову блока управления, про исходящему при поступлении сигнала по одной из цепей Переполнение 32, признака Конец теста 22 и сигнала Неисправность 9, подача синхронизи

рующих импульсов на блок 35 формирования временных диаграмм прекращается. Сигналы цепей канала 26 временных диаграмм по содержанию могут изменяться программно. Конкретное зна- 35 чение номера контакта Qk, Qm, Qc, Qf Qn регистра 43 определяется характеристиками контролируемого блока (цикл обращения, время выборки и т.д.) и частоты генератора 1 (20 мГц

Таким образом, введение блока фор мирования временных диаграмм позволя ет расширить парк проверяемых устрой ством блоков памяти, а также операти но изменить временную диаграмму проверяемых блоков памяти с целью отработки и проверки схемотехнических ре шений в процессе проектирования блоков памяти.

Формула изобретения

Устройство для тестового контроля блоков памяти по авт.св. К 1365134, отличающееся тем, что, с целью расширения области применения устройства за счет увеличения парка проверяемых блоков памяти, в устройство введен блок формирования временлия и обеспечивают его функциониро-

вание. Дальнейшая работа устройства тестового контроля памяти и работа нерассмотренных узлов описана в известном устройстве.

По останову блока управления, происходящему при поступлении сигнала по одной из цепей Переполнение 32, признака Конец теста 22 и сигнала Неисправность 9, подача синхронизи

рующих импульсов на блок 35 формирования временных диаграмм прекращается. Сигналы цепей канала 26 временных диаграмм по содержанию могут изменяться программно. Конкретное зна- чение номера контакта Qk, Qm, Qc, Qf, Qn регистра 43 определяется характеристиками контролируемого блока (цикл обращения, время выборки и т.д.) и частоты генератора 1 (20 мГц)

0

5

g

Таким образом, введение блока формирования временных диаграмм позволяет расширить парк проверяемых устройством блоков памяти, а также оперативно изменить временную диаграмму проверяемых блоков памяти с целью отработки и проверки схемотехнических решений в процессе проектирования блоков памяти.

Формула изобретения.

Устройство для тестового контроля блоков памяти по авт.св. К 1365134, отличающееся тем, что, с целью расширения области применения устройства за счет увеличения парка проверяемых блоков памяти, в устройство введен блок формирования времен ,

ных диаграмм, вход синхронизации которого соединен с одноименным выходом блока управления, выход Конец цикла которого соединен с одноименным входом блока формирования временных диаграмм, информационные входы которого соединены с информационными входами буферного накопителя, счетный вход, вход Прием в регистр предва38

Н

W

V

М

t

w

«,

18

11 Л

11

17

1$

IL-.

f fo

E

23 21

fueJ

рительной установки, входы предварительной установки, установки в 0м и записи в формирователь блока формирования временных диаграмм соединены соответственно с одноименными выходами дешифратора, выходы задания режима работы блока формирования временных диаграмм являются одноименными выходами устройства.

3L

35

26

36

ж 37

25

13

#

,27

28

30

29

31

33

&

Фиг. 2

Риг.З

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-02-07—Публикация

1988-04-19—Подача