05

ел

со

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано при изготовлении и испы тании блоков памяти.

Целью изобретения является повьше ние достоверности контроля.

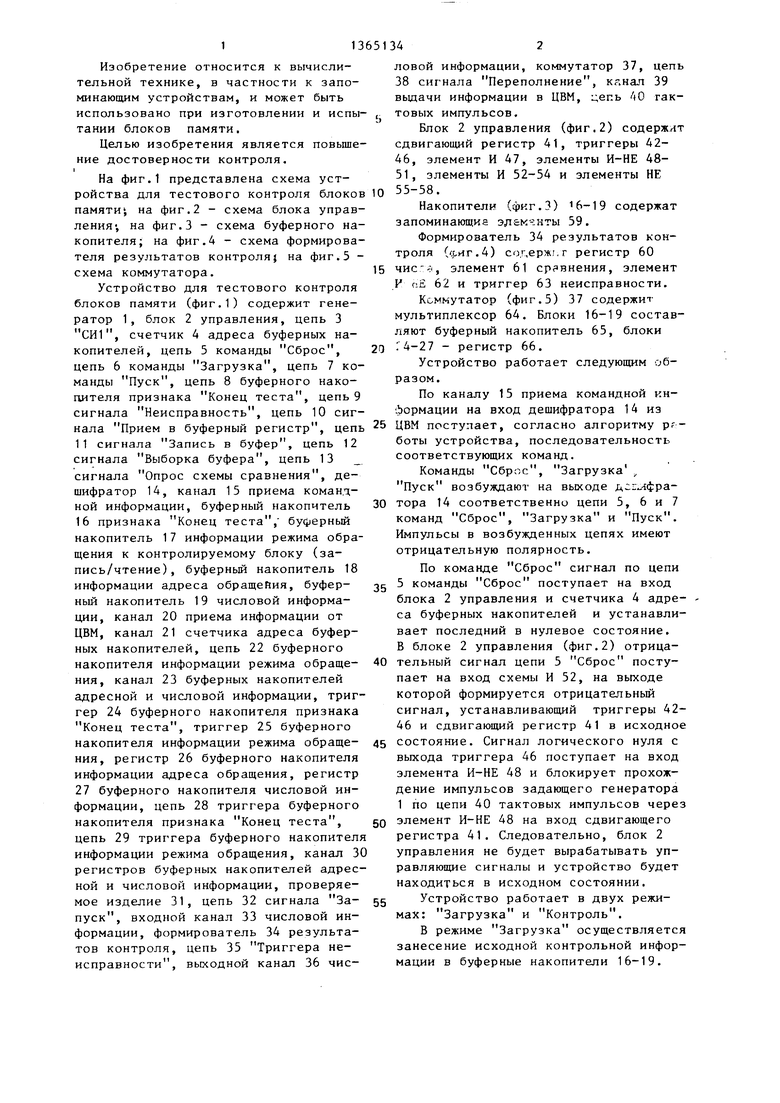

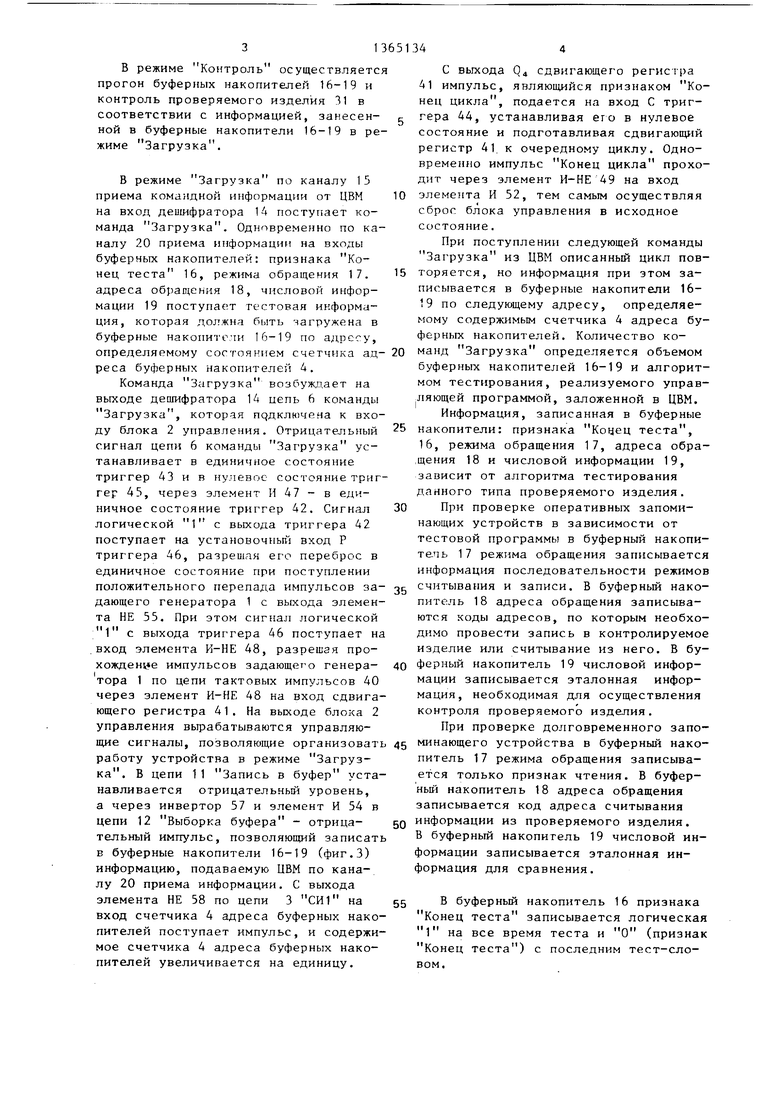

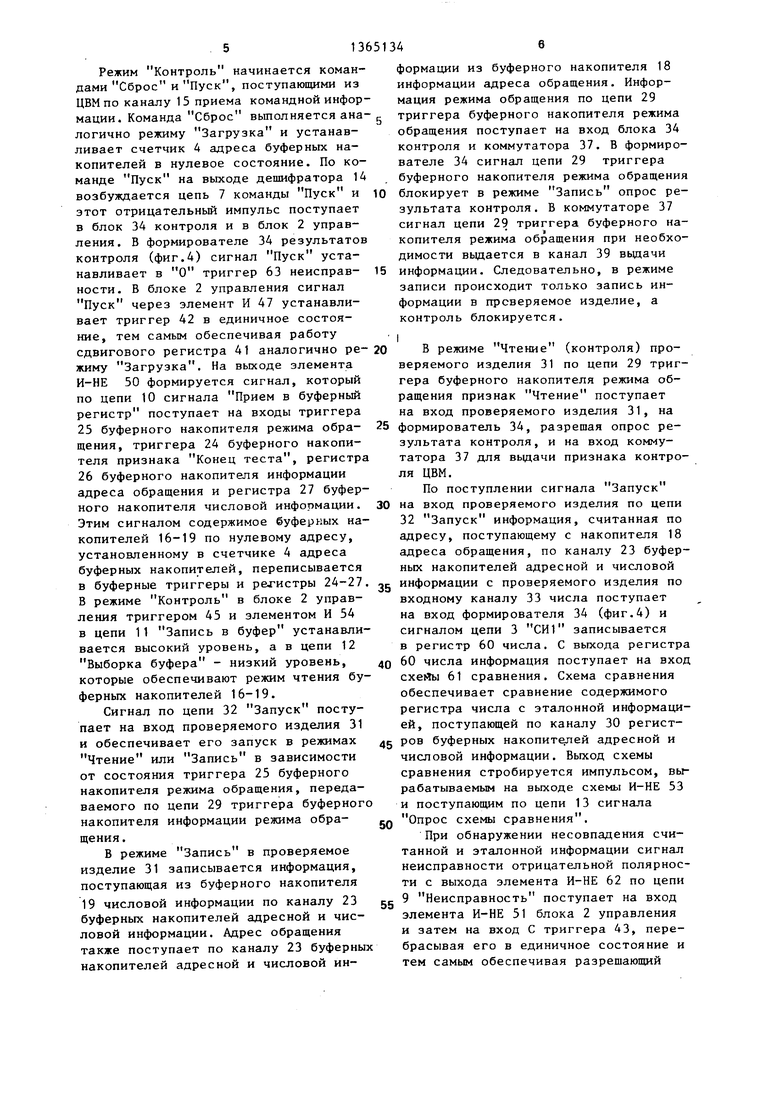

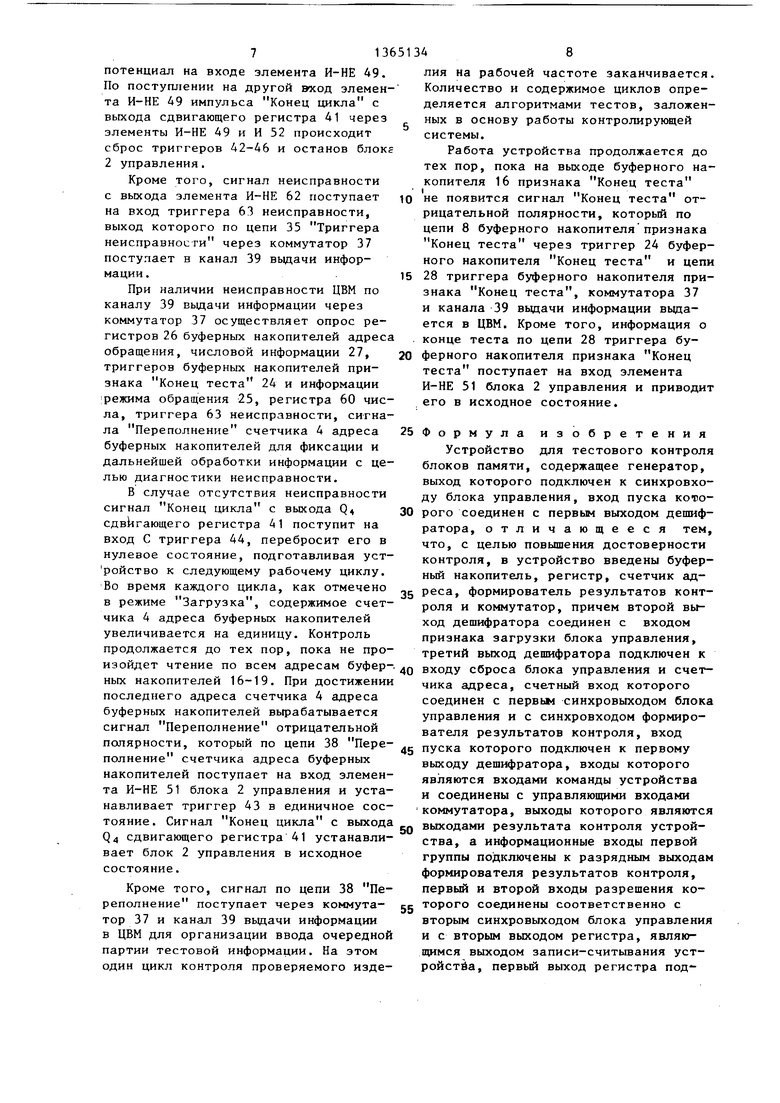

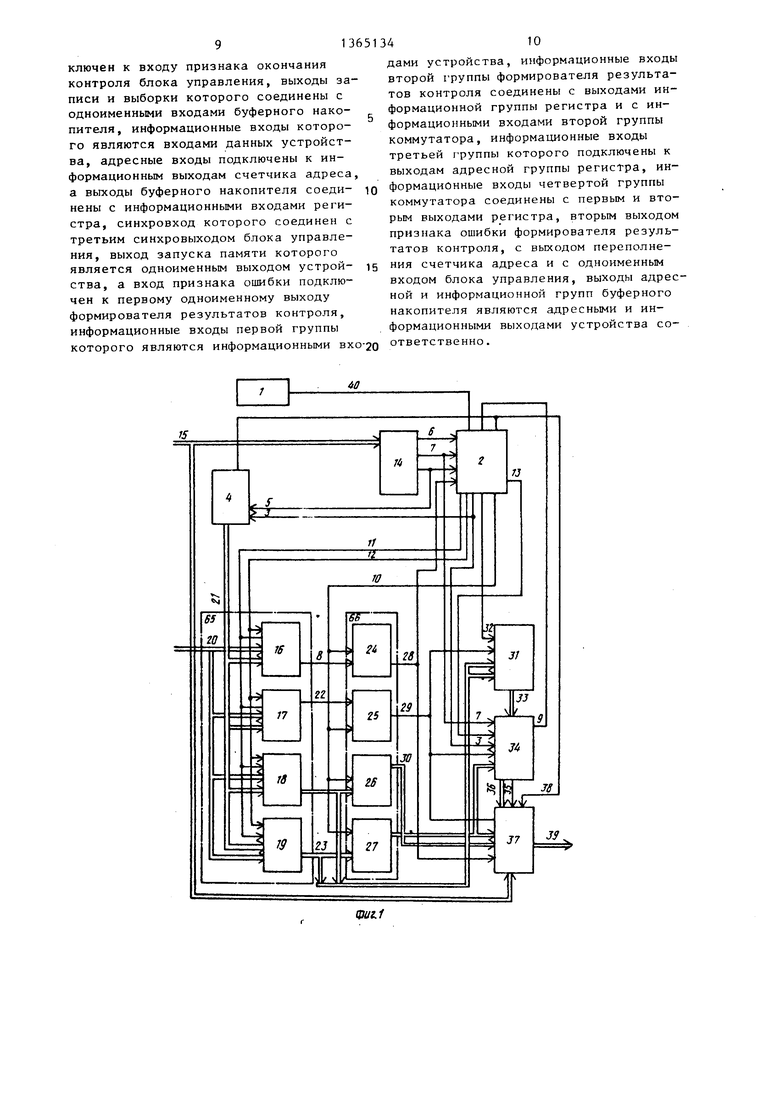

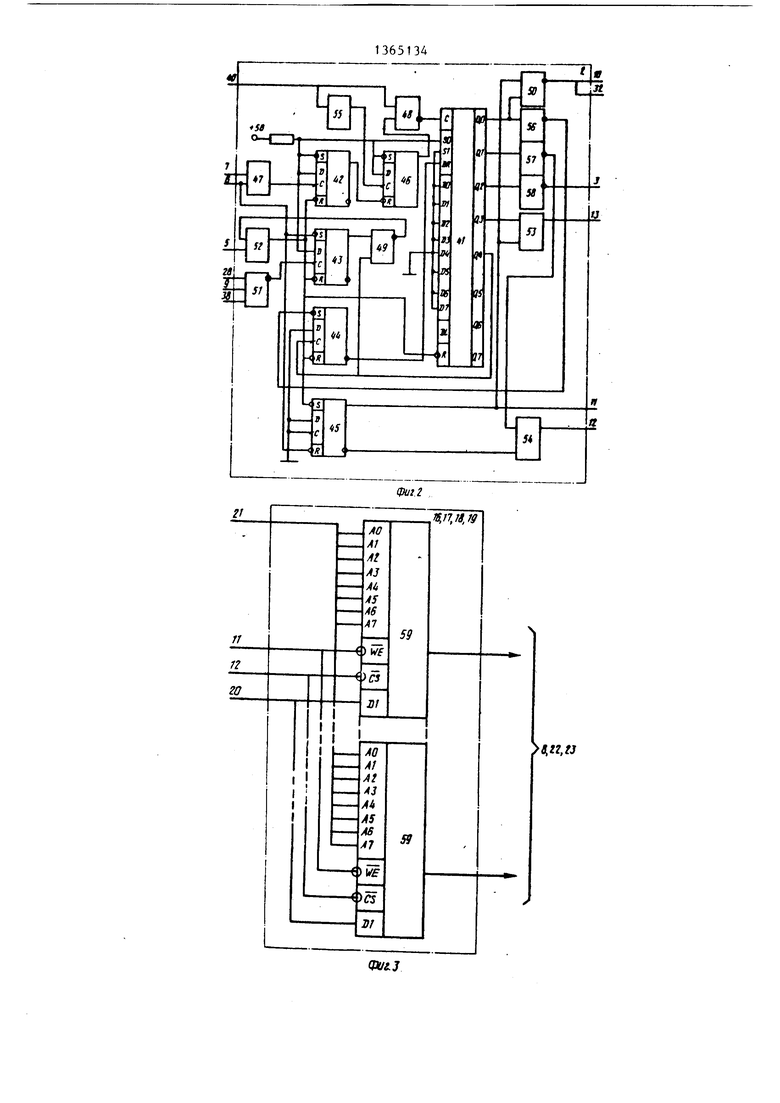

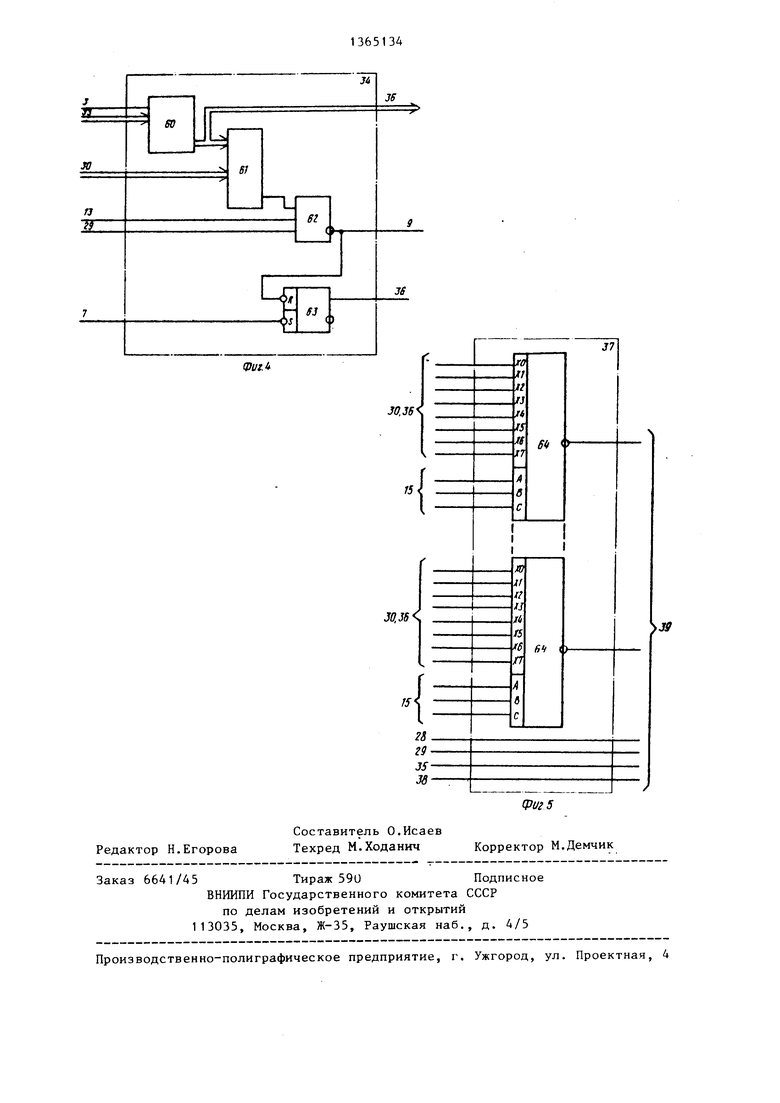

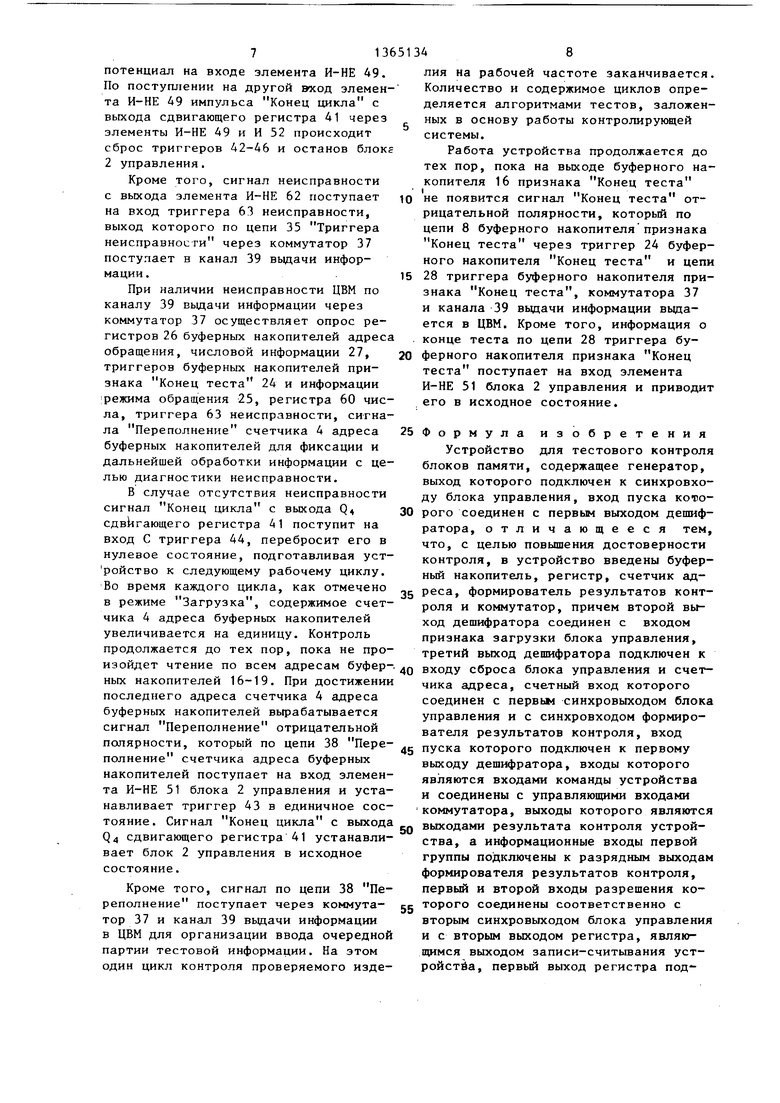

На фиг.1 представлена схема устройства для тестового контроля блоков памяти , на фиг. 2 - схема блока управления-, на фиг.З - схема буферного накопителя; на фиг,4 - схема формирователя результатов контроля} на фиг.З - схема коммутатора.

Устройство для тестового контроля блоков памяти (фиг.1) содержит генератор 1, блок 2 управления, цепь 3 СИ1, счетчик 4 адреса буферных накопителей, цепь 5 команды Сброс, цепь 6 команды Загрузка, цепь 7 команды Пуск, цепь 8 буферного нако- гштеля признака Конец теста, цепь 9 сигнала Неисправность, цепь 10 сигнала Прием в буферный регистр, цепь 11 сигнала Запись в буфер, цепь 12 сигнала Выборка буфера, цепь 13 сигнала Опрос схемы сравнения, дешифратор 14, канал 15 приема командной информации, буферный накопитель 16 признака Конец теста, буферный накопитель 17 информации режима обращения к контролируемому блоку (запись/чтение), буферньш накопитель 18 информации адреса обращейия, буфер- ный накопитель 19 числовой информации, канал 20 приема информации от ЦВМ, канал 21 счетчика адреса буферных накопителей, цепь 22 буферного накопителя информации режима обраще- ния, канал 23 буферных накопителей адресной и числовой информации, триггер 24 буферного накопителя признака Конец теста, триггер 25 буферного накопителя информации режима обраще- ния, регистр 26 буферного накопителя информации адреса обращения, регистр 27 буферного накопителя числовой информации, цепь 28 триггера буферного накопителя признака Конец теста, цепь 29 триггера буферного накопителя информации режима обращения, канал 30 регистров буферных накопителей адресной и числовой информации, проверяемое изделие 31, цепь 32 сигнала За- пуск, входной канал 33 числовой информации, формирователь 34 результатов контроля, цепь 35 Триггера неисправности, выходной канал 36 числовой информации, коммутатор 37, цепь 38 сигнала Переполнение, канал 39 вьщачи информации в ЦВМ, :;епь 40 тактовых импульсов.

Блок 2 управления (фиг.2) содержит сдвигающий регистр 41, триггеры 42- 46, элемент И 47, элементы И-НЕ 48- 51, элементы И 52-54 и элементы НЕ 55-58.

Накопители (фиг.З) 6-19 содержат запоминающие эл - -Нты 59.

Формирователь 34 результатов контроля (.4) сог,ерж1.г регистр 60 чис--, элемент 61 сравнения, элемент И па 62 и триггер 63 неисправности.

Коммутатор (фиг.5) 37 содержит мультиплексор 64. Блоки 16-19 составляют буферный накопитель 65, блоки Г 4-27 - регистр 66.

Устройство работает следующим образом.

По каналу 15 приема командной информации на вход дешифратора 14 из ЦВМ поступает, согласно алгоритму работы устройства, последовательность соответствующих команд.

Команды Сброс, Загрузка ,, Пуск возбуждают на выходе дгг.,-{фра- тора 14 соответственно цепи 5, 6 и 7 команд Сброс, Загрузка и Пуск. Импульсы в возбужденных цепях имеют отрицательную полярность.

По команде Сброс сигнал по цепи 5 команды Сброс поступает на вход блока 2 управления и счетчика 4 адреса буферных накопителей и устанавливает последний в нулевое состояние. В блоке 2 управления (фиг.2) отрицательный сигнал цепи 5 Сброс поступает на вход схемы И 52, на выходе которой формируется отрицательный сигнал, устанавливаюпщй триггеры 42- 46 и сдвигающий регистр 41 в исходное состояние. Сигнал логического нуля с выхода триггера 46 поступает на вход элемента И-НЕ 48 и блокирует прохождение импульсов задающего генератора 1 по цепи 40 тактовых импульсов через элемент И-НЕ 48 на вход сдвигающего регистра 41. Следовательно, блок 2 управления не будет вырабатывать управляющие сигналы и устройство будет находиться в исходном состоянии.

Устройство работает в двух режимах: Загрузка и Контроль.

В режиме Загрузка осуществляется занесение исходной контрольной информации в буферные накопители 16-19.

В режиме Контроль осуществляется прогон буферных накопителей 16-19 и контроль проверяемого изделия 31 в соответствии с информацией, занесен- ной в буферные накопители 16-19 в режиме Загрузка,

В режиме Загрузка по каналу 15 приема кома}|дной информации от ЦВМ на вход деишфратора 14 поступает команда Загрузка. Одновременно по каналу 20 приема информации на входы буферных накопителей: признака Конец теста 16, режима обращения 17. адреса обрап;ения 18, числовой информации 19 поступает тестовая информация, которая должна быть загружена в буферные накопители 16-19 по адресу, определяемому состоянием счетчика ад- реса буферных накопителей 4.

Команда Загрузка возбужрдет на выходе дешифратора 14 цепь 6 команды Загрузка, которая П9дклн)чеяа к входу блока 2 управления. Отрицательный сигнал цепи 6 команды Загрузка устанавливает в единичное состояние триггер 43 и в нулевое состояние триггер 45, через элемент И 47 - в единичное состояние триггер 42. Сигнал логической 1 с выхода триггера 42 поступает на установочный вход Р триггера 46, разрешая его переброс в единичное состояние при поступлении положительного перепада импульсов за- дающего генератора 1 с выхода элемента НЕ 55. При этом сигнал логической 1 с выхода триггера 46 поступает на вход элемента И-НЕ 48, разрешая прохождение импульсов задающего генера- тора 1 по цепи тактовых импульсов 40 через элемент И-НЕ 48 на вход сдвигающего регистра 41. На выходе блока 2 управления вырабатываются управляю- щие сигналы, позволяющие организоват работу устройства в режиме Загрузка. В цепи 11 Запись в буфер устанавливается отрицательньй уровень, а через инвертор 57 и элемент И 54 в цепи 12 Выборка буфера - отрица- тельный импульс, позволяющий записат в буферные накопители 16-19 (фиг.З) информацию, подаваемую ЦВМ по каналу 20 приема информации. С выхода элемента НЕ 58 по цепи 3 СИ1 на вход счетчика 4 адреса буферных накопителей поступает импульс, и содержимое счетчика 4 адреса буферных накопителей увеличивается на единицу.

С выхода р4 сдвигающего регистра 41 импульс, являющийся признаком Конец цикла, подается на вход С триггера 44, устанавливая его в нулевое состояние и подготавливая сдвигающий регистр 41 к очередному циклу. Одновременно импульс Конец цикла проходит через элемент И-НЕ 49 на вход элемента И 52, тем самым осуществляя сброс блока управления в исходное состояние.

При поступлении следующей команды Загрузка из ЦВМ описанный цикл повторяется, но информация при этом записывается в буферные накопители 16- 19 по следующему адресу, определяемому содержимым счетчика 4 адреса буферных накопителей. Количество команд Загрузка определяется объемом буферных накопителей 16-19 и алгоритмом тестирования, реализуемого управ- |Ляющей программой, заложенной в ЦВМ.

Информация, записанная в буферные накопители: признака Коцец теста, 16, режима обращения 17, адреса обращения 18 и числовой информации 19, зависит от алгоритма тестирования данного типа проверяемого изделия.

При проверке оперативных запоминающих устройств в зависимости от тестовой программы в буферный накопи- тет7ь 17 режима обращения записывается информация последовательности режимов считывания и записи. В буферный накопитель 18 адреса обращения записываются коды адресов, по которым необходимо провести запись в контролируемое изделие или считывание из него. В буферный накопитель 19 числовой информации записывается эталонная информация, необходимая для осуществления контроля проверяемого изделия.

При проверке долговременного запоминающего устройства в буферный накопитель 17 режима обращения записывается только признак чтения. В буферный накопитель 18 адреса обращения записывается код адреса считывания информации из проверяемого изделия. В буферный накопитель 19 числовой информации записывается эталонная информация для сравнения.

В буферный накопитель 16 признака Конец теста записывается логическая 1 на все время теста и О (признак Конец теста) с последним тест-словом.

Режим Контроль начинается командами Сброс и Пуск, поступающими из ЦВМ по каналу 15 приема командной информации. Команда Сброс вьшолняется ана логично режиму Загрузка и устанавливает счетчик 4 адреса буферных накопителей в нулевое состояние. По команде Пуск на выходе дешифратора 14 возбуждается цепь 7 команды Пуск и этот отрицательный импульс поступает в блок 34 контроля и в блок 2 управления. В формирователе 34 результатов контроля (фиг.4) сигнал Пуск устанавливает в О триггер 63 неисправ- ности. В блоке 2 управления сигнал Пуск через элемент И 47 устанавливает триггер 42 в единичное состояние, тем самым обеспечивая работу сдвигового регистра 41 аналогично ре- жиму Загрузка. На выходе элемента И-НЕ 50 формируется сигнал, который по цепи 10 сигнала Прием в буферный регистр поступает на входы триггера

25буферного накопителя режима обра- щения, триггера 24 буферного накопителя признака Конец теста, регистра

26буферного накопителя информации адреса обращения и регистра 27 буферного накопителя числовой информации. Этим сигналом содержимое буферных накопителей 16-19 по нулевому адресу, установленному в счетчике 4 адреса буферных накопителей, переписывается

в буферные триггеры и peJ иcтpы 24-27. В режиме Контроль в блоке 2 управления триггером 45 и элементом И 54 в цепи 11 Запись в буфер устанавливается высокий уровень, а в цепи 12 Выборка буфера - низкий уровень, которые обеспечивают режим чтения буферных накопителей 16-19.

Сигнал по цепи 32 Запуск поступает на вход проверяемого изделия 31 и обеспечивает его запуск в режимах Чтение или Запись в зависимости от состояния триггера 25 буферного накопителя режима обращения, передаваемого по цепи 29 триггера буферного накопителя информации режима обра- щения.

В режиме Запись в проверяемое изделие 31 записывается информация, поступающая из буферного накопителя

19 числовой информации по каналу 23 буферных накопителей адресной и числовой информации. Адрес обращения также поступает по каналу 23 буферных накопителей адресной и числовой информации из буферного накопителя 18 информации адреса обращения. Информация режима обращения по цепи 29 триггера буферного накопителя режима обращения поступает на вход блока 34 контроля и коммутатора 37. В формирователе 34 сигнал цепи 29 триггера буферного накопителя режима обращени блокирует в режиме Запись опрос результата контроля. В коммутаторе 37 сигнал цепи 29 триггера буферного накопителя режима обращения при необходимости выдается в канал 39 вьщачи информации. Следовательно, в режиме записи происходит только запись информации в проверяемое изделие, а контроль блокируется.

I

В режиме Чтение (контроля) проверяемого изделия 31 по цепи 29 триггера буферного накопителя режима обращения признак Чтение поступает на вход проверяемого изделия 31, на формирователь 34, разрешая опрос результата контроля, и на вход коммутатора 37 для выдачи признака контроля ЦВМ.

По поступлении сигнала Запуск на вход проверяемого изделия по цепи 32 Запуск информация, считанная по адресу, поступающему с накопителя 18 адреса обращения, по каналу 23 буферных накопителей адресной и числовой информации с проверяемого изделия по входному каналу 33 числа поступает на вход формирователя 34 (фиг.4) и сигналом цепи 3 СИГ записывается в регистр 60 числа. С выхода регистра 60 числа информация поступает на вход схейы 61 сравнения. Схема сравнения обеспечивает сравнение содержимого регистра числа с эталонной информацией, поступающей по каналу 30 регистров буферных накопителей адресной и числовой информации. Выход схемы сравнения стробируется импульсом, вы рабатываемым на выходе схемы И-НЕ 53 и поступающим по цепи 13 сигнала Опрос схемы сравнения.

При обнаружении несовпадения считанной и эталонной информации сигнал неисправности отрицательной полярности с выхода элемента И-НЕ 62 по цепи 9 Неисправность поступает на вход элемента И-НЕ 51 блока 2 управления и затем на вход С триггера 43, перебрасывая его в единичное состояние и тем самым обеспечивая разрешающий

потенциал на входе элемента И-НЕ 49. По поступлении на другой вкод элемента И-НЕ 49 импульса Конец цикла с выхода сдвигающего регистра 41 череэ элементы И-НЕ 49 и И 52 происходит сброс триггеров 42-46 и останов блоке 2 управления.

Кроме того, сигнал неисправности с вьосода элемента И-НЕ 62 поступает на вход триггера 63 неисправности, выход которого по цепи 35 Триггера неисправности через коммутатор 37 поступает н канал 39 вьщачи информации .

При наличии неисправности ЦВМ по каналу 39 выдачи информации через коммутатор 37 осуществляет опрос регистров 26 буферных накопителей адреса обращения, числовой информации 27, триггеров буферных накопителей признака Конец теста 24 и информации :режима обращения 25, регистра 60 чис

51348

ЛИЯ на рабочей частоте заканчивается. Количество и содержимое циклов определяется алгоритмами тестов, заложенных в основу работы контролирующей системы.

Работа устройства продолжается до тех пор, пока на выходе буферного накопителя 16 признака Конец теста

10 не появится сигнал Конец теста отрицательной полярности, который по цепи 8 буферного накопителя признака Конец теста через триггер 24 буферного накопителя Конец теста и цепи

15 28 триггера буферного накопителя признака Конец теста, коммутатора 37 и канала 39 вьодачи информации вьща- ется в ЦВМ. Кроме того, информация о . конце теста по цепи 28 триггера бу20 ферного накопителя признака Конец теста поступает на вход элемента И-НЕ 51 блока 2 управления и приводит его в исходное состояние.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля блоков памяти | 1988 |

|

SU1541678A1 |

| Устройство для контроля оперативных запоминающих блоков | 1980 |

|

SU890442A1 |

| Устройство для контроля блоков постоянной памяти | 1982 |

|

SU1049984A1 |

| Графический дисплей с контролем | 1984 |

|

SU1249526A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Устройство для сопряжения | 1980 |

|

SU962906A2 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано при изготовлении и испытании блоков памяти. Целью изобретения является повьшение достоверности , контроля. Устройство содержит генератор, блок управления, счетчик адреса, дешифратор, буферные накопители, регистр, коммутатор и формирователь результатов контроля.. Перед началом - контроля по командам от ЦВМ производится загрузка буферного накопителя информационной, адресной и управляющей (запись/считывание, признак окончания теста) последовательностями, образующими тест. Далее устройство переходит в режим выдачи теста на контролируемый блок памяти путем последовательного считывания буферного накопителя. Считываемая информация контролируется формирователем результатов контроля. 5 ил. с $ (Л

ла, триггера 63 неисправности, сигнала Переполнение счетчика 4 адреса буферных накопителей для фиксации и дальнейшей обработки информации с целью диагностики неисправности.

В случае отсутствия неисправности сигнал Конец 1Д1кла с выхода р4 сдвигающего регистра 41 поступит на вход С триггера 44, перебросит его в нулевое состояние, подготавливая уст- ройство к следующему рабочему циклу. Во время каждого цикла, как отмечено в режиме Загрузка, содержимое счетчика 4 адреса буферных накопителей увеличивается на единицу. Контроль продолжается до тех пор, пока не произойдет чтение по всем адресам буферных накопителей 16-19. При достижении последнего адреса счетчика 4 адреса буферных накопителей вырабатывается сигнал Переполнение отрицательной полярности, который по цепи 38 Пере

полнение счетчика адреса буферных накопителей поступает на вход элемента И-НЕ 51 блока 2 управления и устанавливает триггер 43 в единичное состояние. Сигнал Конец цикла с выхода Q4 сдвигающего регистра 41 устанавливает блок 2 управления в исходное состояние.

Кроме того, сигнал по цепи 38 Переполнение поступает через коммутатор 37 и канал 39 выдачи информации в ЦВМ для организации ввода очередной партии тестовой информации. На этом один цикл контроля проверяемого изде30

Q

25 Формула изобретения

Устройство для тестового контроля блоков памяти, содержащее генератор, выход которого подключен к синхровхо- ду блока управления, вход пуска которого соединен с первым выходом дещиф- ратора, отличающееся тем.

контроля, в устройство введены буферный накопитель, регистр, счетчик ад- реса, формирователь результатов контроля и коммутатор, причем второй выход дешифратора соединен с входом признака загрузки блока управления, третий выход дешифратора подключен к входу сброса блока управления и счетчика адреса, счетный вход которого соединен с первьм синхровыходом блока управления и с синхровходом формирователя результатов контроля, вход пуска которого подключен к первому выходу дешифратора, входы которого являются входами команды устройства и соединены с управляю1цими входами коммутатора, выходы которого являются выходами результата контроля устройства, а информационные входы первой группы подключены к разрядным выходам формирователя результатов контроля, первый и второй входы разрешения которого соединены соответственно с

вторым синхровыходом блока управления и с вторым выходом регистра, являющимся выходом записи-считьшания уст- ройстйа, первый выход регистра подключей к входу признака окончания контроля блока управления, выходы записи и выборки которого соединены с одноименными входами буферного накопителя, информационные входы которого являются входами данных устройства, адресные входы подключены к информационным выходам счетчика адреса а выходы буферного накопителя соеди- нены с информационными входами регистра, синхровход которого соединен с третьим синхровыходом блока управления, выход запуска памяти которого является одноименным выходом устрой- ства, а вход признака ошибки подключен к первому одноименному выходу формирователя результатов контроля, информационные входы первой группы которого являются информационными вх

J5

дами устройства, информационные входы второй группы формирователя результатов контроля соединены с выходами информационной группы регистра и с информационными входами второй группы коммутатора, информационные входы третьей группы которого подключены к выходам адресной группы регистра, информационные входы четвертой группы коммутатора соединены с первым и вторым выходами регистра, вторым выходом признака ошибки формирователя результатов контроля, с выходом переполнения счетчика адреса и с одноименным входом блока управления, выходы адресной и информационной групп буферного накопителя являются адресными и информационными выходами устройства соответственно .

| Устройство для контроля полупроводниковой памяти | 1981 |

|

SU968856A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Полупроводниковый элемент памятидля пОСТОяННОгО зАпОМиНАющЕгО уСТРОйСТВА | 1979 |

|

SU824313A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-01-07—Публикация

1986-07-09—Подача