Изобретение относится к вычислительной технике и может быть исполы зовано в качестве буферного запоминающего устройства каналов и устройств обмена, а также систем .сбора и обработки информации. ,

Цель изобретения - повьшение надежности устройства.

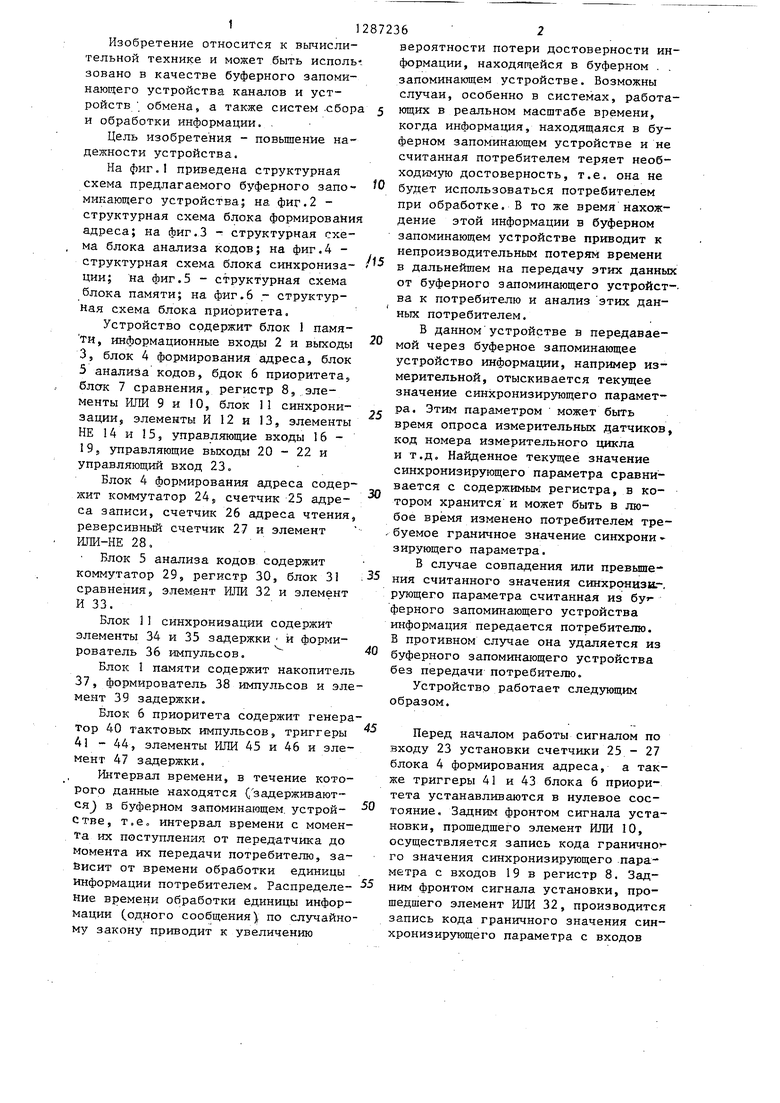

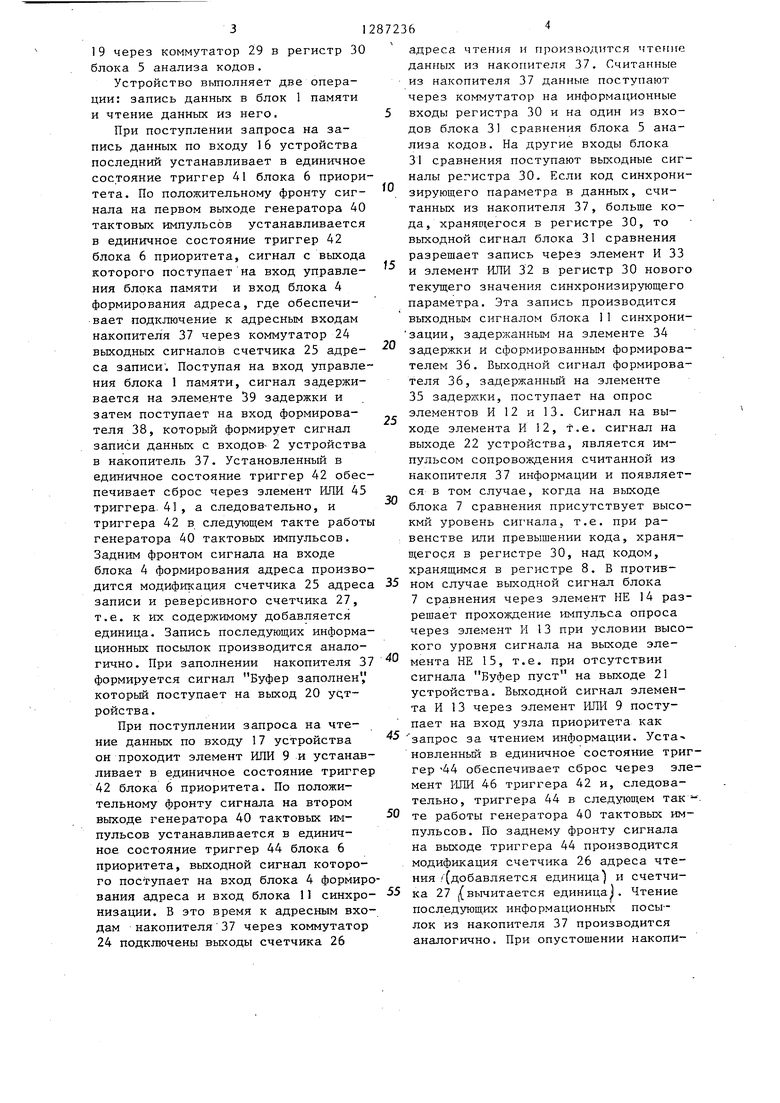

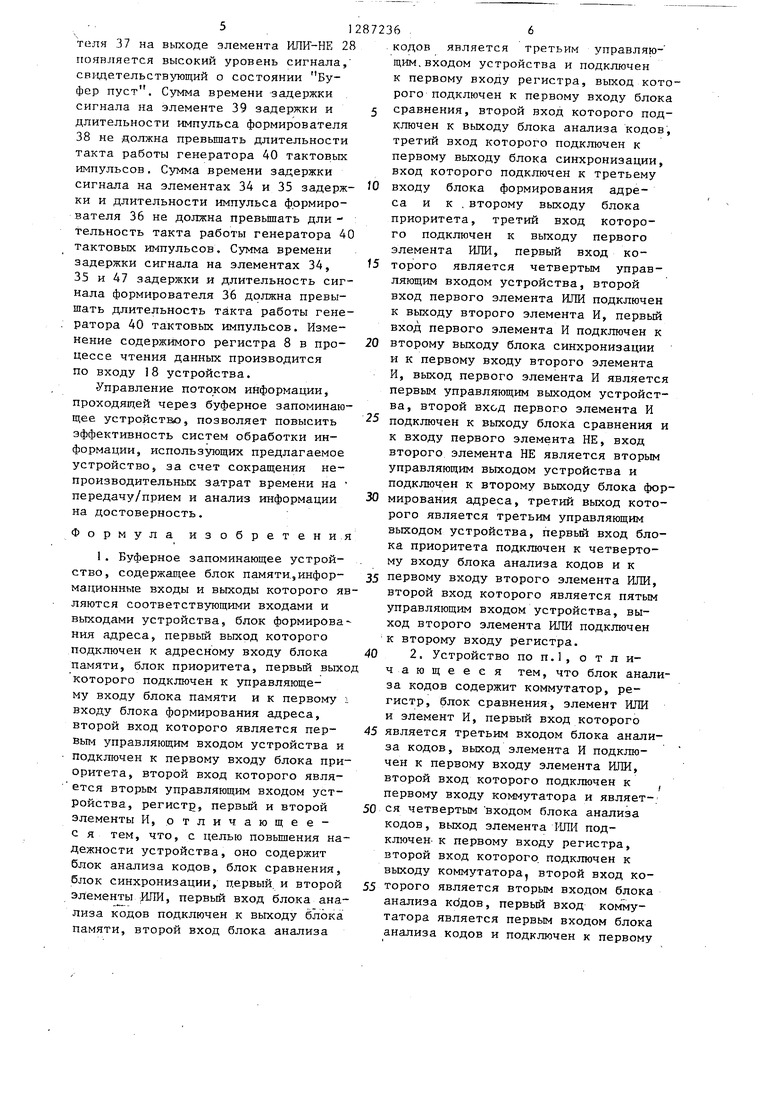

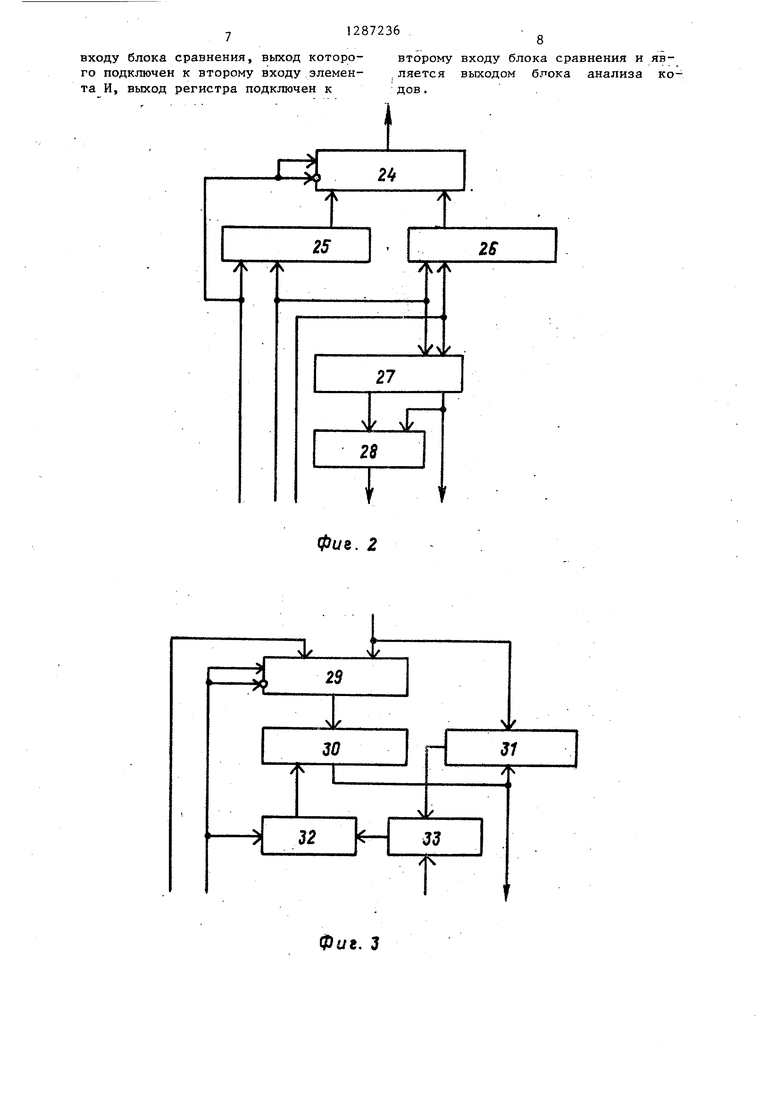

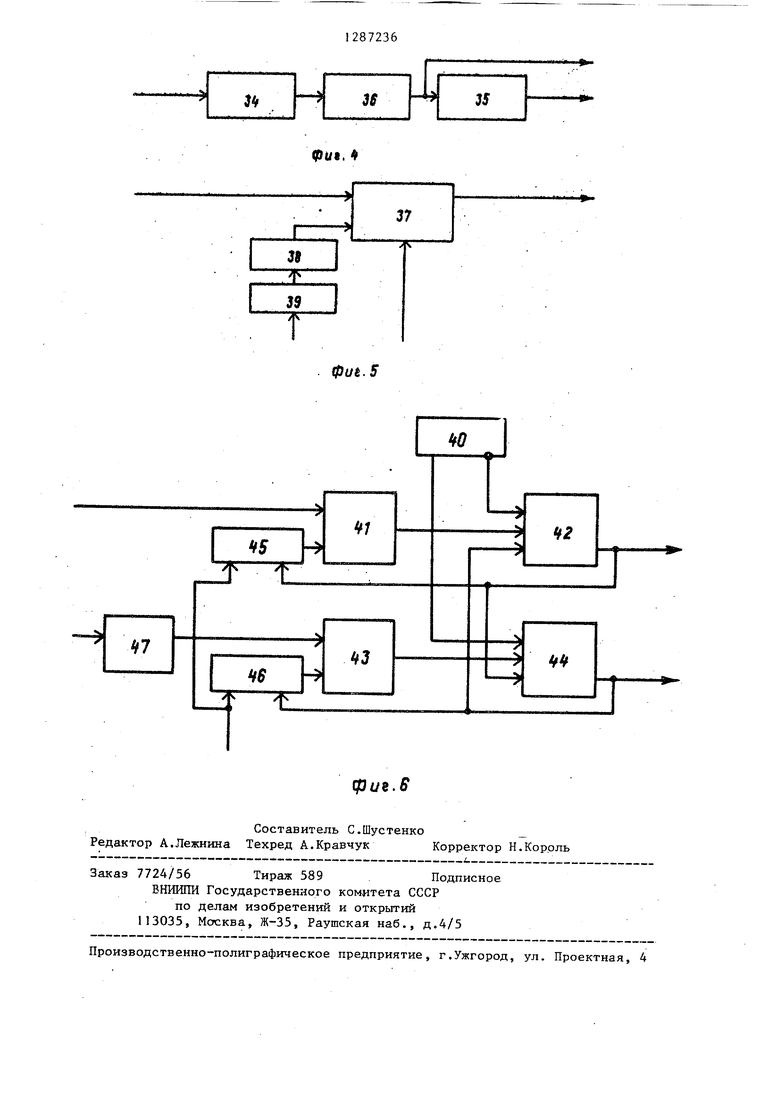

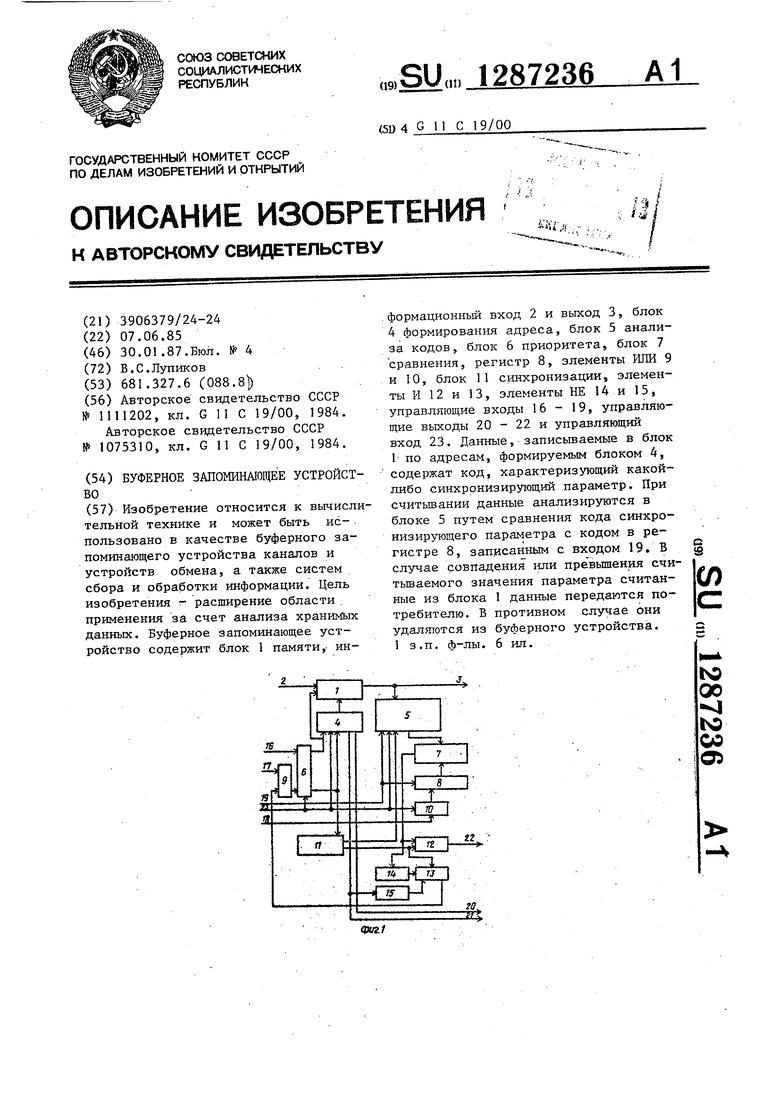

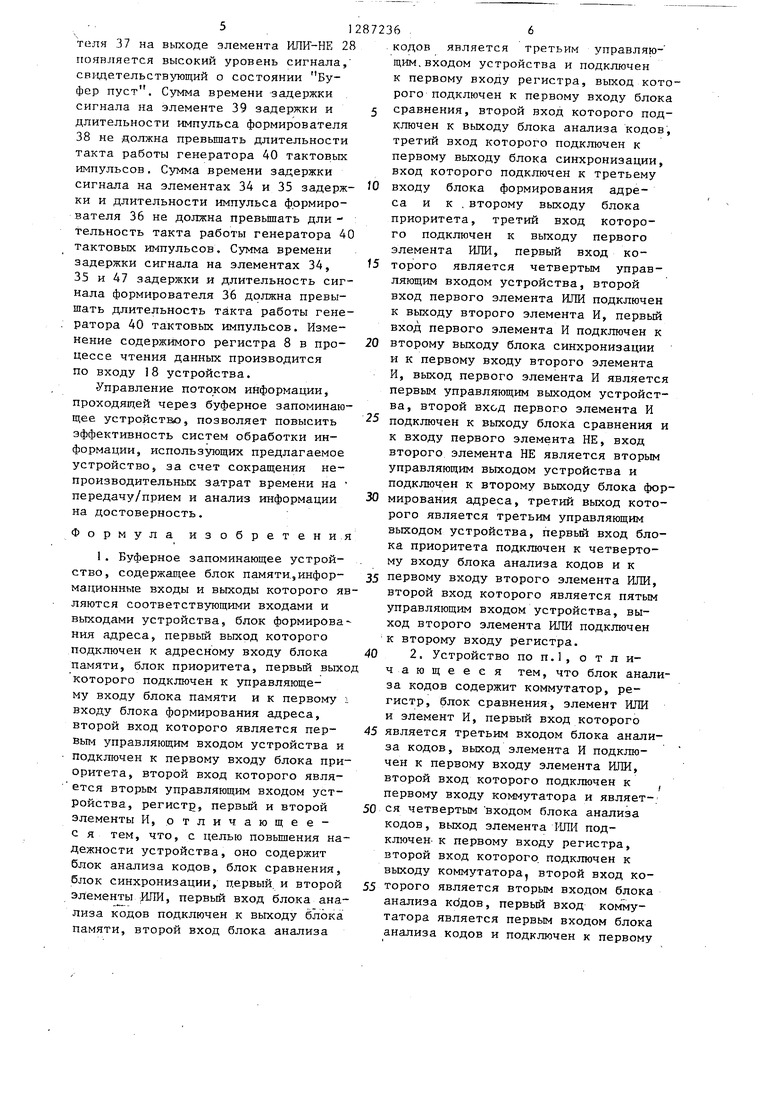

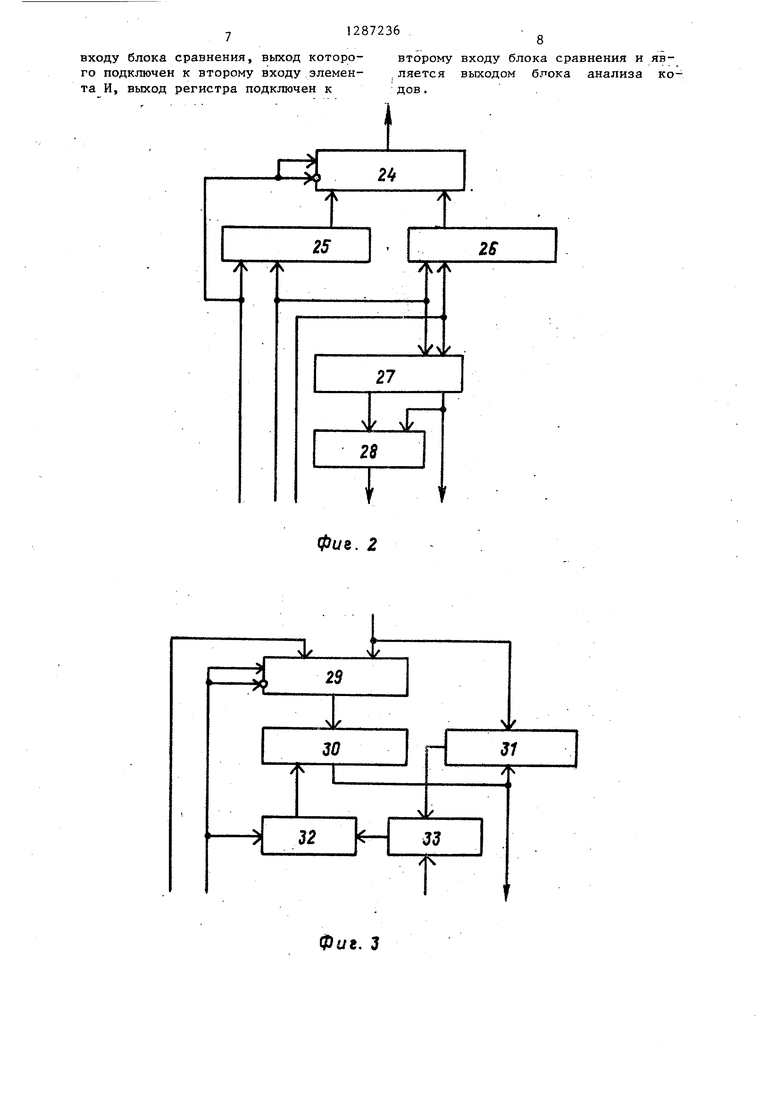

На фиг.1 приведена структурная схема предлагаемого буферного запоминающего устройства; на фиг.2 - структурная схема блока формирования адреса; на фиг.З - структурная схема блока анализа кодов; на фиг.4 - структурная схема блока синхронизации; на фиг.З - структурная схема блока памяти; на фиг.6 - структурная схема блока приоритета.

Устройство содержит блок 1 памя- ти, информационные входы 2 и выходы 3, блок 4 формирования адреса, блок 5 анализа кодов, бдок 6 приоритета блсгк 7 сравнения, регистр 8, элементы ИЛИ 9 и 10, блок 1 синхронизации, элементы И 12 и 13, элементы НЕ 14 и 15, управляющие входы 16 19, управляющие выходы 20 - 22 и управляющий вход 23

Блок 4 формирования адреса содержит коммутатор 24, счетчик 25 адреса записи, счетчик 26 адреса чтения, реверсивньгй счетчик 27 и элемент ИЛИ-НЕ 28 о

Блок 5 анализа кодов содержит коммутатор 29, регистр 30, блок 31 сравнения, элемент ИЛИ 32 и элемент И 33.

Блок 1 синхронизации содержит элементы 34 и 35 задержки и формирователь 36 импульсов.

Блок 1 памяти содержит накопитель 37, формирователь 38 импульсов и эле мент 39 задержки.

Блок 6 приоритета содержит генера Тор 40 тактовых импульсов, триггеры 41 - 44, элементы ИЛИ 45 и 46 и элемент 47 задержки.

Интервал времени, в течение которого данные находятся (задерживаются в буферном запоминающем, устройстве, т.е. интервал времени с момента их поступления от передатчика до Момента их передачи потребителю, за- бисит от времени обработки единицы Информации потребителем. Распределение времени обработки единицы информации (одного сообщения по случайно My закону приводит к увеличению

W

f5

0

5

30

35

0

5

0

5

вероятности потери достоверности информации, находящейся в буферном . . запоминающем устройстве. Возможны случаи, особенно в системах, работающих в реальном масштабе времени, когда информация, находящаяся в буферном запоминающем устройстве и не считанная потребителем теряет необходимую достоверность, т.е. она не будет использоваться потребителем при обработке. В то же время нахождение этой информации в буферном запоминающем устройстве приводит к непроизводительным потерям времени в дальнейшем на передачу этих данных от буферного запоминающего устройст-. ва к потребителю и анализ этих данных потребителем.

В данном устройстве в передаваемой через буферное запоминающее устройство информации, например измерительной, отыскивается текущее значение синхронизирующего параметра. Этим параметром может быть время опроса измерительных датчиков, код номера измерительного цикла и т.д. Найденное текущее значение синхронизирующего параметра сравнивается с содержимым регистра, в котором хранится и может быть в любое время изменено потребителем тре- , буемое граничное значение синхрони - зирующего параметра.

В случае совпадения или превышения считанного значения синхронизиг. рующего параметра считанная из буферного запоминающего устройства информация передается потребителю. В противном случае она удаляется из буферного запоминающего устройства без передачи потребителю.

Устройство работает следующим образом.

Перед началом работы сигналом по входу 23 установки счетчики 25 - 27 блока 4 формирования адреса, а также триггеры 41 и 43 блока 6 приоритета устанавливаются в нулевое состояние. Задним фронтом сигнала установки, прошедшего элемент ИЛИ 10, осуществляется запись кода граничног- го значения синхронизирующего .параметра с входов 19 в регистр 8. Задним фронтом сигнала установки, прошедшего элемент ИЛИ 32, производится запись кода граничного значения синхронизирующего параметра с входов

19 через коммутатор 29 в регистр 30 блока 5 анализа кодов.

Устройство вьшолняет две операции: запись данных в блок 1 памяти и чтение данных из него.

При поступлении запроса на запись данных по входу 16 устройства последний устанавливает в единичное состояние триггер 41 блока 6 приоритета. По положительному фронту сигнала на первом выходе генератора 40 тактовых импульсов устанавливается в единичное состояние триггер 42 блока 6 приоритета, сигнал с выхода которого поступает на вход управления блока памяти и вход блока 4 формирования адреса, где обеспечивает подключение к адресным входам накопителя 37 через коммутатор 24 выходных сигналов счетчика 25 адреса записи; Поступая на вход управления блока 1 памяти, сигнал задерживается на элементе 39 задержки и затем поступает на вход формирователя 38, который формирует сигнал записи данных с входов- 2 устройства в накопитель 37. Установленный в единичное состояние триггер 42 обеспечивает сброс через элемент ИЛИ 45 триггера. 41, а следовательно, и триггера 42 в следующем такте работы генератора 40 тактовых импульсов. Задним фронтом сигнала на входе блока 4 формирования адреса производится модификация счетчика 25 адреса записи и реверсивного счетчика 27, т.е. к их содержимому добавляется единица. Запись последующих информационных посылок производится аналогично. При заполнении накопителя 37 формируется сигнал Буфер заполнен , который поступает на выход 20 ус;т- ройства.

При поступлении запроса на чтение данных по входу 17 устройства он проходит элемент ИПИ 9 и устанавливает в единичное состояние триггер 42 блока 6 приоритета. По положительному фронту сигнала на втором выходе генератора 40 тактовых импульсов устанавливается в единичное состояние триггер 44 блока 6 приоритета, выходной сигнал которого поступает на вход блока 4 формирования адреса и вход блока 11 синхронизации. В это время к адресным входам накопителя 37 через коммутатор 24 подключены выходы счетчика 26

0

5

0

5

5

адреса чтения и производится чтение данных из накопителя 37. Считанные из накопителя 37 данные поступают через коммутатор на информационные входы регистра 30 и на один из входов блока 31 сравнения блока 5 анализа кодов. На другие входы блока 31 сравнения поступают выходные сигналы регистра 30. Если код синхронизирующего параметра в данных, считанных из накопителя 37, больше кода, храняп5егося в регистре 30, то выходной сигнал блока 31 сравнения разрешает запись через элемент И 33 и элемент ИЛИ 32 в регистр 30 нового текущего значения синхронизирующего параметра. Эта запись производится выходным сигналом блока I1 синхронизации, задержанным на элементе 34 задержки и сформированным формирователем 36. Выходной сигнал формирователя 36, задержанный на элементе 35 задержки, поступает на опрос элементов И 12 и 13. Сигнал на выходе элемента И 12, т.е. сигнал на выходе 22 устройства, является импульсом сопровождения считанной из накопителя 37 информации и появляется в том случае, когда на выходе блока 7 сравнения присутствует высо- кмй уровень сигнала, т.е. при равенстве или превышении кода, хранящегося в регистре 30, над кодом, хранящимся в регистре 8. В противном случае выходной сигнал блока 7 сравнения через элемент НЕ 14 разрешает прохождение импульса опроса через элемент И 13 при условии высокого уровня сигнала на выходе элемента НЕ 15, т.е. при отсутствии сигнала Буфер пуст на выходе 21 устройства. Выходной сигнал элемента И 1 3 через элемент ИЛИ 9 поступает на вход узла приоритета как запрос за чтением информации. Уста новленный в единичное состояние триггер 44 обеспечивает сброс через элемент 1-ШИ 46 триггера 42 и, следовательно, триггера 44 в следующем так, те работы генератора 40 тактовых импульсов. По заднему фронту сигнала на выходе триггера 44 производится модификация счетчика 26 адреса чтения . (добавляется единица) и счетчика 27 ((вычитается единица. Чтение последующих информационных посылок из накопителя 37 производится аналогично. При опустошении накопи0

0

0

5

теля 37 на выходе элемента ЖИТ-НЕ 28 появляется высокий уровень сигнала, св1-щетельствующий о состоянии Буфер пуст. Сумма времени задержки , сигнала на элементе 39 задер|жки и длительности импульса формирователя 38 не должна превышать длительности такта работы генератора 40 тактовых импульсов, Сумма времени задержки сигнала на элементах 34 и 35 задержки и длительности импульса формирователя 36 не должна превышать дли- тельность такта работы генератора 40 тактовых импульсов. Сумма времени задержки сигнала на элементах 34, 35 и 47 задержки и длительность сигнала формирователя 36 должна превышать длительность такта работы генератора 40 тактовых импульсов. Изменение содержимого регистра 8 в процессе чтения данных производится по входу 18 устройства.

Управление потоком информацииj проходящей через буферное запоминающее устройство, позволяет повысить эффективность систем обработки информации, использующих предлагаемое устройство, за счет сокращения непроизводительных затрат времени на передачу/прием и анализ информации на достоверность.

Формула и 1

е т е н и я

обр

Буферное запоминающее устрой- ство, содержащее блок памяти, информационные входы и выходы которого являются соответствующими входами и выходами устройства, блок формироваНИЛ адреса, первый выход которого подключен к адресному входу блока памяти, блок приоритета, первый выхо которого подключен к управляющему входу блока памяти и к первому i входу блока формирования адреса, второй вход которого является первым управляющим входом устройства и подктаочен к первому входу блока приоритета, второй вход которого является вторым управляющим входом устройства, регистр, первьй и второй Элементы И, ртличающее- с я тем, что, с целью повышения надежности устройства, оно содержит блок анализа кодов, блок сравнения, блок синхронизации, первый, и второй элементы ИЛИ, первый вход блока анализа кодов подключен к выходу блока памяти, второй вход блока анализа

0

5

.кодов является третьим управляющим, входом устройства и подключен к первому входу регистра, выход которого подключен к первому входу блока

сравнения, второй вход которого подключен к выходу блока анализа кодов, третий вход которого подключен к первому выходу блока синхронизации, вход которого подключен к третьему 0 входу блока формирования адреса и к , второму выходу блока приоритета, третий вход которого подключен к выходу первого элемента ИЛИ, первьШ вход ко5 торого является четвертым управляющим входом устройства, второй вход первого элемента ИЛИ подключен к выходу второго элемента И, первый вход первого элемента И подключен к второму выходу блока синхронизации и к первому входу второго элемента И, выход первого элемента И является первым управляющим выходом устройства, второй вход первого элемента И подключен к выходу блока сравнения и к входу первого элемента НЕ, вход второго элемента НЕ является вторым управляющим выходом устройства и подключен к второму выходу блока фор0 мирования адреса, третий выход которого является третьим управляющим выходом устройства, первый вход блока приоритета подключен к четвертому входу блока анализа кодов и к

5 первому входу второго элемента ИЛИ, второй вход которого является пятым управляющим входом устройства, выход второго элемента ИЛИ подключен к второму входу регистра.

0 2, Устройство по п.1, о т л и- чающе е с я тем, что блок анализа кодов содержит коммутатор, регистр, блок сравнения, элемент ИЛИ и элемент И, первый вход которого

45 является третьим входом блока анализа кодов, выход элемента И подключен к первому входу элемента ИЛИ, второй вход которого подключен к , первому входу коммутатора и являет50 ся четвертым входом блока анализа кодов, выход элемента 1-ШИ подключен-к первому входу регистра, второй вход которого, подключен к выходу коммутатора, второй вход ко55 торого является вторым входом блока анализа кЬдов, первый вход коммутатора является первым входом блока анализа кодов и подключен к первому

,1287236 ..

/о

входу блока сравнения, выход которо- второму входу блока сравнения и яв- го подключен к второму входу элемен- ляется выходом блока анализа кота И, выход регистра подключен к дов.

24

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1444893A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1048516A1 |

| Запоминающее устройство | 1982 |

|

SU1069000A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1439681A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1105940A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1295451A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

Изобретение относится к вычислительной технике и может быть ис- пользовано в качестве буферного запоминающего устройства каналов и устройств обмена, а также систем сбора и обработки информации. Цель изобретения г- расширение области применения за счет анализа храниь Ых данных. Буферное запоминающее устройство содержит блок 1 памяти, ин,формационный вход 2 и выход 3, блок 4 формирования адреса, блок 5 анализа кодов, блок 6 приоритета, блок 7 сравнения, регистр 8, элементы ИЛИ 9 и 10, блок 11 синхронизации, элементы И 12 и 13, элементы НЕ 14 и 15, управляющие входы 16 - 19, управляющие выходы 20 - 22 и управляющий вход 23. Данные, записьгоаемые в блок 1 по адресам, формируемым блоком 4, содержат код, характеризующий какой- либо синхронизирующий параметр. При считьшании данные анализируются в блоке 5 путем сравнения кода синхронизирующего параметра с кодом в регистре 8, записанным с входом 19, В случае совпадения или превьшения счи- тьшаемого значения параметра считанные из блока 1 данные передаются потребителю. В противном случае они удаляются из буферного устройства. 1 3.п. А-лы. 6 Ш1. с S (Л с ю 00 to со о

25

7ч /ч

Фиг. 2

Фиг. 3

2В

N

r

фиб.5

Составитель С.Шуетенко

Редактор А.Лежнина Техред А.Кравчук Корректор Н.Король

«.1-.и« я-«|и..-.-.-...i-,.вв,™«ви-«.«и,™.в.«ив«-.,..---.-«..- ..- в...-..™.- ...-.-.i-.- ,- .-.-----.--.- ,- -.

Заказ 7724/56 Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д,4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

gOwe.ff

| Буферное запоминающее устройство | 1982 |

|

SU1111202A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1075310A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-01-30—Публикация

1985-06-07—Подача