Изобретение относится к электронной коммутационной технике и может быть использовано в автоматических системах сбора информации.

Целью изобретения является расширение функциональных возможностей, достигаемое путем обеспечения индивидуального изменения длительности опроса источников информации при по- .стоянкой частоте тактовых импульсов генератора.

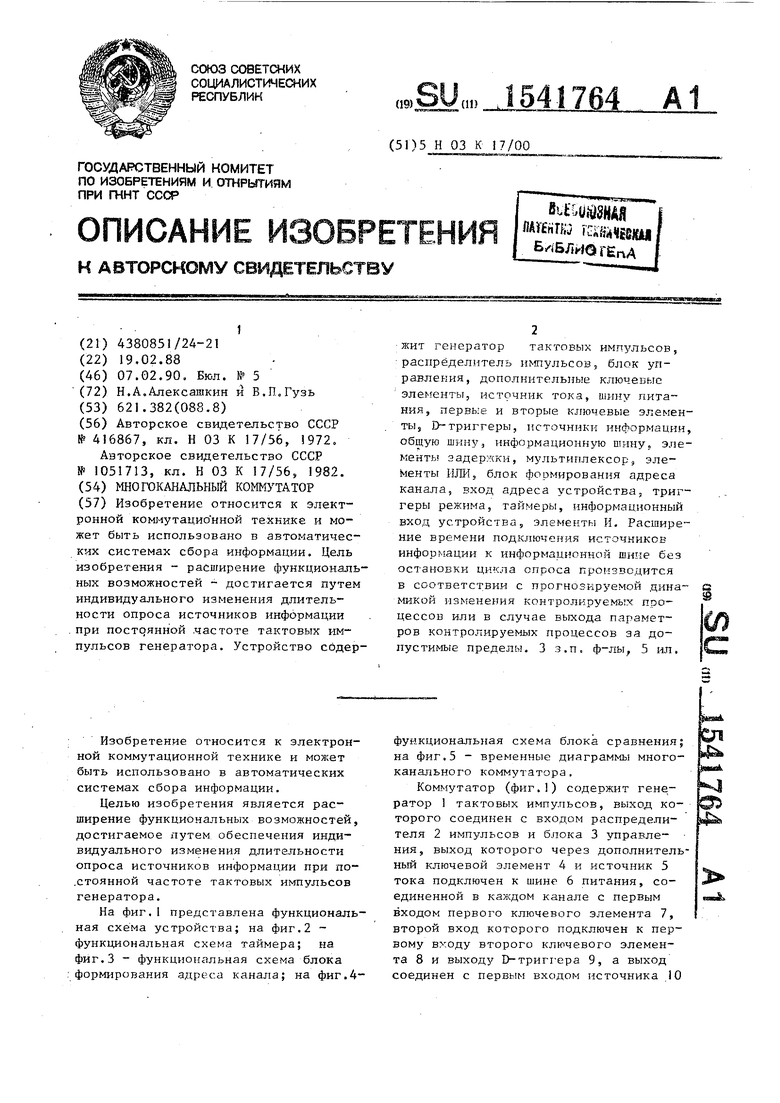

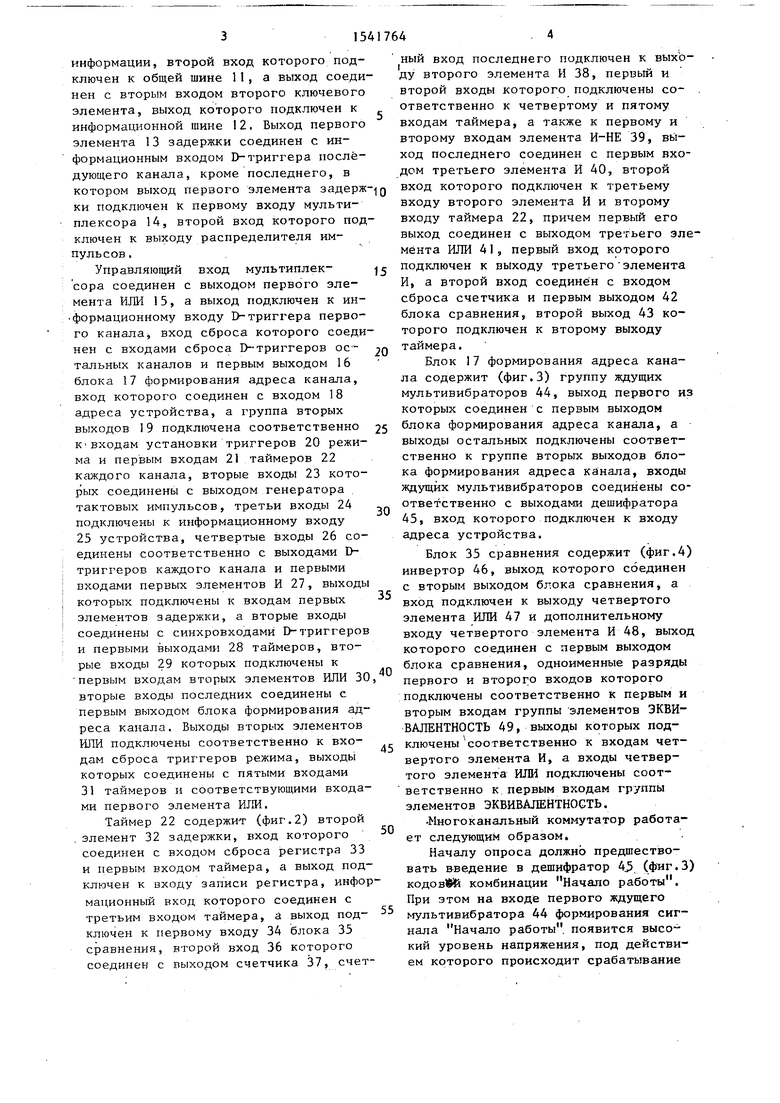

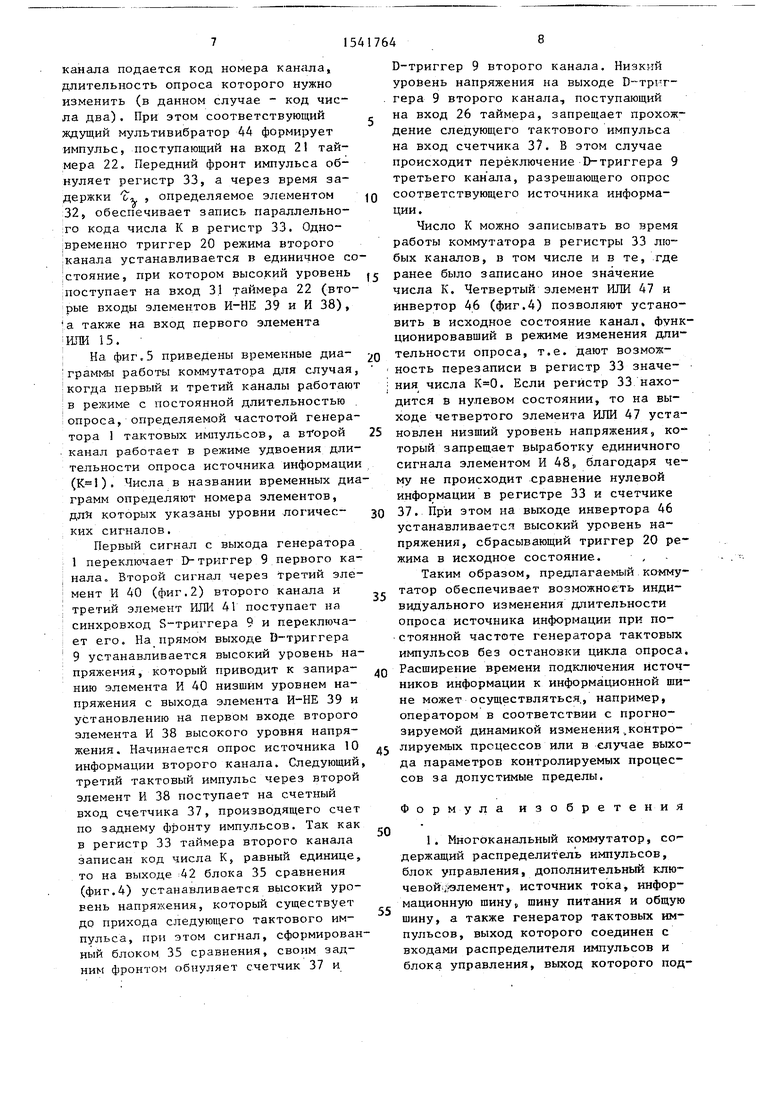

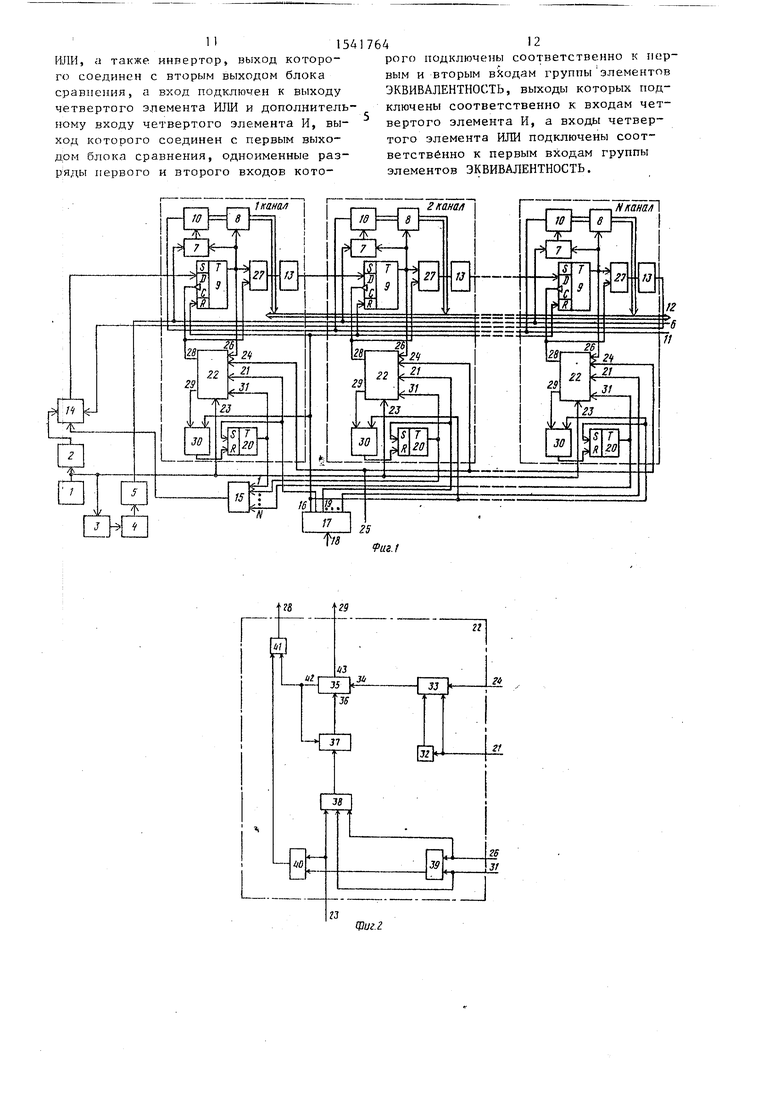

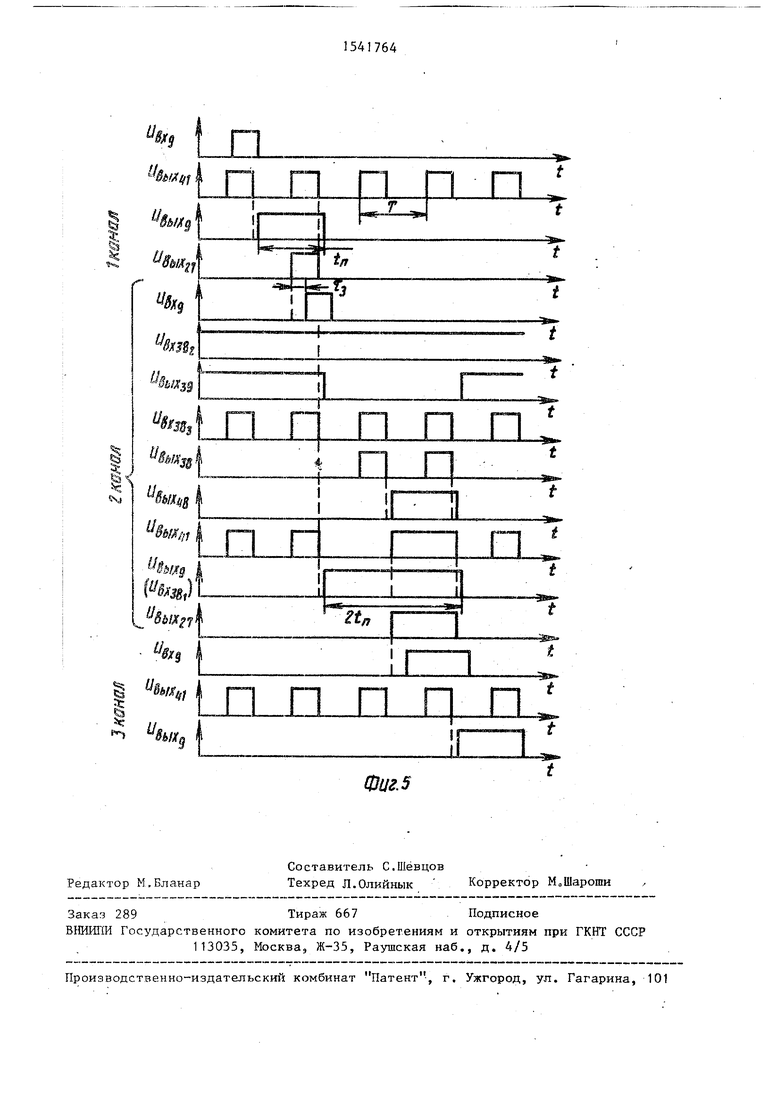

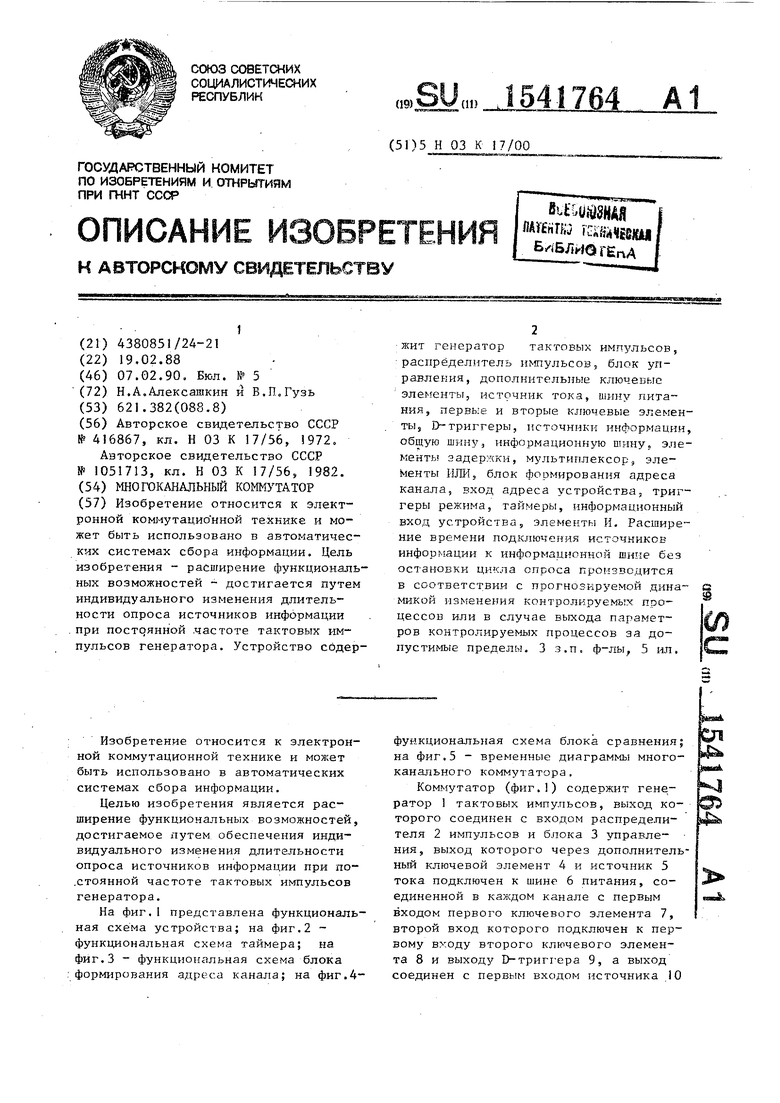

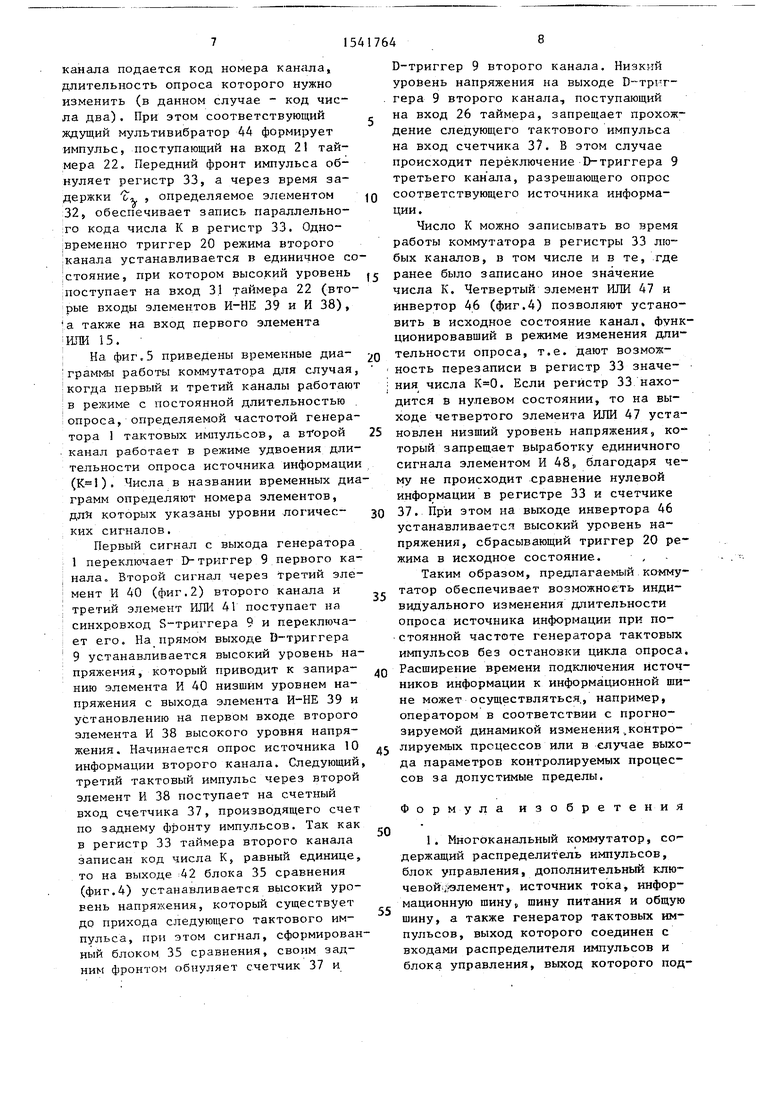

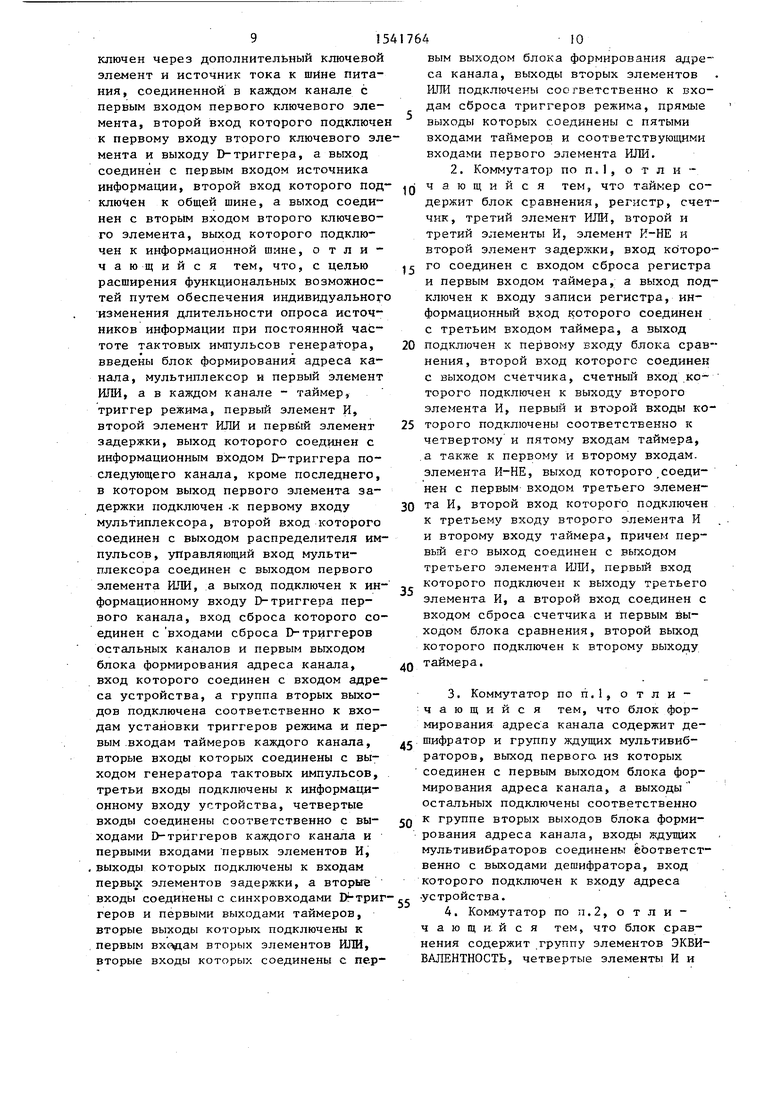

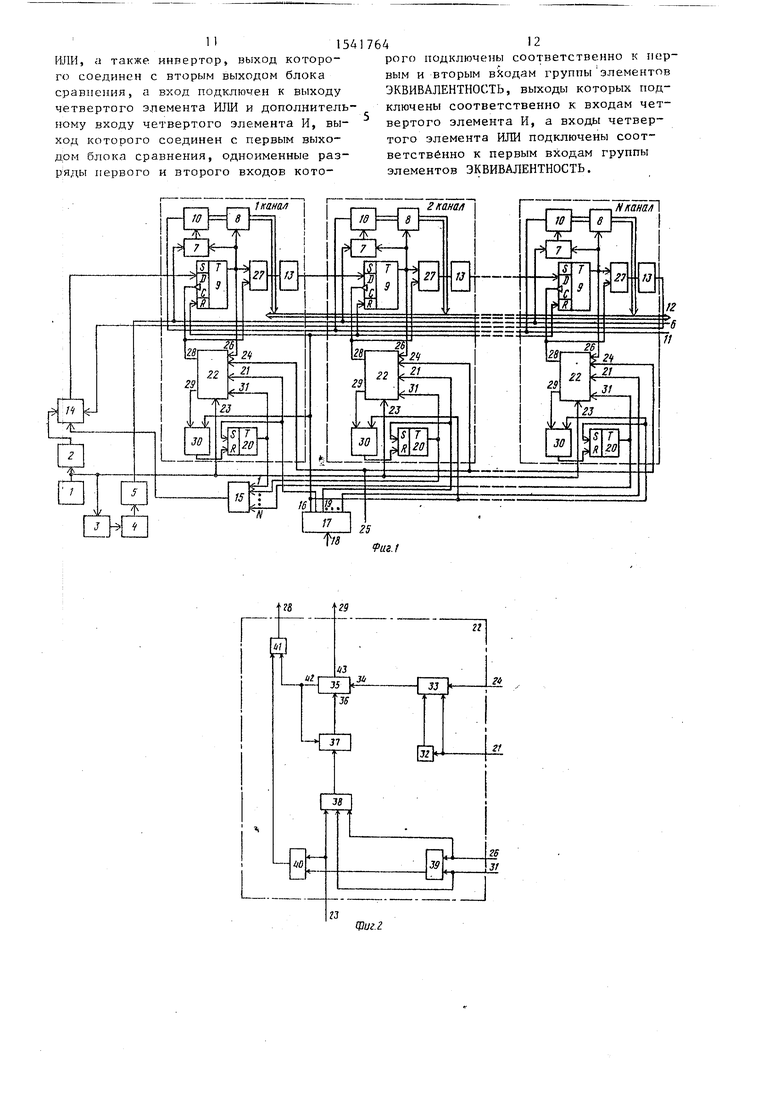

На фиг.1 представлена функциональная схема устройства; на фиг.2 - функциональная схема таймера; на фиг.З - функциональная схема блока формирования адреса канала; на фиг.4функциональная схема блока сравнения; на фиг.5 - временные диаграммы многоканального коммутатора.

Коммутатор (фиг.) содержит генератор 1 тактовых импупьсов, выход которого соединен с входом распределителя 2 импульсов и блока 3 управления, выход которого через дополнительный ключевой элемент 4 и источник 5 тока подключен к шине 6 питания, соединенной в каждом канале с первым входом первого ключевого элемента 7, второй вход которого подключен к первому второго ключевого элемента 8 и выходу D-триггера 9, а выход соединен с первым входом источника 10

gaent СП

информации, второй вход которого подключен к общей шине 11, а выход соединен с вторым входом второго ключевого элемента, выход которого подключен к информационной шине 12. Выход первого элемента 13 задержки соединен с информационным входом D-триггера последующего канала, кроме последнего, в котором выход первого элемента задержки подключен К первому входу мультиплексора 14, второй вход которого подключен к выходу распределителя импульсов .

Управляющий вход мультиплексора соединен с выходом первого элемента ИЛИ 15, а выход подключен к информационному входу D-триггера первого канала, вход сброса которого соединен с входами сброса D-триггеров остальных каналов и первым выходом 16 блока 17 формирования адреса канала, вход которого соединен с входом 18 адреса устройства, а группа вторых выходов 19 подключена соответственно к входам установки триггеров 20 режима и первым входам 21 таймеров 22 каждого канала, вторые входы 23 которых соединены с выходом генератора тактовых импульсов, третьи входы 24 подключены к информационному входу 25 устройства, четвертые входы 26 соединены соответственно с выходами D- триггеров каждого канала и первыми входами первых элементов И 27, выходы которых подключены к входам первых элементов задержки, а вторые входы соединены с синхровходами D-триггеров и первыми выходами 28 таймеров, вторые входы 29 которых подключены к первым входам вторых элементов ИЛИ 30. вторые входы последних соединены с первым выходом блока формирования адреса канала. Выходы вторых элементов ИЛИ подключены соответственно к входам сброса триггеров режима, выходы которых соединены с пятыми входами 31 таймеров и соответствующими входами первого элемента ИЛИ.

Таймер 22 содержит (фиг.2) второй элемент 32 задержки, вход которого соединен с входом сброса регистра 33 и первым входом таймера, а выход подключен к входу записи регистра, информационный вход которого соединен с третьим входом таймера, а выход подключен к первому входу 34 блока 35 сравнения, второй вход 36 которого соединен с выходом счетчика 37, счет0

5

0

5

0

5

0

5

0

5

ный вход последнего подключен к выходу второго элемента И 38, первый и второй входы которого подключены соответственно к четвертому и пятому входам таймера, а также к первому и второму входам элемента И-НЕ 39, выход последнего соединен с первым входом третьего элемента И 40, второй вход которого подключен к третьему входу второго элемента И и второму входу таймера 22, причем первый его выход соединен с выходом третьего элемента ИЛИ 4 1 9 первый вход которого подключен к выходу третьего элемента И, а второй вход соединен с входом сброса счетчика и первым выходом 42 блока сравнения, второй выход 43 которого подключен к второму выходу таймера.

Блок 17 формирования адреса канала содержит (фиг.З) группу ждущих мультивибраторов 44, выход первого из которых соединен с первым выходом блока формирования адреса канала, а выходы остальных подключены соответственно к группе вторых выходов блока формирования адреса канала, входы ждущих мультивибраторов соединены соответственно с выходами дешифратора 45, вход которого подключен к входу адреса устройства.

Блок 35 сравнения содержит (фиг.4) инвертор 46, выход которого соединен с вторым выходом блока сравнения, а вход подключен к выходу четвертого элемента ИЛИ 47 и дополнительному входу четвертого элемента И 48, выход которого соединен с первым выходом блока сравнения, одноименные разряды первого и второго входов которого подключены соответственно к первым и вторым входам группы элементов ЭКВИВАЛЕНТНОСТЬ 49, выходы которых подключены 1 соответственно к входам четвертого элемента И, а входы четвертого элемента ИЛИ подключены соответственно к первым входам группы элементов ЭКВИВАЛЕНТНОСТЬ.

Многоканальный коммутатор работа- ет следующим образом.

Началу опроса должно предшествовать введение в дешифратор 43 (фиг.З) кодовой комбинации Начало работы. При этом на входе первого ждущего мультивибратора 44 формирования сигнала Начало работы появится высокий уровень напряжения, под действием которого происходит срабатывание

515

первого ждущего мультивибратора 44. Сигнал, который является на выходе 16, устанавливает в исходное состояние все D-триггеры 9 и триггеры 20 режима. На их прямых выходах установится низкий уровень напряжения. При этом ключевые элементы 7 и 8 оказываются запертыми, и источники информации отключены от информационной шины 12. Нулевой потенциал на выходах триггеров 20 режима исключает работу каналов в режиме с изменением длительности опроса источников 10 информации. При этом на выходе первого элемента ИЛИ 15 имеется низкий уровень напряжения, обеспечивающий прохождение импульсов с выхода распределителя 2 импульсов на информационный вход D-триггера 9 первого канала. Высокий уровень напряжения, поступающий на управляющий вход мультиплексора 14, разрешает прохождение на вход D-триггера 9 первого канала сигналов с выхода элемента 13 задержки последнего канала и запрещает прохождение сигналов с выхода распределителя 2 импульсов.

Генератор 1 тактовых импульсов формирует последовательность тактовых импульсов с периодом повторения Т. Распределитель 2 импульсов, представляющий собой делитель частоты тактовых импульсов на п, где п - число ис точников информации (датчиков), выде- ляет из последовательности тактовых импульсов каждый n-й импульс, который с выхода распределителя импульсов через мультиплексор 14 поступает на информационный вход D-триггера 9 первого канала.

Так как на прямом выходе триггера 20 режима низкий уровень напряжения, на выходе элемента И-НЕ 39 (фиг.2) и первом входе третьего элемента И 40 устанавливается высокий потенциал.

Сигнал тактовой частоты Fr 1/Т генератора 1 тактовых импульсов через третий элемент И 40 первого канала и третий элемент ИЛИ 41 первого канала поступает на синхронизирующий вход D-триггера 9 первого канала и переключает его.

На выходе D-триггера первого канала устанавливается высокий уровень напряжения, который открывает ключевые элементы 7 и 8 этого канала. В результате этого источник 10 информации первого камгша подключается к ши10

15

20

35

7646

не 6 питания и информационной шине 12.

При этом ключевые элементы 7 и 8 остальных канале заперты и опрос других источников информации не производится.

Следующий тактовый импульс, поступающий на синхронизирующие вход1; D-трнггеров, переключает D-триггеры первого н второго каналов. При этом на выходе триггера 9 первого канала устанавливается низкий потенциал и опрос источника информации этого канала прекращается. На выходе триггера 9 второго канала устанавливается высокий уровень напряжения и начинается опрос истопника 10 информации второго канала.

Так как D-триггеры срабатывают по заднему фронту импульса, в схеме предусмотрен элемент 13 задержки, параметр которого ty (фиг.5) выбирается так, чтобы обеспечить надежное 25 переключение D-триггеров 9.

После того, как опрошен источник информации последнего канала, распределитель 2 импульсов формирует новый импульс запуска D-триггера первого канала, и процесс сбора информации повторяется.

Последовательность тактовых импульсов, вырабатываемая генератором 1 тактовых импульсов, поступает также на блок 3 управления, формирующий последовательность импульсов длительностью t и периодом повторения Т, которые поступают через дополнительный ключевой элемент 4 на источник 5 тока, который включает питание каналов только на время их опроса t. В паузе источник 5 тока отключен от всех каналов.

Коммутатор при изменении длитель- г ности опроса источников информации работает следующим образом. Перед началом работы введением в дешифратор 45 (фиг.З) кодовой комбинации Начало работы все триггеры 20 режима и Q D-триггеры 9 устанавливаются в нулевое состояние- для исключения неопределенности.

Пусть необходимо увеличить длительность опроса источника 10 инфор- .мации второго канала в цикле опроса

30

40

5

на KtK, где К - число, вводимое по информационному входу 25 устройства в регистр 33 (фиг.2). На вход дешифратора 45 блока формирования адреса

канала подается код номера канала, длительность опроса которого нужно изменить (в данном случае - код числа два). При этом соответствующий ждущий мультивибратор 44 формирует импульс, поступающий на вход 21 таймера 22. Передний фронт импульса обнуляет регистр 33, а через время задержки t, , определяемое элементом 32s обеспечивает запись параллельного кода числа К в регистр 33. Одновременно триггер 20 режима второго канала устанавливается в единичное состояние, при котором высокий уровень поступает на вход 31 таймера 22 (вторые входы элементов И-НЕ 39 и И 38), а также на вход первого элемента ИЛИ 15.

На фиг,5 приведены временные диа- граммы работы коммутатора для случая, когда первый и третий каналы работают в режиме с постоянной длительностью опроса, определяемой частотой генератора 1 тактовых импульсов, а второй канал работает в режиме удвоения длительности опроса источника информации (). Числа в названии временных диаграмм определяют номера элементов, для которых указаны уровни логических сигналов.

Первый сигнал с выхода генератора 1 переключает D-триггер 9 первого канала. Второй сигнал через третий элемент И 40 (фиг.2) второго канала и третий элемент ИЛИ 41 поступает на синхровход S-триггера 9 и переключает его. На прямом выходе D-триггера 9 устанавливается высокий уровень напряжения, который приводит к запиранию элемента И 40 низшим уровнем напряжения с выхода элемента И-НЕ 39 и установлению на первом входе второго элемента И 38 высокого уровня напряжения. Начинается опрос источника 10 информации второго канала. Следующий, третий тактовый импульс через второй элемент И 38 поступает на счетный вход счетчика 37, производящего счет по заднему фронту импульсов. Так как в регистр 33 таймера второго канала записан код числа К, равный единице, то на выходе 42 блока 35 сравнения (фиг.4) устанавливается высокий уровень напряжения, который существует до прихода следующего тактового импульса, при этом сигнал, сформированный блоком 35 сравнения, своим задним фронтом обнуляет счетчик 37 и

5

0

5

0

5

0

5

0

5

D-триггер 9 второго канала. Низкий уровень напряжения на выходе D-триг- гера 9 второго канала, поступающий на вход 26 таймера, запрещает прохождение следующего тактового импульса на вход счетчика 37. В этом случае происходит переключение D-триггера 9 третьего канала, разрешающего опрос соответствующего источника информации.

Число К можно записывать во время работы коммутатора в регистры 33 любых каналов, в том числе и в те, где ранее было записано иное значение числа К. Четвертый элемент ИЛИ 47 и инвертор 46 (фиг.4) позволяют установить в исходное состояние канал, функционировавший в режиме изменения длительности опроса, т.е. дают возможность перезаписи в регистр 33 значения числа . Если регистр 33 находится в нупевом состоянии, то на выходе четвертого элемента ИЛИ 47 установлен низший уровень напряжения, который запрещает выработку единичного сигнала элементом И 48, благодаря чему не происходит сравнение нулевой информации в регистре 33 и счетчике 37. При этом на выходе инвертора 46 устанавливается высокий уровень на пряжения, сбрасывающий триггер 20 режима в исходное состояние.

Таким образом, предлагаемый коммутатор обеспечивает возможность индивидуального изменения длительности опроса источника информации при постоянной частоте генератора тактовых импульсов без остановки цикла опроса. Расширение времени подключения источников информации к информационной шине может осуществляться, например, оператором в соответствии с прогнозируемой динамикой изменения .контролируемых процессов или в случае выхода параметров контролируемых процессов за допустимые пределы.

Формула изобретения

1. Многоканальный коммутатор, содержащий распределитель импульсов, блок управления, дополнительный ключевой,-элемент, источник тока, информационную шину, шину питания и общую шину, а также генератор тактовых импульсов, выход которого соединен с входами распределителя импульсов и блока управления, выход которого подключей через дополнительный ключевой элемент и источник тока к шине питания, соединенной в каждом канале с первым входом первого ключевого элемента, второй вход которого подключен к первому входу второго ключевого элемента и выходу D-триггера, а выход соединен с первым входом источника информации, второй вход которого подключен к общей шине, а выход соединен с вторым входом второго ключевого элемента, выход которого подключен к информационной шине, отличающийся тем, что, с целью расширения функциональных возможностей путем обеспечения индивидуального изменения длительности опроса источников информации при постоянной частоте тактовых импульсов генератора, введены блок формирования адреса канала, мультиплексор и первый элемент ИЛИ, а в каждом канале - таймер, триггер режима, первый элемент И, второй элемент ИЛИ и первый элемент задержки, выход которого соединен с информационным входом D-триггера последующего канала, кроме последнего, в котором выход первого элемента задержки подключен -к первому входу мультиплексора, второй вход которого соединен с выходом распределителя импульсов, управляющий вход мультиплексора соединен с выходом первого элемента ИЛИ, а выход подключен к информационному входу D-триггера первого канала, вход сброса которого соединен с входами сброса D-триггеров остальных каналов и первым выходом блока формирования адреса канала, вход которого соединен с входом адреса устройства, а группа вторых выходов подключена соответственно к входам установки триггеров режима и первым входам таймеров каждого канала, вторые входы которых соединены с выходом генератора тактовых импульсов, третьи входы подключены к информационному входу устройства, четвертые входы соединены соответственно с выходами D-триггеров каждого канала и первыми входами первых элементов И, выходы которых подключены к входам первых элементов задержки, а вторые

15

20

25

вым выходо са канала, ИЛИ подклю дам сброса выходы кот входами та входами пе

2.Комм jg чающи держит бло чик, трети третий элем второй элем го соединен и первым вх ключен к вх формационны

с третьим в подключен к нения, втор с выходом с торого подк элемента И торого подк четвертому а также к п элемента Инен с первы та И, второ к третьему и второму в вый его вых третьего эл которого по элемента И, входом сбро ходом блока которого по AQ таймера.

3.Комму чающий мирования а

. шифратор и раторов, вы соединен с мирования а остальных п

JQ к группе вт рования адр мультивибра венно с вых которого по

30

35

входы соединены с синхровходами 1 -триг-,-5 -устройства.

геров и первыми выходами таймеров, вторые выходы которых подключены к первым входам вторых элементов ИЛИ, вторые входы которых соединены с пер4. Комму чающий нения содер ВАЛЕНТНОСТЬ

5

0

5

вым выходом блока формирования адреса канала, выходы вторых элементов ИЛИ подключены соответственно к входам сброса триггеров режима, прямые выходы которых соединены с пятыми входами таймеров и соответствующими входами первого элемента ИЛИ.

2.Коммутатор по п.1, о т л и - g чающийся тем, что таймер содержит блок сравнения, регистр, счетчик, третий элемент ИЛИ, второй и третий элементы И, элемент И-НЕ и второй элемент задержки, вход которого соединен с входом сброса регистра и первым входом таймера, а выход подключен к входу записи регистра, информационный вход которого соединен

с третьим входом таймера, а выход подключен к первому входу блока сравнения, второй вход которого соединен с выходом счетчика, счетный вход которого подключен к выходу второго элемента И, первый и второй входы которого подключены соответственно к четвертому и пятому входам таймера, а также к первому и второму входам, элемента ИНЕ, выход которого соединен с первым входом третьего элемента И, второй вход которого подключен к третьему входу второго элемента И и второму входу таймера, причем первый его выход соединен с выходом третьего элемента ИЛИ, первый вход которого подключен к выходу третьего элемента И, а второй вход соединен с входом сброса счетчика и первым выходом блока сравнения, второй выход которого подключен к второму выходу Q таймера.

3.Коммутатор по п.отличающийся тем, что блок формирования адреса канала содержит де шифратор и группу ждущих мультивибраторов, выход первого, из которых соединен с первым выходом блока формирования адреса канала, а выходы остальных подключены соответственно

Q к группе вторых выходов блока формирования адреса канала, входы ждущих мультивибраторов соединены безответственно с выходами дешифратора, вход которого подключен к входу адреса

0

5

-устройства.

4. Коммутатор по л.2, отличающийся тем, что блок сравнения содержит группу элементов ЭКВИВАЛЕНТНОСТЬ, четвертые элементы И и

П154

ИЛИ, а также инвертор, выход которого соединен с вторым выходом блока сравнения, а вход подключен к выходу четвертого элемента ИЛИ и дополнительному входу четвертого элемента И, выход которого соединен с первым выходом блока сравнения, одноименные разряды первого и второго входов кото1764 2

рого подключены соответственно к первым и вторым входам группы элементов ЭКВИВАЛЕНТНОСТЬ, выходы которых подключены соответственно к входам чет5 вертого элемента И, а входы четвертого элемента ИЛИ подключены соответственно к первым входам группы элементов ЭКВИВАЛЕНТНОСТЬ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный коммутатор | 1989 |

|

SU1661986A1 |

| Многоканальный коммутатор | 1991 |

|

SU1780182A1 |

| Адаптивный многоканальный коммутатор | 1990 |

|

SU1800606A1 |

| Многоканальный коммутатор | 1987 |

|

SU1443159A1 |

| Многоканальный коммутатор | 1984 |

|

SU1226644A2 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для сопряжения абонентов с каналами связи | 1984 |

|

SU1233158A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

Изобретение относится к электронной коммутационной технике и может быть использовано в автоматических системах сбора информации. Цель изобретения - расширение функциональных возможностей - достигается путем индивидуального изменения длительности опроса источников информации при постоянной частоте тактовых импульсов генератора. Устройство содержит генератор тактовых импульсов, распределитель импульсов, блок управления, дополнительные ключевые элементы, источник тока, шину питания, первые и вторые ключевые элементы, D-триггеры, источники информации, общую шину, информационную шину, элементы задержки, мультиплексор, элементы ИЛИ, блок формирования адреса канала, вход адреса устройства, триггеры режима, таймеры, информационный вход устройства, элементы И. Расширение времени подключения источников информации к информационной шине без остановки цикла опроса производится в соответствии с прогнозируемой динамикой изменения контролируемых процессов или в случае выхода параметров контролируемых процессов за допустимые пределы. 3 з.п.ф-лы, 5 ил.

гз

(Риг г

16

Щ Щ

N

НЕ

i

..

w Ш

36

79

Фиг.З

иг

4J

л

47

О

Г

Ф(/г

| 0 |

|

SU416867A1 | |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Многоканальный коммутатор | 1982 |

|

SU1051713A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-02-07—Публикация

1988-02-19—Подача