Изобретение относится к радиоэлектронике, в частности к электронной коммутационной технике, и может быть использовано в автоматических системах сбора информации.

Цель изобретения - упрощение устройства и повышение надежности за счет устранения возможности возникновения неоднозначности в работе.

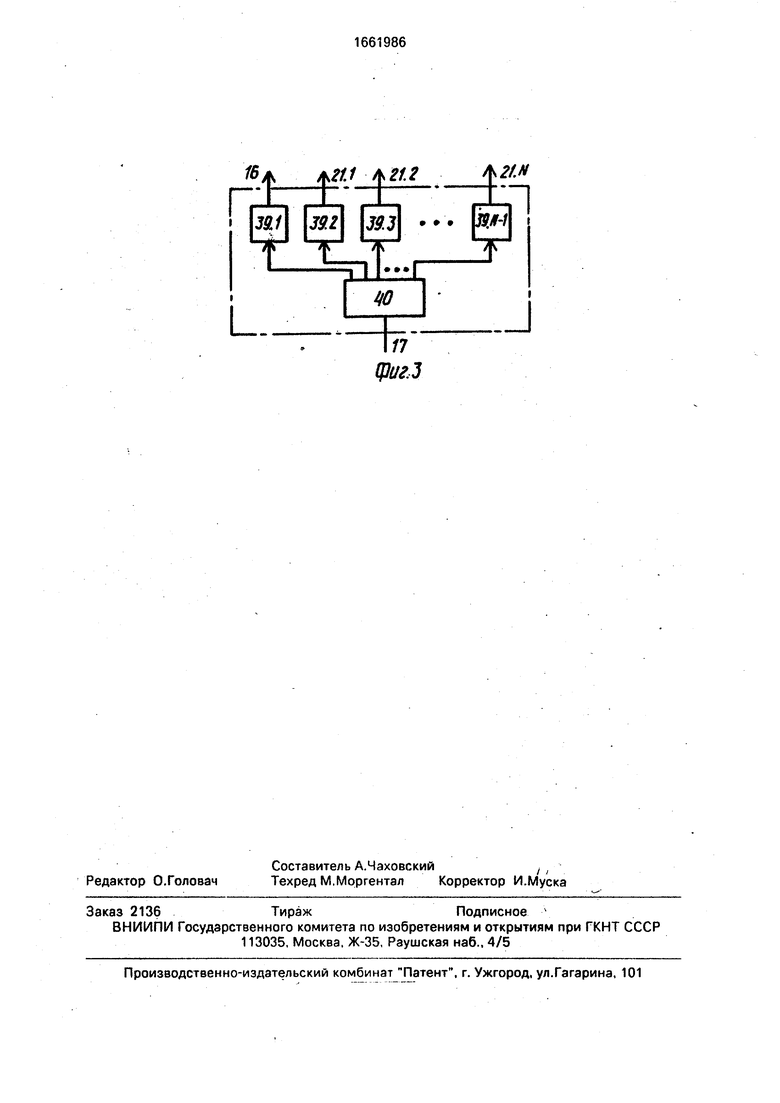

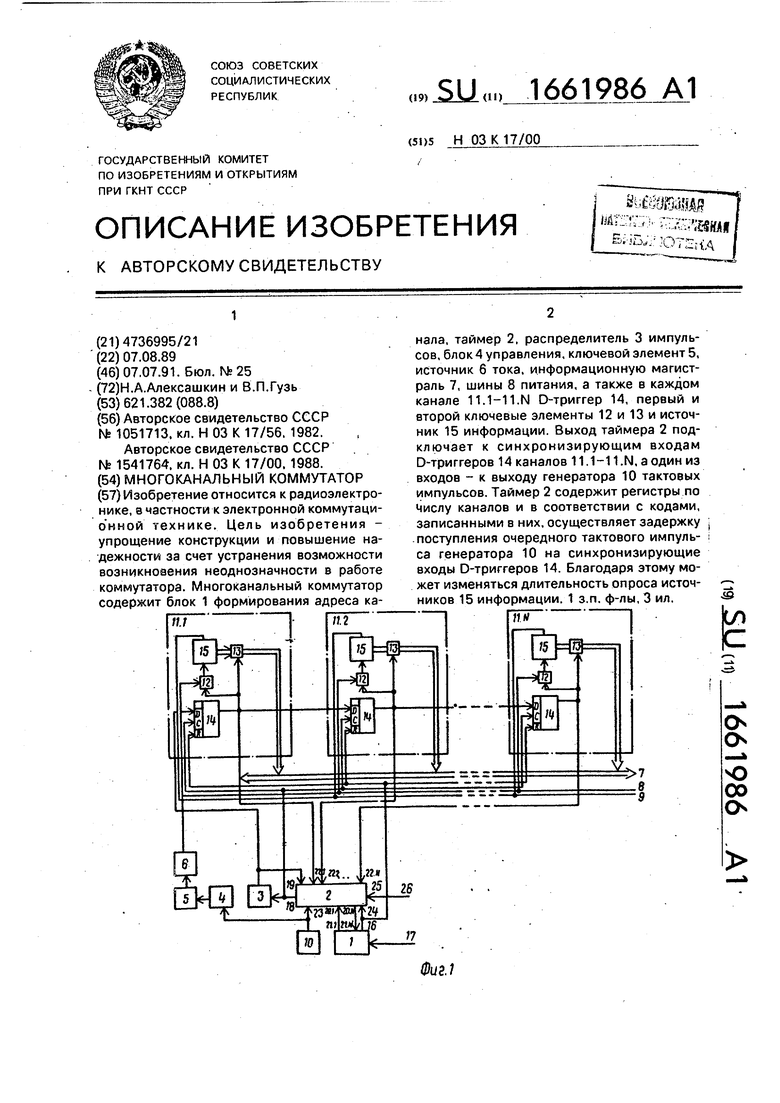

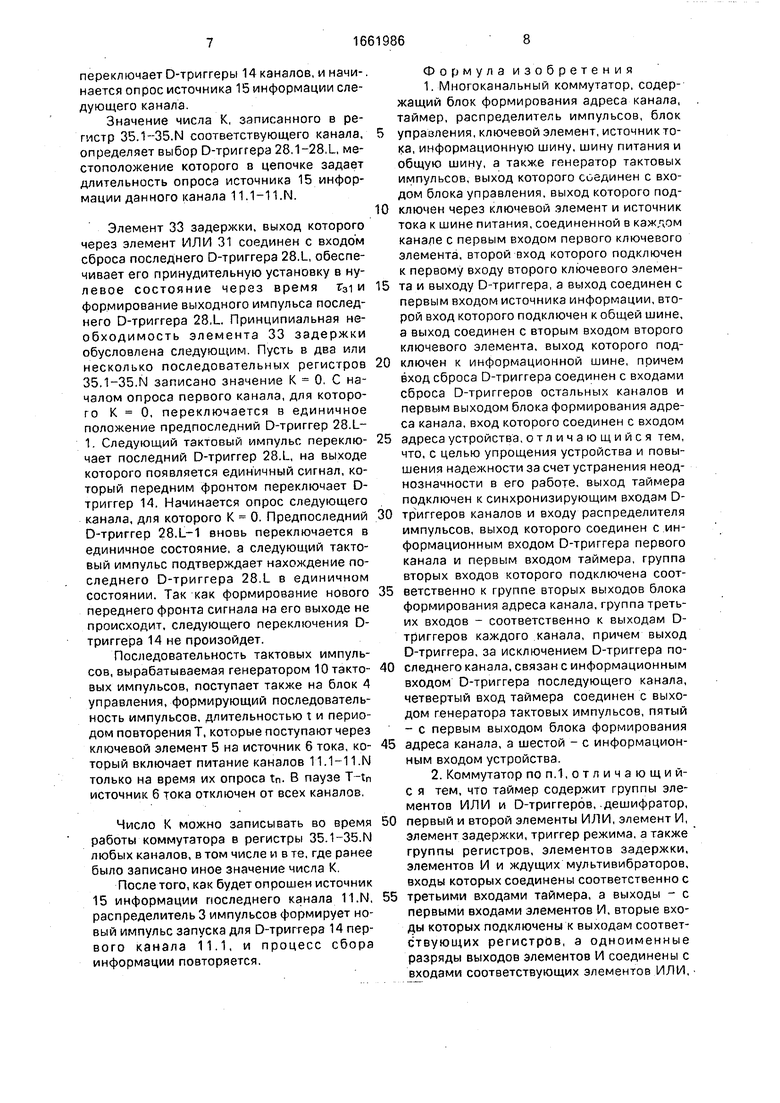

На фиг.1-3 представлены функциональные схемы многоканального коммутатора, таймера и блока формирования адреса каналов соответственно.

Многоканальный коммутатор (фиг.1) содержит блок 1 формирования адреса канала, таймер 2, распределитель 3 импульсов, блок 4 управления, ключевой элемент 5, источник 6 тока, информационную шину 7, шину 8 питания, общую шину 9, генератор 10 тактовых импульсов, выход которого соединен с входом блока 4 управления, выход которого подключен через ключевой элемент 5 и источник 6 тока к шине 8 питания, соединенной в каждом канале 11.1,...,11. N с первым входом первого ключевого элемента 12, второй вход которого подключен к первому входу второго ключевого элемента 13 и выходу D-триггера 14, а выход соединен с первым входом источника 15 информации, второй вход которого подключен к общей шине 9, а выход соединен с вторым входом второго ключевого элемента 13, выход которого подключен к информационной шине 7, причем вход сброса D-триггера 14 первого канала 11.1 соединен с входами сброса Dтриггера 14 остальных каналов 11.211.N

и первым выходом 16 блока 1 формирования адреса канала, вход которого соединен с входом 17 адреса устройства, при этом выход 18 таймера подключен к синхровходам D-триггеров 14 каналов 11.1-11.N и к входу распределителя 3 импульсов, выход которого соединен с информационным входом D- триггера 14 первого канала 11.1 и первым входом 19 таймера 2, группа вторых входов 20.1-20.N которого подключена соответственно к группе вторых выходов 21.1-21.N блока 1 формирования адреса канала, группа третьих входов 22.1-22 N соответственно к выходам D-трйггеров 14 каждого канала 11.1-11.N, выход D-триггера 14 которых, за исключением D-триггера 14 последнего канала 11.N. связан с информационным входом D-триггера 14 последующего канала 11.2-11.N, четвертый вход 23 таймера 2 соединен с выходом генератора 10 тактовых импульсов, пятый вход 24 - с первым выходом 16 блока 1 формирования адреса канала, а шестой вход 25 - с информационным входом 26 устройства

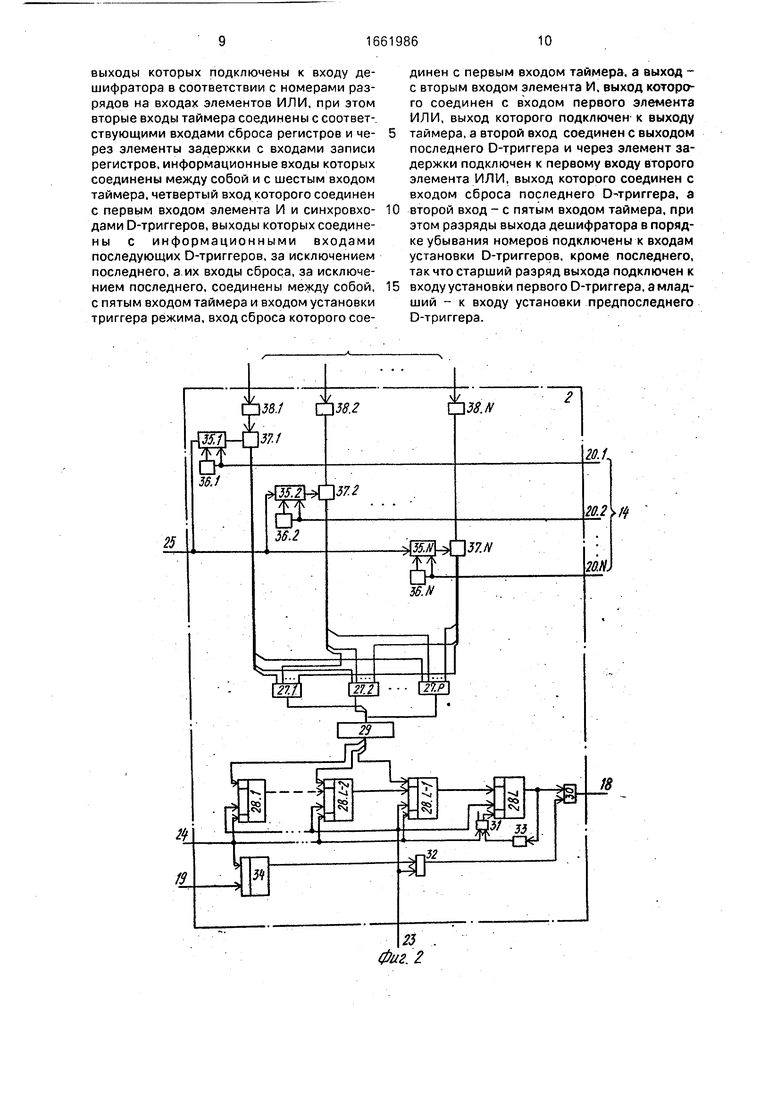

Таймер 2 (фиг.2) содержит группу элементов ИЛИ 27.1-27 Р и D-триггеров 28.1- 28.L дешифратор 29, первый 30 и второй 31 элементы ИЛИ, элемент И 32, элемент 33

задержки, триггер 34 режима, а также группы регистров 35.1-35.N, элементов 36.1- 36.N задержки, элементов И 37.1-37.N и ждущих мультивибраторов 38.1-38.N, входы которых соединены с соответствующими

0 третьими входами 22.1-22.N таймера 2, а выходы - с первыми выходами соответствующих элементов И 37.1-37,N, вторые входы которых подключены к выходам соответствующих регистров 35.1-35.N, а одноимен5 ные разряды выходов элементов И 37.1-37.N соединены с входами соответствующих элементов ИЛИ 27,1-27.Р, выходы которых подключены к входу дешифратора 29 в соответствии с номерами разрядов на

0 входах элементов ИЛИ 27.1-27.Р, при этом вторые входы 20.1-20.N таймера 2 соединены с соответствующими входами сброса регистров 35.1-35.N и через элементы 36.1-36.N задержки с входами записи реги5 строе 35.1-35.N, информационные входы которых соединены между собой и с шестым входом 25 таймера 2, четвертый вход 23 которого соединен с первым входом элемента И 32 и синхровходами D-триггеров

0 28.1-28.L, выходы D-триггеров 28.1-28.L- 1 соединены с информационными входами последующих D-триггеров 28.2-28.L, входы сброса D-триггеров 28.1-28.L-1, соединены между собой, с пятым входом 24 таймера 2

5 и с входом установки триггера 34 режима, вход сброса которого соединен с первым входом 19 таймера 2, а выход - с вторым входом элемента И 32, выход которого соединен с входом первого элемента ИЛИ 30,

0 выход которого подключен к выходу 18 таймера 2, а второй вход соединен с выходом последнего D-триггера 28.L и через элемент 33 задержки с первым входом второго элемента ИЛИ 31, выход которого соединен с

5 входом сброса последнего D-триггера 28.L, а второй вход - с пятым входом 24 таймера 2. При этом выходы дешифратора 29 в порядке убывания номеров подключены к входам установки D-триггеров 28.1-28.L-1 так,

0 что старший выход дешифратора 29 подключен к входу установки первого D-триггера 28.1, а младший - к входу установки предпоследнего D-триггера 28.L-1..

Блок 1 формирования адреса канала

5 (фиг.З) устройства содержит группу ждущих мультивибраторов 39.1-39.N, выход первого из которых соединен с первым выходом 16 блока 1 формирования адреса канала, а выходы остальных подключены соответственно к группе вторых выходов 21.1-21.N

блока 1 формирования адреса канала, входы ждущих мультивибраторов 39..NM соединены соответственно с выходами дешифратора 40, вход которого подключен к входу блока 1.

Многоканальный коммутатор работает следующим образом.

Началу опроса должно предшествовать введение в дешифратор 40 (фиг.З) кодовой комбинации Начало работы. При этом на входе первого ждущего мультивибратора 39.1 формируется высокий уровень напряжения, который появляется на выходе 16, устанавливает в исходное состояние D- триггеры 14, D-триггеры 28.1-28.L и триггер 34 режима. На прямых выходах D-триггеров устанавливается низкий уровень напряжения, на выходе триггера 34 режима - высокий. При этом ключевые элементы 12 и 13 оказываются запертыми, и источники 15 ин- фо рмации отключены от информационной шины 7. Длительности опроса источников информации в исходном режиме определяются периодом тактовой частоты генератора 10 тактовых импульсов и равны tn. Пусть необходимо увеличить длительность опроса источника информации 15 на K-tn, где К - число, вводимое по информационному входу 26 устройства в соответствующий регистр 35.1-35.N таймера 2. На вход дешифратора 40 блока 1 формирования адреса канала подается код номера канала, длительность опроса которого нужно изменить. При этом соответствующий ждущий мультивибратор 39.2-39.N+1 формирует импульс, поступающий йа соответствующий второй вход 20.1-20.N таймера 2. Передний фронт импульса обнуляет соответствующий регистр 35.1-35.N, а через время задержки Г3, определяемое соответствующим элементом 36,1-36.N задержки, обеспечивает запись параллельного кода числа К в выбранный регистр.

Генератор 10 тактовых импульсов формирует последовательность тактовых импульсов с периодом повторения Т. Сигналы тактовой частоты через элемент И 32. на втором входе которого высокий уровень напряжения, и первый элемент ИЛИ 30 посту- пают на синхронизирующие входы D-триггеров 14 и распределитель 3, представляющий собой счетчик и выделяющий из последовательности входных импульсов каждый N-й импульс, где N - число источников информации.

Сигнал, появившийся на выходе распределителя 3 импульсов, поступает на информационный вход D-триггера 14 первого канала 11.1, на синхронизирующем входе

которого в этот момент присутствует сигнал с выхода 18 таймера 2 D-триггер 14 первого канала 11.1 переключается, на его выходе устанавливается высокий уровень напряже- ния, который открывает ключевые элементы 12 и 13 этого канала. В результате источник 15 информации первого канала 11.1 подключается к шине 8 питания и информационной шине 7. При этом ключевые элементы

0 12 и 13 остальных каналов заперты, и опрос других источников 15 информации не производится.

Передний фронт сигнала на выходе D- триггера 14 вызывает срабатывание соот5 ветствующего ждущего мультивибратора 38.1-38.N, который формирует импульс, открывающий соответствующий элемент И 37.1-37.N. Так как i-й разряд входа дешифратора 29 соединен с выходом элемента

0 ИЛИ 27.i, объединяющего 1-е разряды выходов вторых элементов И 37.1-37.Р, параллельный код числа К, записанного в регистре 35.1 первого канала 11.1, через элемент И 37.1 и элемент ИЛИ 27.1-27.Р

5 поступает на вход дешифратора 29. В соответствии со значением числа К, записанным в регистре 35.1-35.N опрашиваемого канала, на определенном выходе дешифратора 29 формируется импульс, длительность ко0 торого зависит от параметров соответствующего ждущего мультивибратора 38.1-38.N. Этот импульс передним фронтом устанавливает в единичное состояние соответствующий D-триггер 28.1-28 L. Число D5 триггеров 28.1-28.L определяется количеством выходных разрядов дешифратора 29 и не больше L 2 (так как в зависимости от величины К могут быть задействованы все или не все выходные раз0 ряды дешифратора 29). При этом старший разряд дешифратора 29, соответствующий Ктах, соединен с первым D-триггером 28.1, а младший (соответствующий ) - с предпоследним D-триггером 28.L-1. Так как в

5 этот момент триггер 34 режима сигналом с выхода распределителя 3 импульсов установлен в нулевое состояние, следующий импульс тактовой частоты генератора 10 тактовых импульсов не поступает через эле0 менты И 32 и ИЛИ 30 на выход 18 таймера 2, а переключает соответствующий D-триггер 28.1-28.L, находящийся в единичном положении. Следующий тактовый импульс вызывает переключение следующего D5 триггера 28.1-28.L. Процесс переключения этих триггеров повторяется до тех пор. пока не переключится последний D-григгер 28.L, выход которого через элемент ИЛИ 30 связан с выходом 18 таймера 2. Сигнал на выходе 18 таймера 2 своим передним фронтом

переключает D-триггеры 14 каналов, и начи-. нается опрос источника 15 информации следующего канала.

Значение числа К, записанного в регистр 35.1-35.N соответствующего канала, определяет выбор D-триггера 28.1-28,L, местоположение которого в цепочке задает длительность опроса источника 15 информации данного канала 11.1-11.N.

Элемент 33 задержки, выход которого через элемент ИЛИ 31 соединен с входом сброса последнего D-триггера 28.L, обеспечивает его принудительную установку в нулевое состояние через время г31 и формирование выходного импульса последнего D-триггера 28,L Принципиальная необходимость элемента 33 задержки обусловлена следующим. Пусть в два или несколько последовательных регистров 35.1-35.N записано значение К 0. С началом опроса первого канала, для которого К 0, переключается в единичное положение предпоследний D-триггер 28.L- 1. Следующий тактовый импульс переключает последний D-триггер 28.L, на выходе которого появляется единичный сигнал, который передним фронтом переключает D- триггер 14. Начинается опрос следующего канала, для которого К 0. Предпоследний D-триггер 28.L-1 вновь переключается в единичное состояние, а следующий тактовый импульс подтверждает нахождение последнего D-триггера 28.L в единичном состоянии. Так как формирование нового переднего фронта сигнала на его выходе не происходит, следующего переключения D- триггера 14 не произойдет.

Последовательность тактовых импульсов, вырабатываемая генератором 10 тактовых импульсов, поступает также на блок 4 управления, формирующий последовательность импульсов, длительностью t и периодом повторения Т, которые поступают через ключевой элемент 5 на источник 6 тока, который включает питание каналов 11.1-11.N только на время их опроса т.п. В паузе T-tn источник 6 тока отключен от всех каналов.

Число К можно записывать во время работы коммутатора в регистры 35.1-35.N любых каналов, в том числе и в те, где ранее было записано иное значение числа К.

После того, как будет опрошен источник 15 информации последнего канала 11.N, распределитель 3 импульсов формирует новый импульс запуска для D-тригтера 14 первого канала 11.1, и процесс сбора информации повторяется.

Формула изобретения

1.Многоканальный коммутатор, содержащий блок формирования адреса канала, таймер, распределитель импульсов, блок

управления, ключевой элемент, источник тока, информационную шину, шину питания и общую шину, а также генератор тактовых импульсов, выход которого соединен с входом блока управления, выход которого под0 ключей через ключевой элемент и источник тока к шине питания, соединенной в каждом канале с первым входом первого ключевого элемента, второй вход которого подключен к первому входу второго ключевого элемен5 та и выходу D-триггера, а выход соединен с первым входом источника информации, второй вход которого подключен к общей шине, а выход соединен с вторым входом второго ключевого элемента, выход которого под0 ключей к информационной шине, причем вход сброса D-триггера соединен с входами сброса D-триггеров остальных каналов и первым выходом блока формирования адреса канала, вход которого соединен с входом

5 адреса устройства, отличающийся тем, что, с целью упрощения устройства и повышения надежности за счет устранения неоднозначности в его работе, выход таймера подключен к синхронизирующим входам D0 триггеров каналов и входу распределителя импульсов, выход которого соединен с информационным входом D-триггера первого канала и первым входом таймера, группа вторых входов которого подключена соот5 ветственно к группе вторых выходов блока формирования адреса канала, группа третьих входов - соответственно к выходам D- триггеров каждого канала, причем выход D-триггера, за исключением D-триггера по0 следнего канала, связан с информационным входом D-триггера последующего канала, четвертый вход таймера соединен с выходом генератора тактовых импульсов, пятый - с первым выходом блока формирования

5 адреса канала, а шестой - с информационным входом устройства.

2.Коммутатор по п.1, о т л и ч а ю щ и й- с я тем, что таймер содержит группы элементов ИЛИ и D-триггеров, дешифратор,

0 первый и второй элементы ИЛИ, элемент И, элемент задержки, триггер режима, а также группы регистров, элементов задерх ки, элементов И и ждущих мультивибраторов, входы которых соединены соответственное

5 третьими входами таймера, а выходы - с первыми входами элементов И, вторые входы которых подключены к выходам соответствующих регистров, а одноименные разряды выходов элементов И соединены с входами соответствующих элементов ИЛИ,

выходы которых подключены к входу дешифратора в соответствии с номерами разрядов на входах элементов ИЛИ, при этом вторые входы таймера соединены с соответствующими входами сброса регистров и через элементы задержки с входами записи регистров, информационные входы которых соединены между собой и с шестым входом таймера, четвертый вход которого соединен с первым входом элемента И и синхровхо- дами D-триггеров, выходы которых соедине- ны с информационными входами последующих D-триггеров, за исключением последнего, а их входы сброса, за исключением последнего, соединены между собой, с пятым входом таймера и входом установки триггера режима, вход сброса которого сое0

5

динен с первым входом таймера, а выход - с вторым входом элемента И, выход которого соединен с входом первого элемента ИЛИ, выход которого подключен к выходу таймера, а второй вход соединен с выходом последнего D-триггера и через элемент задержки подключен к первому входу второго элемента ИЛИ, выход которого соединен с входом сброса последнего D-триггера, а второй вход - с пятым входом таймера, при этом разряды выхода дешифратора в порядке убывания номеров подключены к входам установки D-триггеров, кроме последнего, так что старший разряд выхода подключен к входу установки первого D-триггера. а младший - к входу установки предпоследнего D-триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный коммутатор | 1988 |

|

SU1541764A1 |

| МОДУЛЬ ДЛЯ РЕТРАНСЛЯЦИИ СООБЩЕНИЙ В КОММУТАЦИОННОЙ СТРУКТУРЕ | 2002 |

|

RU2222044C2 |

| Многоканальный коммутатор | 1991 |

|

SU1780182A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1989 |

|

SU1781684A1 |

| Адаптивный многоканальный коммутатор | 1990 |

|

SU1800606A1 |

| Многоканальное устройство для программного управления технологическими процессами | 1986 |

|

SU1361509A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1998 |

|

RU2144267C1 |

| СИСТЕМА РАДИОСВЯЗИ С ПОДВИЖНЫМИ ОБЪЕКТАМИ | 2001 |

|

RU2195774C2 |

| ИМИТАТОР ИСТОЧНИКОВ РАДИОСИГНАЛОВ | 1994 |

|

RU2094915C1 |

Изобретение относится к радиоэлектронике, в частности к электронной коммутационной технике. Цель изобретения - упрощение конструкции и повышение надежности за счет устранения возможности возникновения неоднозначности в работе коммутатора. Многоканальный коммутатор содержит блок 1 формирования адреса канала, таймер 2, распределитель 3 импульсов, блок 4 управления, ключевой элемент 5, источник тока 6, информационную магистраль 7, шины 8 питания, а также в каждом канале 11.1 - 11.N D-триггер 14, первый и второй ключевые элементы 12 и 13 и источник 15 информации. Выход таймера 2 подключен к синхронизирующим входам D-триггеров 14 каналов 11.1 - 11.N, а один из входов - к выходу генератора 10 тактовых импульсов. Таймер 2 содержит регистры по числу каналов и в соответствии с кодами, записаными в них, осуществляет задержку поступления очередного тактового импульса генератора 10 на синхронизирующие входы D-триггеров 14. Благодаря этому может изменяться длительность опроса источников 15 информации. 1 з.п. ф-лы, 3 ил.

HI 21.2

ААЈ/:

ш7| Гш| Гш|

t J I I -hi

L.

7

i

/7 фМ.З

| Многоканальный коммутатор | 1982 |

|

SU1051713A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Многоканальный коммутатор | 1988 |

|

SU1541764A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-07-07—Публикация

1989-08-07—Подача