Изобретение относится к вычислительной технике, в частности к микропроцессорам, осуществляюпщм обработку цифровой информации.

Цель изобретения - повышение производительности микропроцессора.

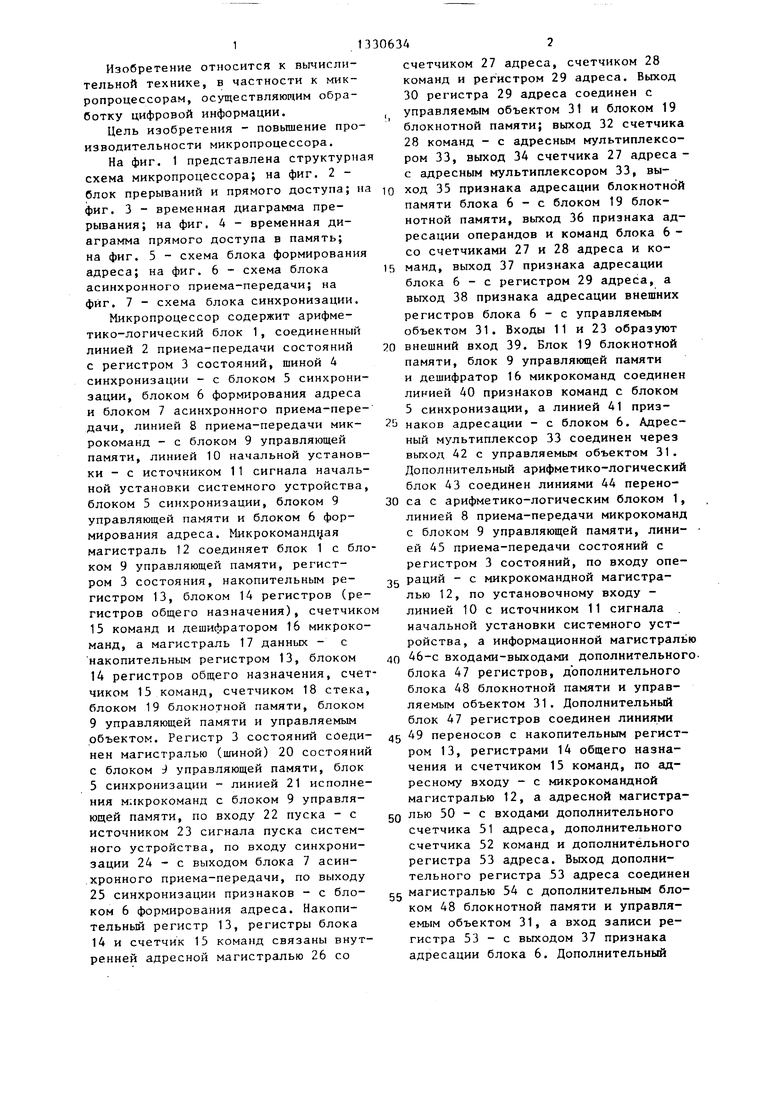

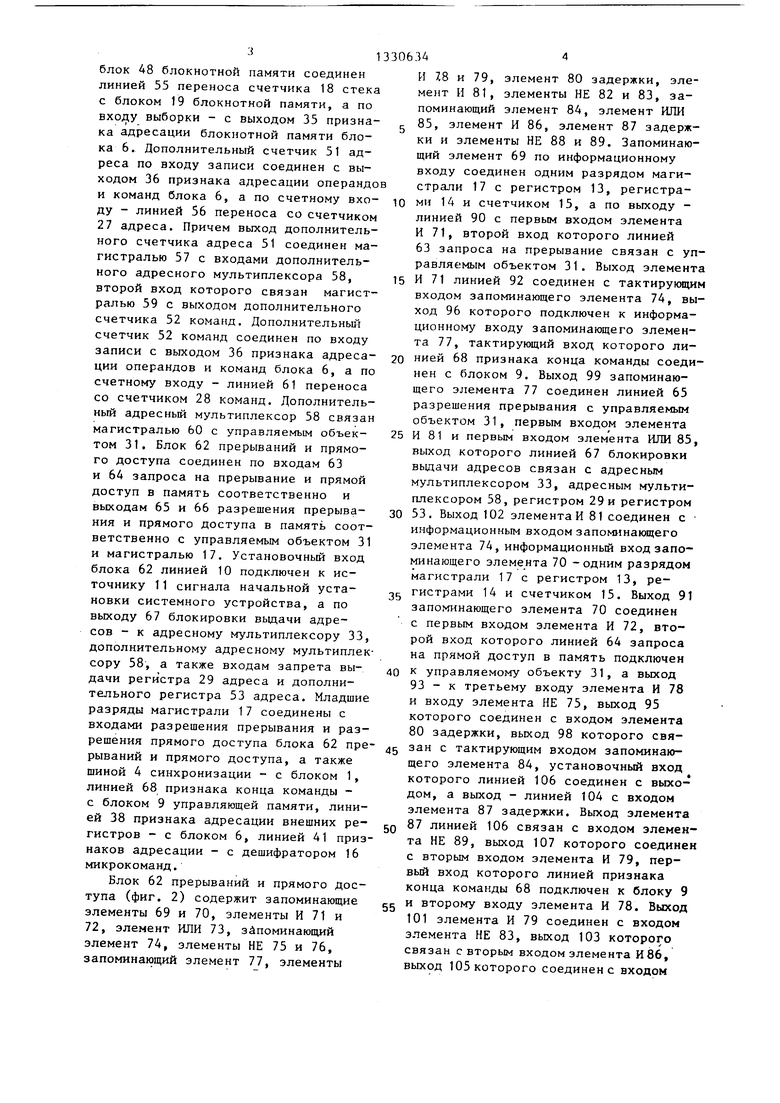

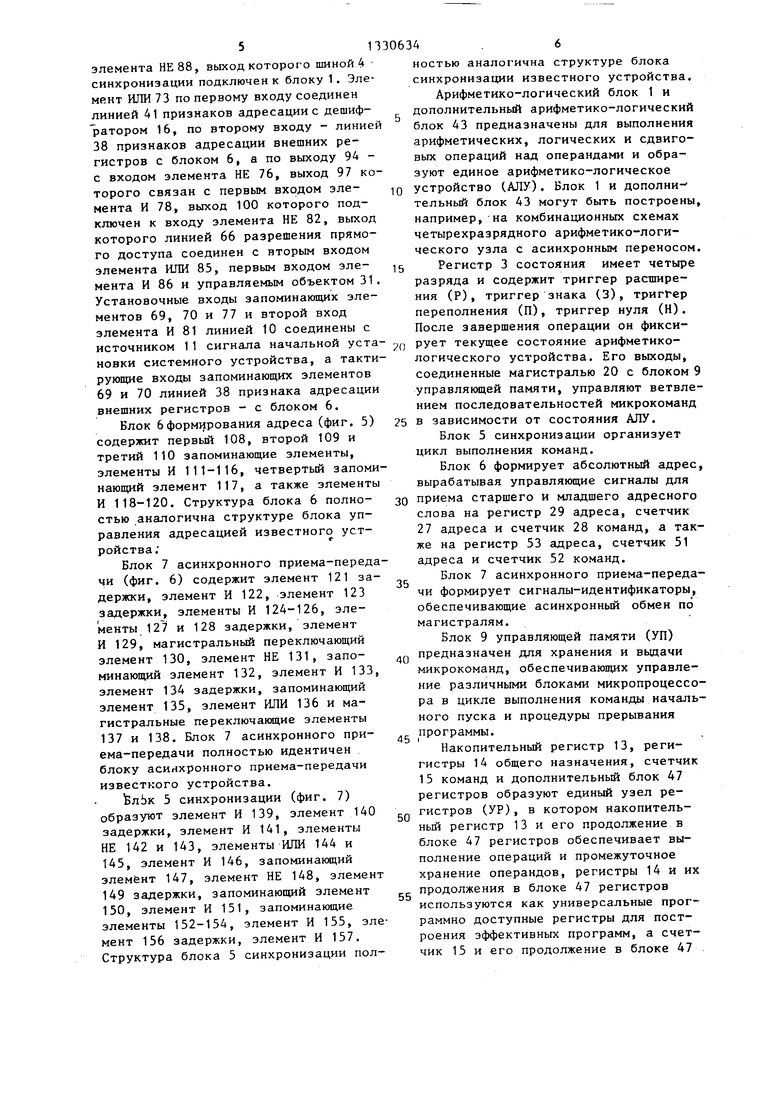

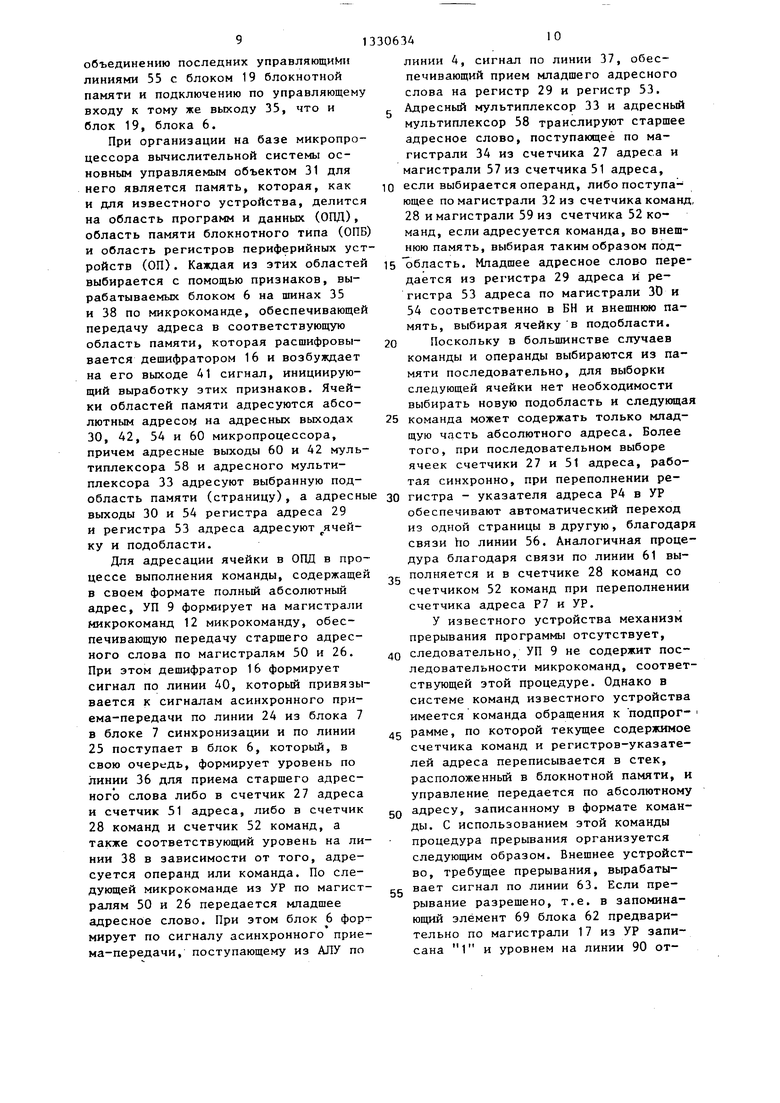

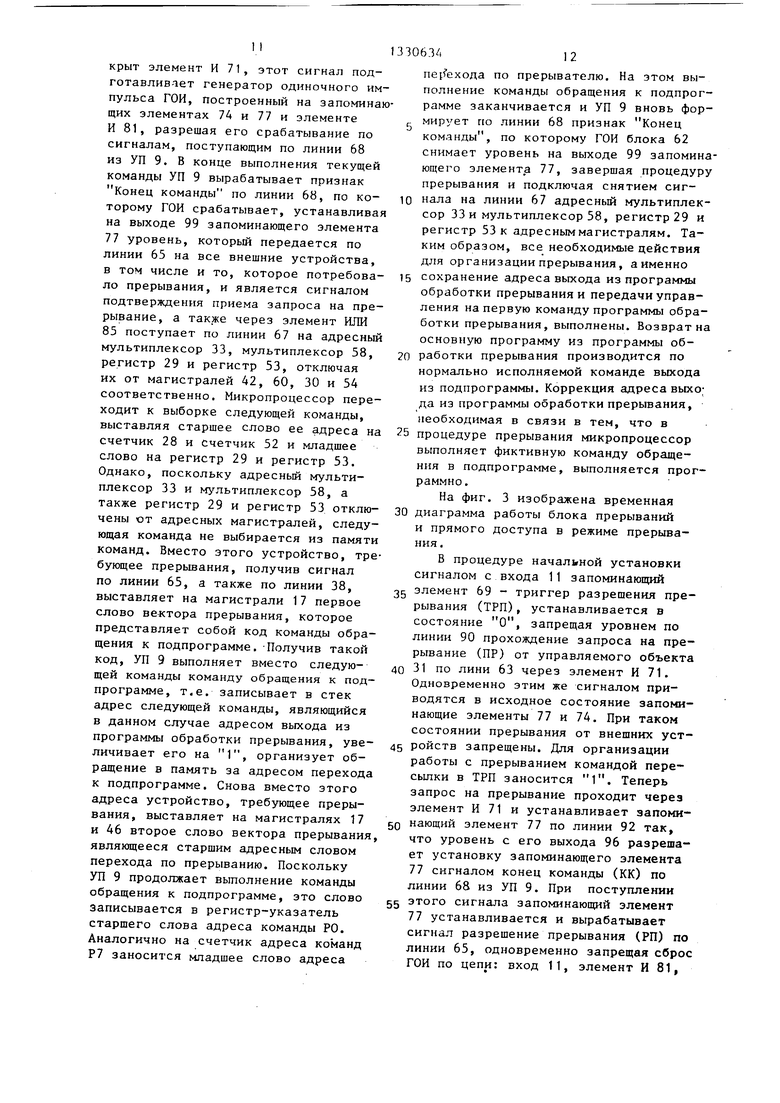

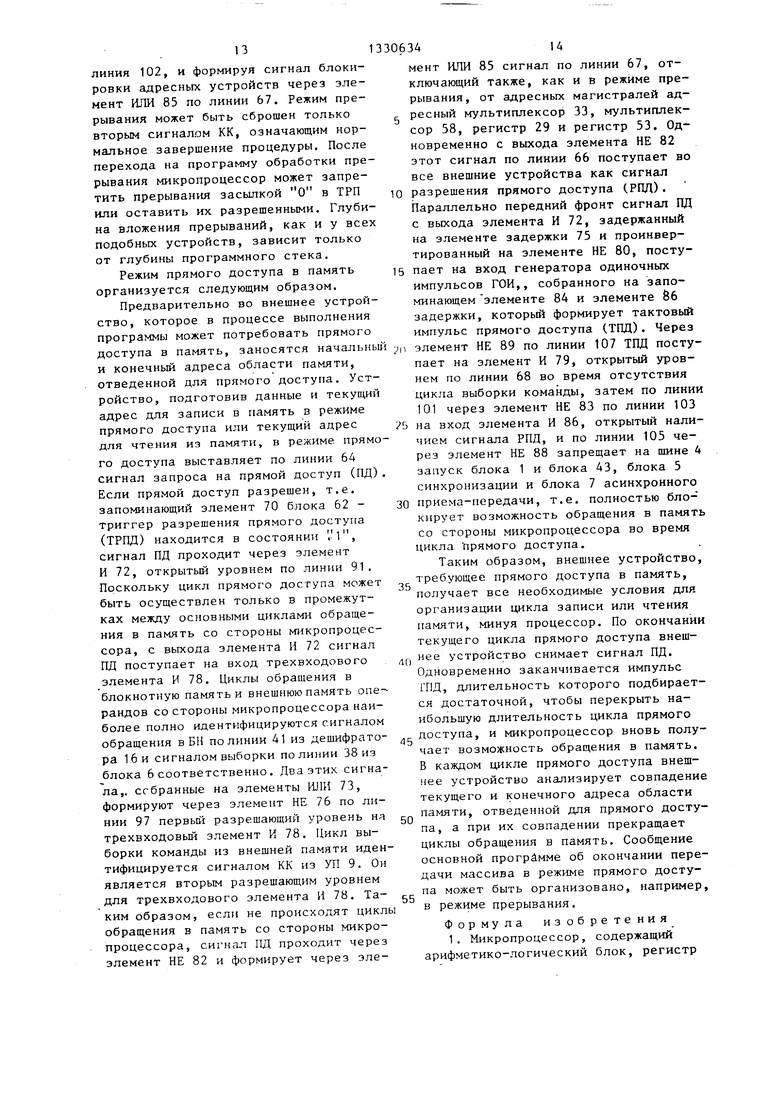

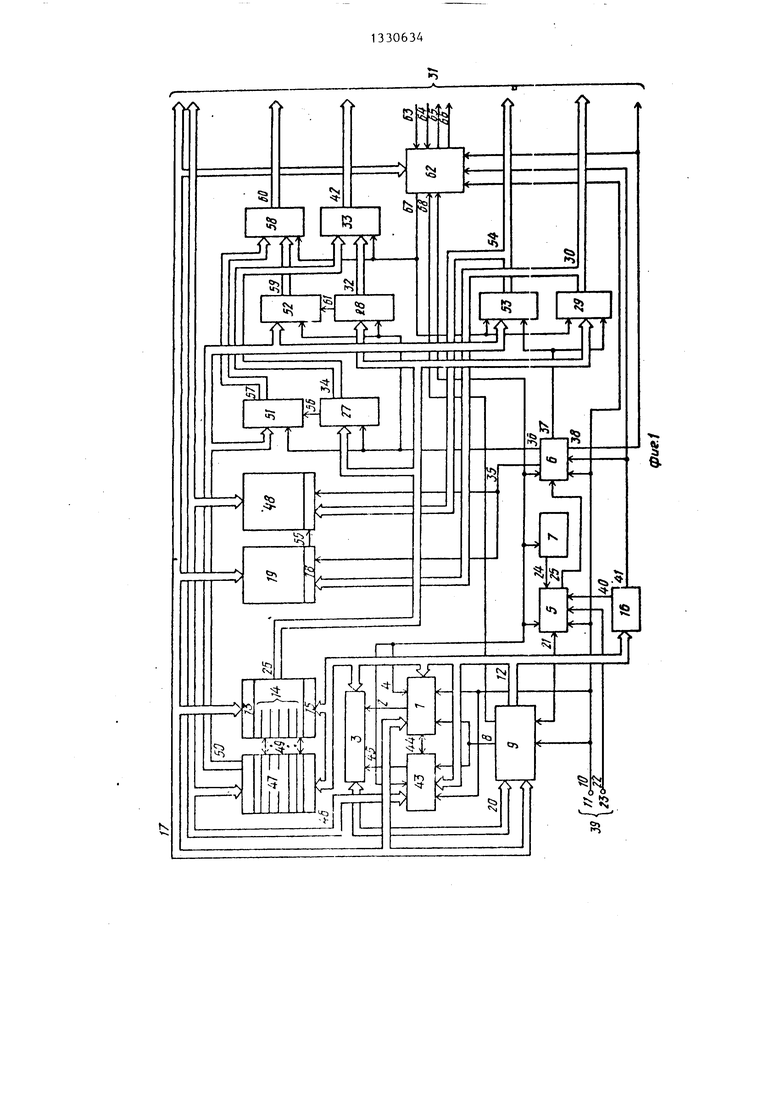

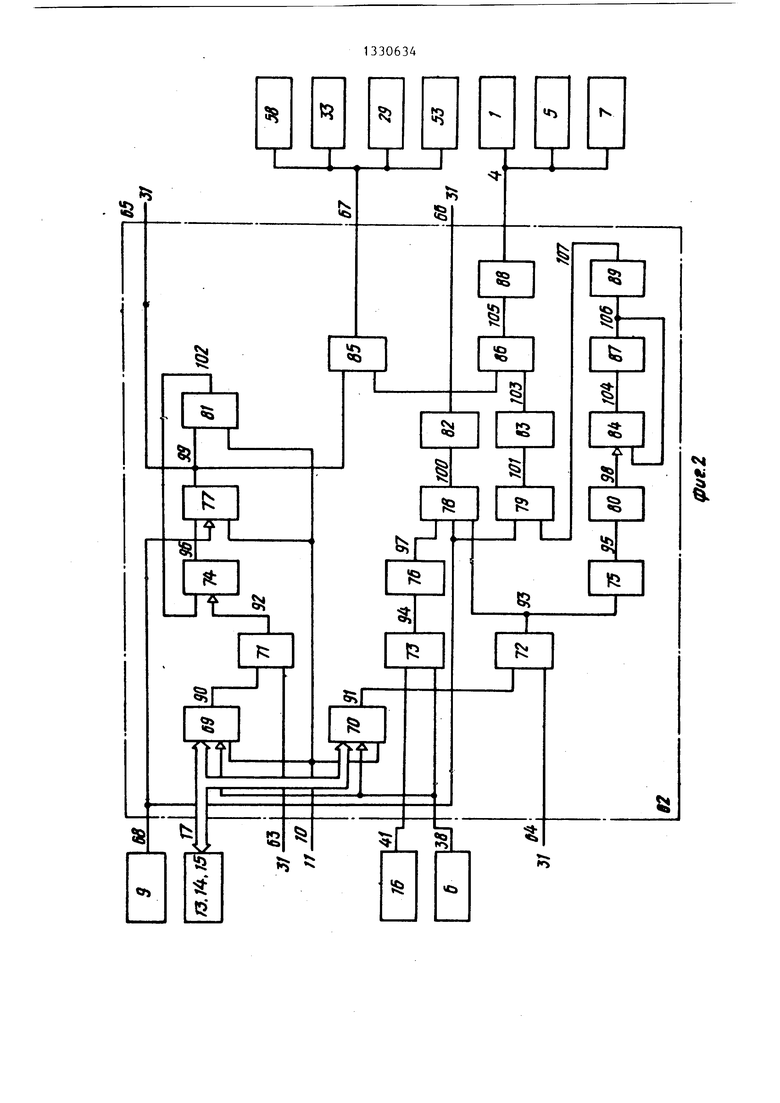

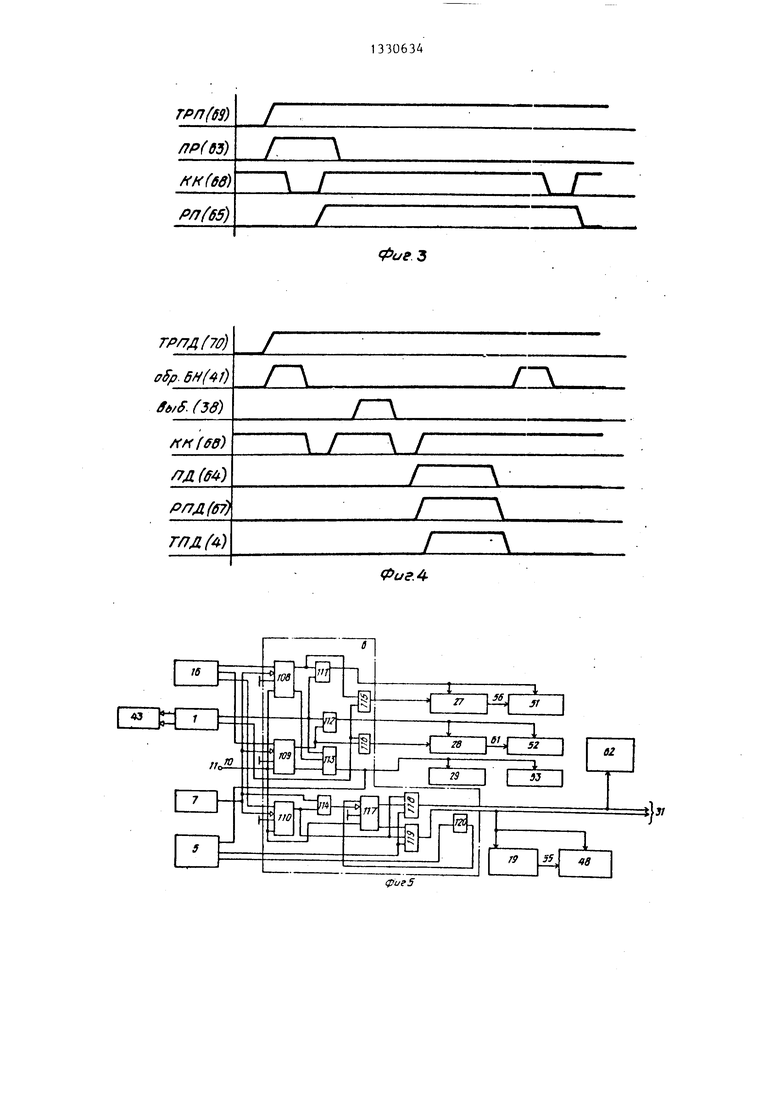

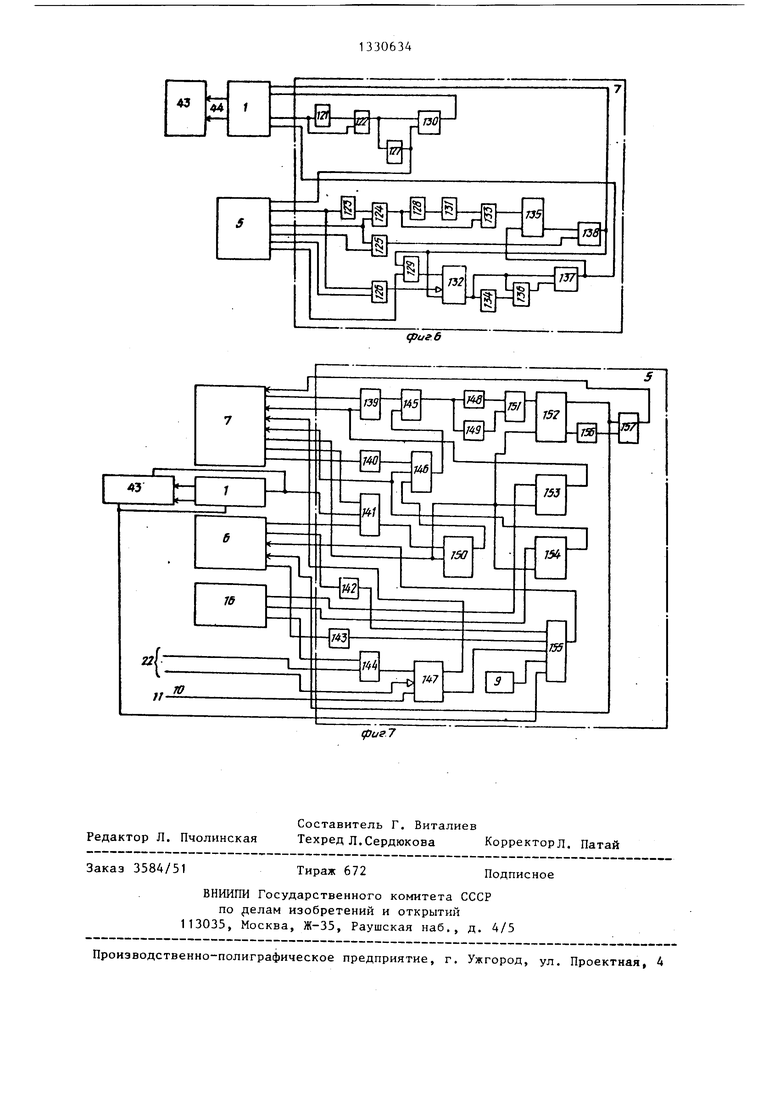

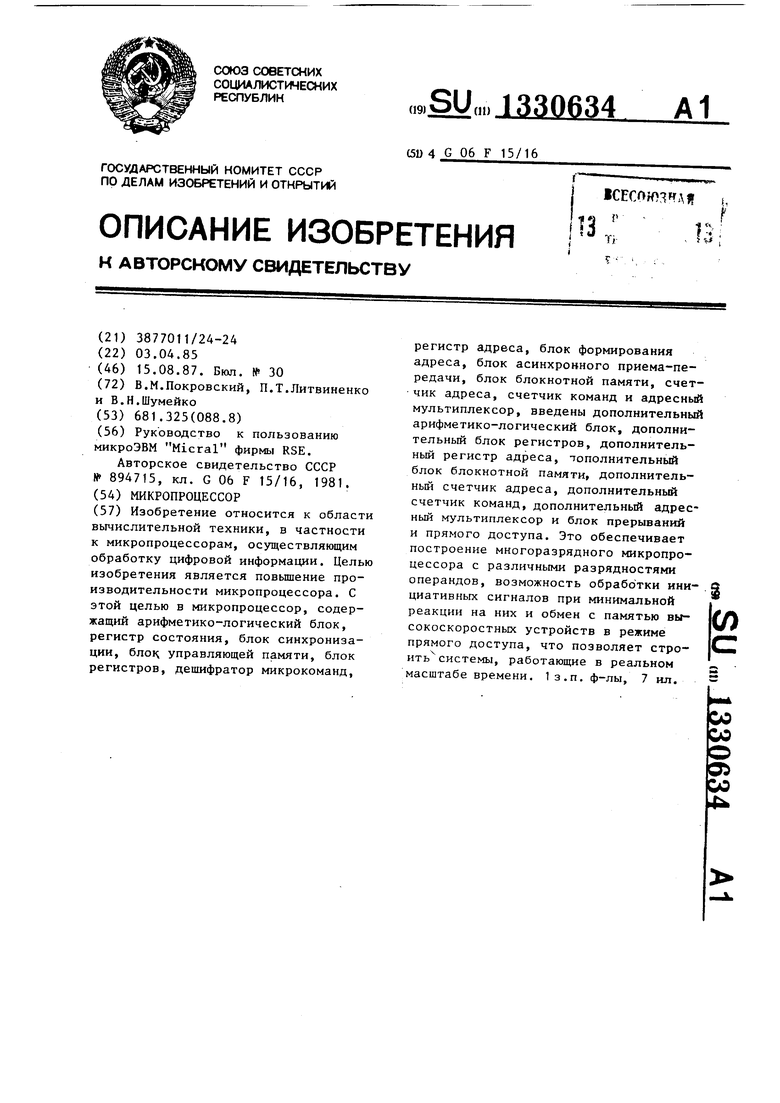

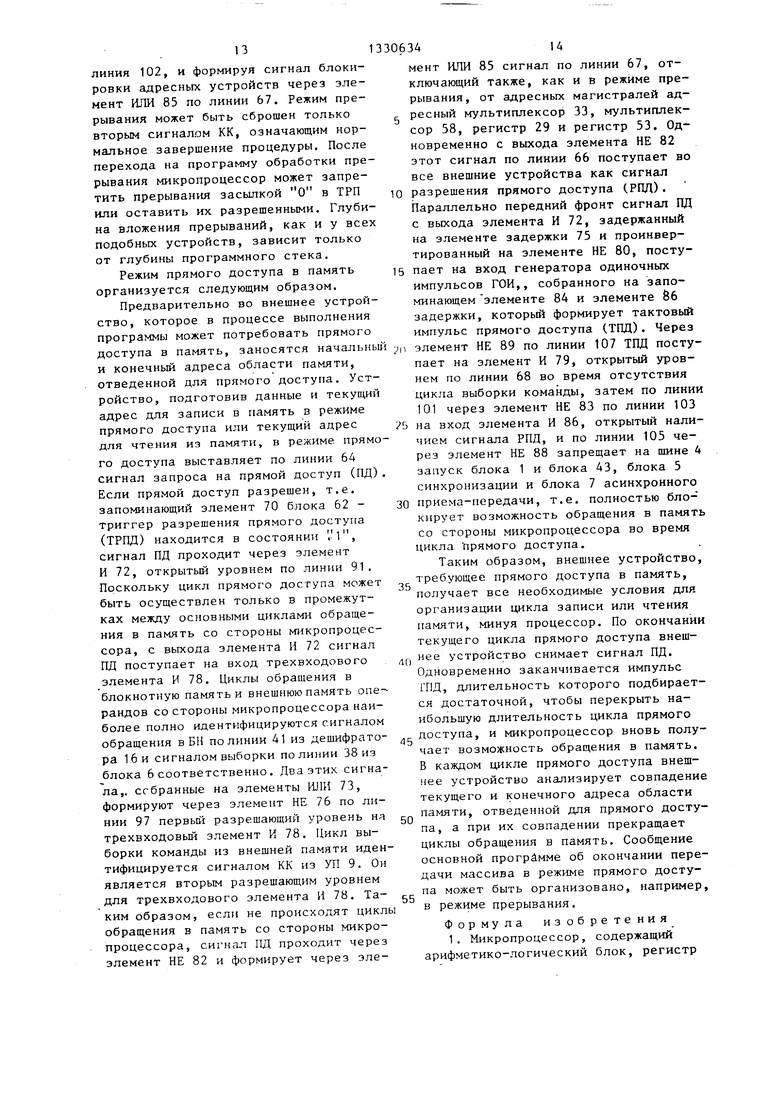

На фиг. 1 представлена структурна схема микропроцессора; на фиг. 2 - блок прерываний и прямого доступа; н фиг. 3 - временная диаграмма прерывания; на фиг. 4 - временная диаграмма прямого доступа в память; на фиг. 5 - схема блока формирования адреса; на фиг. 6 - схема блока асинхронного приема-передачи; на фиг. 7 - схема блока синхронизации.

Микропроцессор содержит арифметико-логический блок 1, соединенный линией 2 приема-передачи состояний с регистром 3 состояний, шиной 4 синхронизации - с блоком 5 синхронизации, блоком 6 формирования адреса и блоком 7 асинхронного приема-передачи, линией 8 приема-передачи микрокоманд - с блоком 9 управляющей памяти, линией 10 начальной установки - с источником 11 сигнала начальной установки системного устройства, блоком 5 синхронизации, блоком 9 управляющей памяти и блоком 6 формирования адреса. Микрокомандцая магистраль 12 соединяет блок 1 с блоком 9 управляющей памяти, регистром 3 состояния, накопительным регистром 13, блоком 14 регистров (регистров общего назначения), счетчико 15 команд и дешифратором 16 микрокоманд, а магистраль 17 данных - с накопительным регистром 13, блоком 14 регистров общего назначения, счетчиком 15 команд, счетчиком 18 стека, блоком 19 блокнотной памяти, блоком 9 управляющей памяти и управляемым объектом. Регистр 3 состояний соединен магистралью (шиной) 20 состояний с блоком 9 управляющей памяти, блок 5 синхронизации - линией 21 исполнения микрокоманд с блоком 9 управляющей памяти, по входу 22 пуска - с источником 23 сигнала пуска системного устройства, по входу синхронизации 24 - с выходом блока 7 асинхронного приема-передачи, по выходу 25 синхронизации признаков - с блоком 6 формирования адреса. Накопительный регистр 13, регистры блока 14 и счетчик 13 команд связаны внутренней адресной магистралью 26 со

счетчиком 27 адреса, счетчиком 28 команд и регистром 29 адреса. Выход 30 регистра 29 адреса соединен с

, управляемым объектом 31 и блоком 19 блокнотной памяти; выход 32 счетчика 28 команд - с адресньм мультиплексором 33, выход 34 счетчика 27 адреса с адресным мультиплексором 33, вы10 ход 35 признака адресации блокнотной памяти блока 6 - с блоком 19 блокнотной памяти, выход 36 признака адресации операндов и команд блока 6 - со счетчиками 27 и 28 адреса и ко15 манд, выход 37 признака адресации блока 6 - с регистром 29 адреса, а выход 38 признака адресации внешних регистров блока 6 - с управляемым объектом 31. Входы 11 и 23 образуют

20 внешний вход 39. Блок 19 блокнотной памяти, блок 9 управляющей памяти и дешифратор 16 микрокоманд соединен линией 40 признаков команд с блоком 5 синхронизации, а линией 41 приз2 3 наков адресации - с блоком 6. Адресный мультиплексор 33 соединен через выход 42 с управляемым объектом 31. Дополнительный арифметико-логический блок 43 соединен линиями 44 перено30 са с арифметико-логическим блоком 1, линией 8 приема-передачи микрокоманд с блоком 9 управляющей памяти, лини- ей 45 приема-передачи состояний с регистром 3 состояний, по входу опе35 раций - с микрокомандной магистралью 12, по установочному входу - линией 10 с источником 11 сигнала начальной установки системного уст- ройства, а информационной магистраль

40 46-с входами-выходами дополнительног блока 47 регистров, дополнительного блока 48 блокнотной памяти и управляемым объектом 31. Дополнительный блок 47 регистров соединен линиями

45 переносов с накопительным регистром 13, регистрами 14 общего назначения и счетчиком 15 команд, по адресному входу - с микрокомандной магистралью 12, а адресной магистра5Q лью 50 - с входами дополнительного счетчика 51 адреса, дополнительного счетчика 52 команд и дополнительного регистра 53 адреса. Выход дополнительного регистра 53 адреса соединен

55 магистралью 54 с дополнительным блоком 48 блокнотной памяти и управляемым объектом 31, а вход записи регистра 53 - с выходом 37 признака адресации блока 6. Дополнительный

блок 48 блокнотной памяти соединен линией 55 переноса счетчика 18 стека с блоком 19 блокнотной памяти, а по входу выборки - с выходом 35 признака адресации блокнотной памяти блока 6. Дополнительный счетчик 51 адреса по входу записи соединен с выходом 36 признака адресации операндо и команд блока 6, а по счетному вхо- ду - линией 56 переноса со счетчиком 27 адреса. Причем выход дополнительного счетчика адреса 51 соединен магистралью 57 с входами дополнительного адресного мультиплексора 58, второй вход которого связан магистралью 59 с выходом дополнительного счетчика 52 команд. Дополнительный счетчик 52 команд соединен по входу записи с выходом 36 признака адреса- ции операндов и команд блока 6, а по счетному входу - линией 61 переноса со счетчиком 28 команд. Дополнительный адресный мультиплексор 58 связан магистралью 60 с управляемым объек- том 31. Блок 62 прерываний и прямого доступа соединен по входам 63 и 64 запроса на прерывание и прямой доступ в память соответственно и выходам 65 и 66 разрешения прерыва- ния и прямого доступа в память соответственно с управляемым объектом 31 и магистралью 17. Установочный вход блока 62 линией 10 подключен к источнику 11 сигнала начальной установки системного устройства, а по выходу 67 блокировки выдачи адресов - к адресному мультиплексору 33, дополнительному адресному мультиплексору 58, а также входам запрета вы- дачи регистра 29 адреса и дополнительного регистра 53 адреса. Младшие разряды магистрали 17 соединены с входами разрешения прерывания и разрешения прямого доступа блока 62 пре рываний и прямого доступа, а также шиной 4 синхронизации - с блоком 1, линией 68 признака конца команды - с блоком 9 управляющей памяти, линией 38 признака адресации внешних ре- гистров - с блоком 6, линией 41 признаков адресации - с дешифратором 16 микрокоманд.

Блок 62 прерываний и прямого Доступа (фиг. 2) содержит запоминающие элементы 69 и 70, элементы И 71 и 72, элемент ИЛИ 73, запоминающий элемент 74, элементы НЕ 75 и 76, запоминающий элемент 77, элементы

5 0 5 О Q ,,

5

5

И 7,8 и 79, элемент 80 задержки, элемент И 81, элементы НЕ 82 и 83, запоминающий элемент 84, элемент ИЛИ 85, элемент И 86, элемент 87 задержки и элементы НЕ 88 и 89. Запоминающий элемент 69 по информационному входу соединен одним разрядом магистрали 17 с регистром 13, регистрами 14 и счетчиком 15, а по выходу - линией 90 с первым входом элемента И 71, второй вход которого линией 63 запроса на прерывание связан с управляемым объектом 31. Выход элемента И 71 линией 92 соединен с тактирующим входом запоминающего элемента 74, выход 96 которого подключен к информационному входу запоминающего элемента 77, тактирующий вход которого линией 68 признака конца команды соединен с блоком 9. Выход 99 запоминающего элемента 77 соединен линией 65 разрешения прерывания с управляемым объектом 31, первым входом элемента И 81 и первым входом элемента ИЛИ 85, выход которого линией 67 блокировки вьщачи адресов связан с адресным мультиплексором 33, адресным мультиплексором 58, регистром 29 и регистром 53, Выход 102 элемента И 81 соединен с информационным входом запоминающего элемента 74, информационный вход запоминающего элемента 70 -одним разрядом магистрали 17 с регистром 13, регистрами 14 и счетчиком 15. Выход 91 запоминающего элемента 70 соединен с первым вхадом элемента И 72, второй вход которого линией 64 запроса на прямой доступ в память подключен к управляемому объекту 31, а выход 93 - к третьему входу элемента И 78 и входу элемента НЕ 75, выход 95 которого соединен с входом элемента 80 задержки, выход 98 которого связан с тактирующим входом запоминающего элемента 84, установочный вход которого линией 106 соединен с выходом, а выход - линией 104 с входом элемента 87 задержки. Выход элемента 87 линией 106 связан с входом элемента НЕ 89, выход 107 которого соединен с вторым входом элемента И 79, первый вход которого линией признака конца команды 68 подключен к блоку 9 и второму входу элемента И 78. Выход 101 элемента И 79 соединен с входом элемента НЕ 83, выход 103 которого связан с вторым входом элемента И 86, выход 105 которого соединен с входом

элемента НЕ 88, выход которого шиной 4 синхронизации подключен к блоку 1, Элемент ИЛИ 73 по первому входу соединен линией А1 признаков адресации с дешиф- ратором 16, по второму входу - линие 38 признаков адресации внешних регистров с блоком 6, а по выходу 94 - с входом элемента НЕ 76, выход 97 которого связан с первым входом элемента И 78, выход 100 которого подключен к входу элемента НЕ 82, выход которого линией 66 разрешения прямого доступа соединен с вторым входом элемента ИЛИ 85, первым входом элемента И 86 и управляемым объектом 31 Установочные входы запоминающих элементов 69, 70 и 77 и второй вход элемента И 81 линией 10 соединены с источником 11 сигнала начальной установки системного устройства, а тактирующие входы запоминающих элементов 69 и 70 линией 38 признака адресации внещних регистров - с блоком 6.

Блок 6формирования адреса (фиг. 5) содержит первый 108, второй 109 и третий 110 запоминающие элементы, элементы И 111-116, четвертый запоминающий элемент 117, а также элементы И 118-120. Структура блока 6 полностью аналогична структуре блока управления адресацией известного устройства;

Блок 7 асинхронного приема-передачи (фиг. 6) содержит элемент 121 задержки, элемент И 122, элемент 123 задержки, элементы И 124-126, элементы 127 и 128 задержки, элемент И 129, магистральный переключающий элемент 130, элемент НЕ 131, запоминающий элемент 132, элемент И 133, элемент 134 задержки, запоминающий элемент 135, элемент ИЛИ 136 и магистральные переключающие элементы 137 и 138. Блок 7 асинхронного приема-передачи полностью идентичен блоку асинхронного приема-передачи известного устройства.

ЬлЬк 5 синхронизации (фиг. 7) образуют элемент И 139, элемент 140 задержки, элемент И 141, элементы НЕ 142 и 143, элементы ИЛИ 144 и 145, элемент И 146, запоминающий элемент 147, элемент НЕ 148, элемент 149 задержки, запоминающий элемент 150, элемент И 151, запоминающие элементы 152-154, элемент И 155, элемент 156 задержки, элемент И 157. Структура блока 5 синхронизации пол0

5

5

0

5

0

5 .

ностью аналогична структуре блока синхронизации известного устройства.

Арифметико-логический блок 1 и дополнительньА арифметико-логический блок 43 предназначены для выполнения арифметических, логических и сдвиговых операций над операндами и образуют единое арифметико-логическое устройство (АЛУ). Блок 1 и дополни- тельный блок 43 могут быть построены, например, на комбинационных схемах четырехразрядного арифметико-логического узла с асинхронным переносом.

Регистр 3 состояния имеет четыре разряда и содержит триггер расширения (Р), триггер знака (3), триггер переполнения (П), триггер нуля (Н). После заверщения операции он фиксирует текущее состояние арифметико- логического устройства. Его выходы, соединенные магистралью 20 с блоком 9 управляющей памяти, управляют ветвлением последовательностей микрокоманд в зависимости от состояния АЛУ.

Блок 5 синхронизации организует цикл выполнения команд.

Блок 6 формирует абсолютный адрес, вырабатывая управляющие сигналы для приема старшего и младшего адресного слова на регистр 29 адреса, счетчик 27 адреса и счетчик 28 команд, а также на регистр 53 адреса, счетчик 51 адреса и счетчик 52 команд.

Блок 7 асинхронного приема-передачи формирует сигналы-идентификаторы, обеспечивающие асинхронный обмен по магистралям.

Блок 9 управляющей памяти (УП) предназначен для хранения и вьщачи микрокоманд, обеспечивающих управление различными блоками микропроцессора в цикле выполнения команды начального пуска и процедуры прерывания программы.

0

5

Накопительный регистр 13, реги- гистры 14 общего назначения, счетчик 15 команд и дополнительньй блок 47 регистров образуют единый узел регистров (УР), в котором накопительный регистр 13 и его продолжение в блоке 47 регистров обеспечивает выполнение операций и промежуточное хранение операндов, регистры 14 и их продолжения в блоке 47 регистров используются как универсальные программно доступные регистры для построения эффективных программ, а счетчик 15 и его продолжение в блоке 47

формирует младшее слово последовательных адресов команд.

Распределение регистров УР: РО, Р1 и Р2 - регистры общего назначения; РЗ - регистр-указатель старшего слова адреса операнда; Р4 - регистр- указатель младшего слова адреса операнда; Р5 - регистр-указатель стека; Рб - регистр-указатель старшего слова адреса команды; Р7 - счетчик адреса команды.

Дешифратор 16 микрокоманд обеспечивает формирование управляющих сигналов в цикле выполнения микрокоманды.

Счетчик 18 и его продолжение в блоке 48 предназначен для организаци программного стека.

Блок 19 блокнотной памяти и дополнительный блок 48 блокнотной памяти образуют блокнотный накопитель (БН) промежуточных результатов и переменных параметров. Ячейки этого накопителя не адресуются по счетчику команд, поэтому их содержимое не может быть командой.

Счетчик 27 адреса и счетчик 51 адреса хранят старшие разряды абсолютного адреса операнда, счетчик 28 команд и счетчик 52 команд - старшие разряды адреса команды, регистр 29 адреса и регистр 53 адреса - младшиз разряды адресов операндов и команд.

Адресный мультиплексор 33 и мультиплексор 58 передают во внешнюю память старшее адресное слово либо со счетчика команд 28 и счетчика 52 команд соответственно в режиме выборки команды, либо со счетчика адреса 27 и счетчика 51 адреса операнда соответственно в режиме выборки операнда

БЛОК 62 прерываний и прямого достпа по сигналу управляемого объекта 31 по линии 63 блокирует выполнение следующей команды и после завершения текущей команды организует процедуру прерывания программы, а по сигналу от управляемого объекта 31 по линии 61 обеспечивает в промежутках между циклами записи и считывания микропроцессора прямой доступ в память.

Так же, как и в известном устройстве, основные процедуры, выполняемые микропроцессором, организуются микропрограммно.

После начальной установки, осуществляемой сигналом на шине 10, вырабатываемым на линии 39 сигналом

306348

1 1, блоки и узлы микропроцессора устанавливаются в исходное состояние. Сигнал на линии 22 инициирует блок 5 синхронизации так, что на его выходах формируются управляющие сигналы, необходимые для организации цикла начального пуска. При этом УП 9, инициируемая сигналом по линии 10 21, формирует на магистрали 12 последовательность микрокоманд, обеспечивающую установку регистров-указателей адресов и счетчиков команд в состояния, соответствующие передаче 15 управления на нулевую ячейку внешней памяти программы. Таким образом, выполнение программ всегда начинается с нулевой ячейки памяти программ.

0

5

При поступлении команды по магистралям 17 на вход УП 9 на магистрали 12 разворачивается соответствующая ей последовательность микрокоманд, обеспечивающая обработку операндов

5 находящихся в регистрах 14 и их продолжениях в блоке 47 регистров или БН или поступающих из внешней памяти операндов по магистралям 17 и 46. При этом дополнительный блок 43 работает

0 параллельно и синхронно с арифметико-логическим блоком 1, что обеспечивается его подключением по управляющим входам и установочному входу к тем же линиям и магистралям, что и соответствующие управляющие входы блока 1. Связь по линиям 44 переноса и управления с арифметико-логическим блоком 1 обеспечивает обработку операнда в АЛУ как единого целого, а магистрали .17 и 46 образуют единую шину данных микропроцессора.

Блок 47 регистров работает параллельно и синхронно с накопительным регистром 13, регистрами 14 и счетg чиком 15, поскольку его адресный

вход подсоединен к общей микрокомандной магистрали 12, а линии 49 переноса и управления объединяют соответствующие регистры в единое целое.

БН, состоящий из блока 19 блокнотной памяти со счетчиком программного стека 18 и дополнительного блока 48 блокнотной памяти организован так, что хранит операнды, разрядность которых соответствует разрядности АЛУ и УР, а их выборка и вьщача на магистрали 17 и 46 происходит параллельно как в блоке 19 блокнотной памяти, так и. в дополнительном блоке 48 благодаря

0

0

5

объединению последних управляющими линиями 55 с блоком 19 блокнотной памяти и подключению по управляющему входу к тому же выходу 35, что и блок 19, блока 6.

При организации на базе микропроцессора вычислительной системы основным управляемым объектом 31 для него является память, которая, как и для известного устройства, делится на область программ и данных (ОПД), область памяти блокнотного типа (ОПБ и область регистров периферийных устройств (ОП). Каждая из этих областей выбирается с помощью признаков, вырабатываемых блоком 6 на шинах 35 и 38 по микрокоманде, обеспечивающей передачу адреса в соответствующую область памяти, которая расшифровывается дешифратором 16 и возбуждает на его выходе А1 сигнал, инициирующий выработку этих признаков. Ячейки областей памяти адресуются абсолютным адресом на адресных выходах 30, 42, 54 и 60 микропроцессора, причем адресные выходы 60 и 42 мультиплексора 58 и адресного мультиплексора 33 адресуют выбранную подобласть памяти (страницу), а адресны выходы 30 и 54 регистра адреса 29 и регистра 53 адреса адресуют ячейку и подобласти.

Для адресации ячейки в ОПД в процессе выполнения команды, содержащей в своем формате полный абсолютный адрес, УП 9 формирует на магистрали микрокоманд 12 микрокоманду, обеспечивающую передачу старшего адресного слова по магистралям 50 и 26. При этом дешифратор 16 формирует сигнал по линии 40, который привязывается к сигналам асинхронного приема-передачи по линии 24 из блока 7 в блоке 7 синхронизации и по линии 25 поступает в блок 6, который, в свою очередь, формирует уровень по линии 36 для приема старшего адресного слова либо в счетчик 27 адреса и счетчик 51 адреса, либо в счетчик 28 команд и счетчик 52 команд, а также соответствующий уровень на линии 38 в зависимости от того, адресуется операнд или команда. По следующей микрокоманде из УР по магистралям 50 и 26 передается младшее адресное слово. При этом блок 6 фор

мирует по сигналу асинхронного приема-передачи, поступающему из АЛУ по

10

20

25

33063410

линии 4, сигнал по линии 37, обеспечивающий прием младшего адресного слова на регистр 29 и регистр 53. Адресный мультиплексор 33 и адресный мультиплексор 58 транслируют старшее адресное слово, поступающее по магистрали 34 из счетчика 27 адреса и магистрали 57 из счетчика 51 адреса, если выбирается операнд, либо поступа- ющее по магистрали 32 из счетчика команд, 28 и магистрали 59 из счетчика 52 команд, если адресуется команда, во внешнюю память, выбирая таким образом под15 Ъбласть. Младшее адресное слово передается из регистра 29 адреса и регистра 53 адреса по магистрали 3D и 54 соответственно в БН и внешнюю память, выбирая ячейку в подобласти. Поскольку в большинстве случаев команды и операнды выбираются из памяти последовательно, для выборки следующей ячейки нет необходимости выбирать новую подобласть и следующая команда может содержать только млад- щую часть абсолютного адреса. Более того, при последовательном выборе ячеек счетчики 27 и 51 адреса, работая синхронно, при переполнении регистра - указателя адреса Р4 в УР обеспечивают автоматический переход из одной страницы в другую, благодаря связи ho линии 56. Аналогичная процедура благодаря связи по линии 61 выполняется и в счетчике 28 команд со счетчиком 52 команд при переполнении счетчика адреса Р7 и УР.

У известного устройства механизм прерывания программы отсутствует, следовательно, УП 9 не содержит последовательности микрокоманд, соответствующей этой процедуре. Однако в системе команд известного устройства имеется команда обращения к подпрог-

45 рамме, по которой текущее содержимое счетчика команд и регистров-указателей адреса переписывается в стек, расположенный в блокнотной памяти, и управление передается по абсолютному адресу, записанному в формате команды. С использованием этой команды процедура прерывания организуется следующим образом. Внешнее устройство, требущее прерывания, вырабатывает сигнал по линии 63. Если прерывание разрешено, т.е. в запоминающий элемент 69 блока 62 предварительно по магистрали 17 из УР записана 1 и уровнем на линии 90 от30

35

40

50

55

крыт элемент И 71, этот сигнал подготавливает генератор одиночного импульса ГОИ, построенный на запоминащих элементах 74 и 77 и элементе И 81, разрешая его срабатывание по сигналам, поступающим по линии 68 из УП 9. В конце выполнения текущей команды УП 9 вырабатывает признак Конец команды по линии 68, по которому ГОИ срабатывает, устанавлива на выходе 99 запоминающего элемента 77 уровень, который передается по линии 65 на все внешние устройства, в том числе и то, которое потребовало прерывания, и является сигналом подтверждения приема запроса на прерывание, а также через элемент ИЛИ 85 поступает по линии 67 на адресный мультиплексор 33, мультиплексор 58, регистр 29 и регистр 53, отключая их от магистралей 42, 60, 30 и 54 соответственно. Микропроцессор переходит к выборке следующей команды, выставляя старшее слово ее адреса на счетчик 28 и счетчик 52 и младшее слово на регистр 29 и регистр 53. Однако, поскольку адресный мультиплексор 33 и му льтиплексор 58, а также регистр 29 и регистр 53 отключены от адресных магистралей, следующая команда не выбирается из памяти команд. Вместо этого устройство, требующее прерьшания, получив сигнал по линии 65, а также по линии 38, выставляет на магистрали 17 первое слово вектора прерывания, которое представляет собой код команды обращения к подпрограмме.-Получив такой код, УП 9 выполняет вместо следующей команды команду обращения к подпрограмме, т.е. записывает в стек адрес следующей команды, являющийся в данном случае адресом выхода из программы обработки прерывания, увеличивает его на 1, организует обращение в память за адресом перехода к подпрограмме. Снова вместо этого адреса устройство, требующее прерывания, выставляет на магистралях 17 и 46 второе слово вектора прерывания являющееся старшим адресным словом перехода по прерыванию. Поскольку УП 9 продолжает выполнение команды обращения к подпрограмме, это слово Записывается в регистр-указатель старшего слова адреса команды РО. Аналогично на счетчик адреса команд Р7 заносится младшее слово адреса

по прерывателю. На этом выполнение команды обращения к подпрограмме заканчивается и УП 9 вновь формирует по линии 68 признак Конец команды, по которому ГОИ блока 62 снимает уровень на выходе 99 запоминающего элемента 77, завершая процедуру прерывания и подключая снятием сигнала на линии 67 адресный мультиплексор 33 и мультиплексор 58, регистр 29 и регистр 53 к адресныммагистралям. Таким образом, все необходимые действия для организации прерывания, а именно

сохранение адреса выхода из программы обработки прерывания и передачи управления на первую команду программы обработки прерывания, выполнены. Возвратна основную программу из программы обработки прерывания производится по нормально исполняемой команде выхода из подпрограммы. Коррекция адреса выхо; да из программы обработки прерывания, необходимая в связи в тем, что в

процедуре прерывания микропроцессор выполняет фиктивную команду обращения в подпрограмме, выполняется программно.

На фиг. 3 изображена временная

диаграмма работы блока прерываний и прямого доступа в режиме прерывания.

В процедуре начальной установки сигналом с входа 11 запоминающий

элемент 69 - триггер разрешения прерывания (ТРП), устанавливается в состояние О, запрещая уровнем по линии 90 прохождение запроса на прерывание (ПР) от управляемого объекта

31 по лини 63 через элемент И 71. Одновременно этим же сигналом приводятся в исходное состояние запоминающие элементы 77 и 74. При таком состоянии прерывания от внешних устройств запрещены. Для организации работы с прерыванием командой пересылки в ТРП заносится 1, Теперь запрос на прерывание проходит через элемент И 71 и устанавливает эапоминающий элемент 77 по линии 92 так, что уровень с его выхода 96 разрешает установку запоминающего элемента 77 сигналом конец команды (КК) по линии 68 из УП 9. При поступлении

этого сигнала запоминающий элемент 77 устанавливается и вырабатывает сигнал разрешение прерывания (РП) по линии 65, одновременно запрещая сброс ГОИ по цепи: вход 11, элемент И 81,

линия 102, и формируя сигнал блокировки адресных устройств через элемент ИЛИ 85 по линии 67. Режим прерывания может быть сброшен только вторьм сигналом КК, означающим нормальное завершение процедуры. После перехода на программу обработки прерывания микропроцессор может запретить прерывания засылкой О в ТРП или оставить их разрешенными. Глубина вложения прерываний, как и у всех подобных устройств, зависит только от глубины программного стека.

Режим прямого доступа в память организуется следующим образом.

Предварительно во внешнее устройство, которое в процессе выполнения программы может потребовать прямого

доступа в память, заносятся начальньш элемент НЕ 89 по линии 107 ТПД постуи конечньм адреса области памяти, отведенной для прямого доступа. Устройство, подготовив данные и текущий адрес для записи в память в режиме прямого доступа или текущий адрес для чтения из памяти, в режиме прямого доступа выставляет по линии 64 сигнал запроса на прямой доступ (ПД) Если прямой доступ разрешен, т.е. запоминающий элемент 70 блока 62 - триггер разрешения прямого доступа (ТРПД) находится в состоянии ., сигнал ПД проходит через элемент И 72, открытый уровнем по линии 91, Поскольку цикл прямого доступа может быть осуществлен только в промежутках между основными циклами обращения в память со стороны микропроцессора, с выхода элемента И 72 сигнал ПД поступает на вход трехвходового элемента И 78. Циклы обращения в блокнотную память и внешнюю память операндов со стороны микропроцессора наиболее полно идентифицируются сигналом

50

обращения вБН по линии 41 из дешифрато- доступа, и микропроцессор вновь полу- ра 16 и сигналом выборки полиции 38 из блока 6 соответственно. Два этих сигнала,, собранные на элементы ИЛИ 73, формируют через элемент НЕ 76 по линии 97 первьш разрешающий уровень на трехвходовьш элемент И 78. Цикл выборки команды из внешней памяти идентифицируется сигналом КК из УП 9. Он является вторым разрешающим уровнем для трехвходового элемента И 78. Таким образом, если не происходят циклы обращения в память со стороны микропроцессора, сигнал 1Щ проходит через элемент НЕ 82 и формирует через эле55

чает возможность обращения в память. В каждом цикле прямого доступа внешнее устройство анализирует совпадение текущего и конечного адреса области памяти, отведенной для прямого доступа, а при их совпадении прекращает циклы обращения в память. Сообщение основной программе об окончании передачи массива в режиме прямого доступа может быть организовано, например, в режиме прерывания.

Формула изобретения 1. Микропроцессор, содержащий арифметико-логический блок, регистр

мент ИЛИ 85 сигнал по линии 67, отключающий также, как и в режиме прерывания, от адресных магистралей ад- ресный мультиплексор 33, мультиплексор 58, регистр 29 и регистр 53. Одновременно с выхода элемента НЕ 82 этот сигнал по линии 66 поступает во все внешние устройства как сигнал

разрешения прямого доступа (РПД). Параллельно передний фронт сигнал ПД с выхода элемента И 72, задержанный на элементе задержки 75 и проинвер- тированный на элементе НЕ 80, поступает на вход генератора одиночных импульсов ГОИ,, собранного на запоминающем элементе 84 и элементе 8б задержки, который формирует тактовый импульс прямого доступа (ТПД). Через

пает на элемент И 79, открытый уровнем по линии 68 во время отсутствия цикла выборки команды, затем по линии 101 через элемент НЕ 83 по линии 103

на вход элемента И 86, открытый наличием сигнала РПД, и по линии 105 через элемент НЕ 88 запрещает на шине 4 запуск блока 1 и блока 43, блока 5 синхронизации и блока 7 асинхронного

приема-передачи, т.е. полностью бло- кирует возможность обращения в память со стороны микропроцессора во время цикла прямого доступа.

Таким образом, внешнее устройство, требующее прямого доступа в память, получает все необходимые условия для организации цикла записи или чтения памяти, минуя процессор. По окончании текущего цикла прямого доступа внешнее устройство снимает сигнал ПД. Одновременно заканчивается импульс ТПД, длительность которого подбирается достаточной, чтобы перекрыть наибольшую длительность цикла прямого

50

доступа, и микропроцессор вновь полу-

55

чает возможность обращения в память. В каждом цикле прямого доступа внешнее устройство анализирует совпадение текущего и конечного адреса области памяти, отведенной для прямого доступа, а при их совпадении прекращает циклы обращения в память. Сообщение основной программе об окончании передачи массива в режиме прямого доступа может быть организовано, например, в режиме прерывания.

Формула изобретения 1. Микропроцессор, содержащий арифметико-логический блок, регистр

состояния, блок синхронизации, блок управляющей памяти, блок регистров, дешифратор микрокоманд, регистр адреса, блок формирования адреса, блок асинхронного приема-передачи, блок блокнотной памяти, счетчик адреса, счетчик команд и адресный мультиплексор, причем вход-выход признака состояния арифметико-логического блока соединен с входом-выходом приема- передачи регистра состояния, информационный вход которого подключен к информационному входу арифметико- логического блока, вход разрешения приема операции которого соединен с выходом признака вьщачи микрокоманды блока управляющей памяти, выход кода операции которого подключен к входу кода операции арифметико-логического блока, вход синхронизации и выход признака операции которого соединены соответственно с первым тактовым выходом и первым входом задания режима блока синхронизации, второй тактовый выход и второй вход задания режима которого подключены соответственно к входу разрешения обращения и информационному выходу блока управляющей памяти, первый адресный вход которого соединен с шиной данных и является входом-выходом данных микропроцессора, информационный вход-выход арифметико-логического блока подключен к входу-выходу данных микропроцессора, второй адресный вход блока управляющей памяти через шину состояний соединен с информационньм входом-выходом регистра состояния, вход останова блока .синхронизации подключен к первому выходу дешифратора микрокоманд, информационный вход которого соединен с выходом кода операции блока управляющей памяти, информационный вход-выход блока регистров подключен к входу-выходу данных микропроцессора, информационный выход блока регистров соединен с информационным входом регистра адреса, выход которого является выходом адреса внешних регистров микропроцессора, адресный вход блока регистров подключен к выходу кода операции блока управляющей памяти, выход признака адресации блокнотной памяти блока формирования адреса соединен с входом выборки блока блокнотной памяти, адресный вход которого подключен к выходу регистра адреса, вход записи

которого соединен с выходом признака адреса блока формирования адреса, выход признака адресации операндов и команд которого подключен к входу записи счетчика адреса, информацион- . ный вход которого соединен с информационным выходом блока регистров, выход признака адресации внешних регистров блока формирования адреса является управляющим выходом микропроцессора, а вход синхронизации блока формирования адреса подключен к третьему тактовому выходу блока синхронизации,

четвертый тактовый выход которого соединен с входом синхронизации блока асинхронного приема-передачи, вход-выход которого подключен к входу синхронизации блока формирования

адреса, вход синхронизации выдачи

признаков которого соединен с третьим тактовым выходом блока синхронизации, вход пуска которого подключен ко входу пуска микропроцессора, а установочные входы блока управляющей памяти, арифметико-логического блока, блока синхронизации и блока формирования адреса соединены с установочным входом микропроцессора, вход признаков адресации блока формирования адреса подключен к второму выходу дешифратора микрокоманд, информационный вход-выход блока блокнотной памяти соединен с входом-выходом данных

микропроцессора, выход счетчика адреса подключен к первому входу адресного мультиплексора, выход которого является выходом адреса операндов и команд микропроцессора, информационный вход счетчика команд соединен с информационным выходом блока регистров, а вход записи счетчика команд подключен к выходу признака адресации операндов и команд блока формирования адреса, выход счетчика команд соединен с вторым входом адресного мультиплексора, отличающий- с я тем, что, с целью повьппения производительности, он содержит дополнительный арифметико-логический блок, дополнительньш блок регистров, дополнительный регистр адреса, до- полнительньп блок блокнотной памяти, дополнительный счетчик адреса, дополнительный счетчик команд, дополнительный адресный мультиплексор и блок прерываний и прямого доступа, причем вход-выход переноса дополнительного арифметико-логического блока соединен с входом-выходом переноса арифметико-логического блока, выход-выход признака состояния дополнительного арифметико-логического блока чен к второму входу-выходу приема-передачи состояния регистра состояния, вход разрешения приема операции дополнительного арифметико-логического блока соединен с выходом признака выдачи микрокоманд блока управляющей памяти, выход кода операции которого подключен к входу кода операции дополнительного арифметико-логического блока, установочный вход которого соединен с установочным входом микропроцессора, информационный вход-выход дополнительного арифметико-логического блока подключен к информационному входу-выходу дополнительного блока регистров, ИЕ1формационному входу-выходу дополнительного блока блокнотной памяти и япляется вторым входом-выходом данных микропроцессора, вход-выход переноса дополнительного блока регистров соединен с входом- выходом переноса блока регистров, ад- ресньп вход дополнительного блока ре- ристров подключен к выходу кода операции блока управляющей памяти, а информационны выход ; О11олнительного блока регистров соединен с информационными входами дополнительного ре- ристра адреса, дополнительного счетчика адреса и дополнительного счетчика команд, выход дополнительного регистра адреса подключен к адресному входу дополнительного блока блокнотной памяти и является вторьпч выходом адреса внешних регистров микропроцессора, вход записи дополнительного регистра адреса соединен с выходом приз}1ака адреса блока формирования адреса, вход-выход переноса дополнительного блока блокнотной памяти подключен к входу-выходу переноса блока блокнотной памяти, а вход выборки дополнительного блока блокнотной памяти соеинён с выходом признака адресации блокнотной памяти блока формирования адреса, вход записи дополнительного счетчика адреса подключен к вькоду признака адресации операндов и команд блока формирования адреса, счетный ход дополнительного счетчика адреса соединен с вьгходом переноса счетчика адреса, а выход дополнительного счетика адреса подключен к перво,му вхоу дополнительного адресного мульти

5

5

0

5

0

й

0

5

цлексора, второй вход которого соединен с выходом дополнительного счетчика команд, а ,вьп:од дополнительного адресного мультиплексора является вторым вьгходом адреса операндов и команд микропроцессора, вход записи дополнительного счетчика команд подключен к выходу признака адресации операндов и команд блока формирования адреса, счетный вход дополнительного счетчика команд соединен с выходом переноса счетчика команд, вход запроса на прерывания блока прерываний и прямого доступа подключен к входу прерываний микропроцессора, вход запроса на прямой доступ в память блока прерываний и прямого доступа соединен с входом запроса на прямой доступ в память микропроцессора, входы разрещения прерывания и прямого доступа блока прерываний и прямого доступа подключены к информационным входам-выходам арифметико-логического блока, вход признака конца команды блока прерываний и прямого доступа соединен с выходом признак а) конца команды блока управляющей памяти, установочный вход блока прерываний и прямого доступа подключен к установочному входу микропроцессора, пыход блокировки выдачи адресов блока прерываний и прямого доступа соединен с входами запрета выдачи регистра адреса, дополнительного ре- гистра,адреса, адресного мультиплексора и дополнительного адресного мультиплексора, выход разрешения прерьша ния блока прерываний и прямого доступа подключен к вьгходу разрешения прерывания микропроцессора, выход разрешения прямого доступа в память блока прерываний и прямого доступа соединен с вьпсодом разрешения прямого доступа в память микропроцессора, вход признаков адресации блока прерываний и прямого доступа подключен к вьгходу признаков адресации дешифратора микрокоманд, вход занесения разрешений прерывания и прямого доступа блока прерываний и прямого доступа соединен с выходом признака адресации внешних регистров блока формирования адреса, а выход блокировки синхронизации блока прерьшаний ипрямого доступа соединен с входом синхронизации арифме-- тико-логического блока,блока асинхро- ничации приема передачи и первым входом задания режима блока синхронизации.

2. Микропроцессор по п, 1, о т- личающийся тем, что блок прерываний и прямого доступа содержит пять запоминающих элементов, два элемента задержки, шесть элементов И два элемента ИЛИ, шесть элементов НЕ причем информационный вход первого запоминающего элемента соединен с входом разрешения прерывания блока, а выход первого запоминающего элемента подключен к первому входу первого элемента И, второй вход которого соединен с входом запроса прерывания блока, выход первого элемента И под- ключен к тактирующему входу третьего запоминающего элемента, выход которого соединен с информационным входо четвертого запоминающего элемента, тактирующий вход которого подключен к входу признака конца команды блока выход четвертого запоминающего элемента соединен с выходом разрешения прерывания блока, первым входом пятого элемента Ни первым входом второго эле- мента ИЛИ, выход которого подключен к выходу блокировки выдачи адресов блока выход пятого элемента И соединен с информационным входом третьего запоминающего элемента, информационный вход второго запоминающего элемента подключен к входу разрешения прямог доступа блока , а выход второго запоминающего элемента соединен с первым входом второго элемента И, второй вход которого подключен к входу запроса на прямой доступ блока, выход второго элемента И соединен с третьи входом третьего элемента И и входом первого элемента НЕ, выход которого подключен к входу первого элемента задержки, выход которого соединен с

тактирующим входом пятого запоминающего элемента, установочный вход и выход которого подключены соответственно к выходу и входу второго элемента задержки, выход второго элемента задержки соединен с входом шестого элемента НЕ, выход которого подключен к первому входу четвертого элемента И, второй вход которого соединен с входом признака конца команд блока и вторьш входом третьего элеме .та И, выход четвертого элемента И поключен к входу четвертого элемента НЕ выход которого соединен с вторым входом шестого элемента И, выход которого подключен К входу пятого эЛемен та НЕ, выход которого является выходом блокировки синхронизации блока, вход признаков адресации блока . соединен с первым, а вход признака адресации внешних регистров блока - с вторыми входами первого элемента ИЛИ, выход которого подключен к входу второго элемента НЕ, выход которого соединен с первым входом третьего элемента И, выход которого подключен к входу третьего элемента НЕ, выход которого соединен с вторым входом второго элемента ИЛИ, первым входом шестого элемента И и является выходом разрешения прямого доступа блока, установочные входы первого, второго и четвертого запоминающих элементов и второй вход пятого элемента И подключены к установочному входу блока а тактирукщие входы первого и второго запоминающего элементов соединены с входом признака адресации внешних регистров блока.

К

s

А/гЗ

Фие.А

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1979 |

|

SU894715A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

| 8-Битный микропроцессор | 1982 |

|

SU1161950A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для обмена информацией | 1989 |

|

SU1702378A1 |

Изобретение относится к области вычислительной техники, в частности к микропроцессорам, осуществляющим обработку цифровой информации. Целью изобретения является повышение производительности микропроцессора. С этой целью в микропроцессор, содержащий арифметико-логический блок, регистр состояния, блок синхронизации, блок управляющей памяти, блок регистров, дешифратор микрокоманд. регистр адреса, блок формирования адреса, блок асинхронного приема-передачи, блок блокнотной памяти, счет- чик адреса, счетчик команд и адресный мультиплексор, введены дополнительный арифметико-логический блок, дополнительный блок регистров, дополнительный регистр адреса, oпoлнитeльный блок блокнотной памяти, дополнительный счетчик адреса, дополнительный счетчик команд, дополнительный адресный мультиплексор и блок прерываний и прямого доступа. Это обеспечивает построение многоразрядного микропроцессора с различными разрядностями операндов, возможность обработки инициативных сигналов при минимальной реакции на них и обмен с памятью высокоскоростных устройств в режиме прямого доступа, что позволяет строить системы, работающие в реальном масштабе времени. 1 з.п. ф-лы, 7 ил. (Л 00 со о О) со 4

фиг 5

(риг 6

Составитель Г. Виталиев Редактор Л. Пчолинская Техред Л.Сердюкова Корректорл. Патай

Заказ 3584/51

Тираж 672

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, А

Подписное

| Руководство к пользованию микроэвм Micral фирмы RSE | |||

| Микропроцессор | 1979 |

|

SU894715A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-08-15—Публикация

1985-04-03—Подача