Изобретение относится к вычислительной технике и может быть использовано в процессорах цифровых ЭВМ.

Цель изобретения - упрощение комбинационного сумматора на МОП-транзисторах с индикацией моментов окончания переходных процессов.

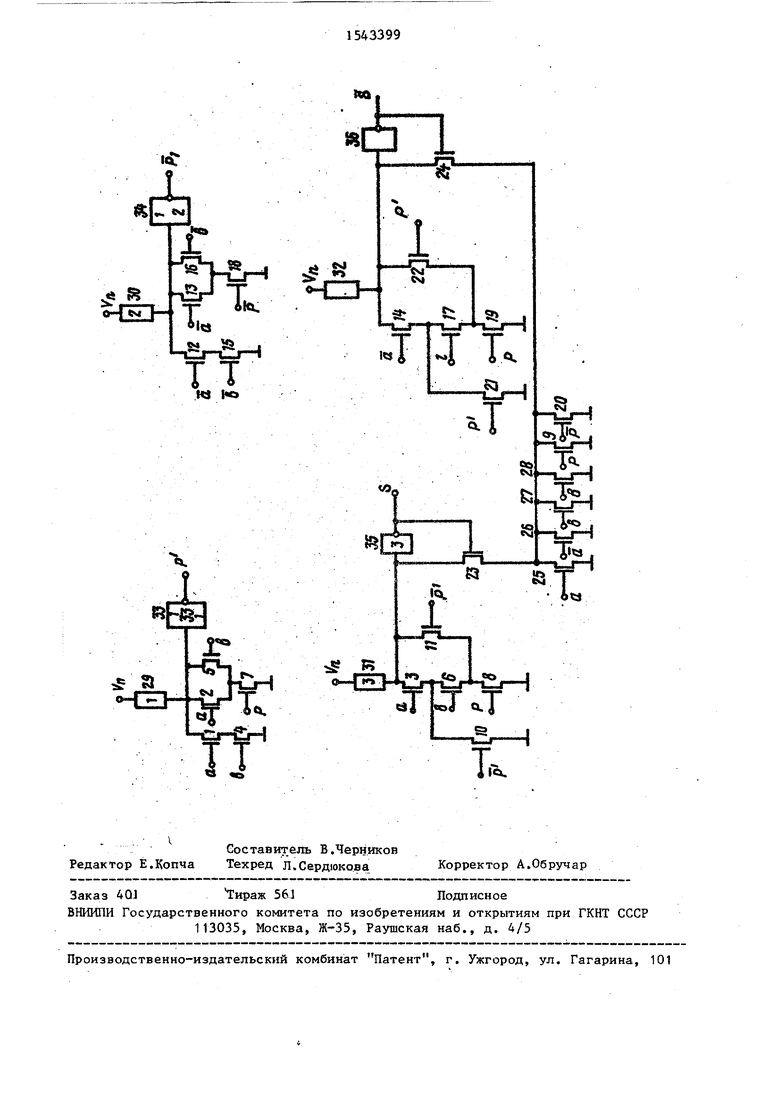

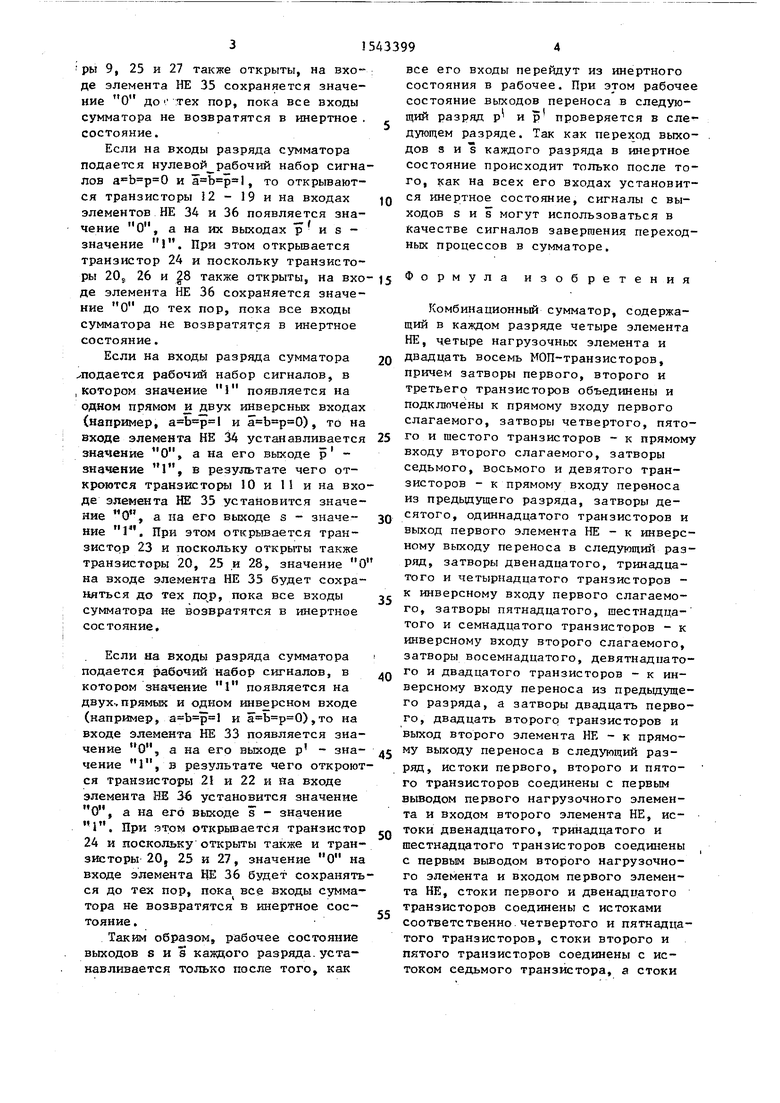

На чертеже представлена схема одного разряда комбинационного сумматора.

Каждый разряд комбинационного сумматора содержит МОП-транзисторы 1 - 28, нагрузочные элементы 29 - 32, элементы НЕ 33 - 36, входы прямых и инверсных значений первого а, а и второго b, b слагаемых и переноса из предыдущего разряда р, р, выходы прямых и инверсных значений суммы данного разряда s, s и переноса в следующий разряд р1, р .

Сумматор работает следующим образом.

В интервалы времени между двумя последовательными суммированиями сумматор находится в инертном состоянии, при котором на входы каждого разряда подается нулевая комбинация входных сигналов: . При этом все транзисторы 1 - 28 закрыты и на выходах устанавливаются нулевые значения р 0.

Если на входы разряда сумматора подается единичный рабочий набор сиг- налов и , то транзисторы 1 - 8 открываются и на входах элементов НЕ устанавливается значение потенциала, соответствующее логическому О, а на их выходах р и s - значение 1. При этом открывается транзистор 23 и поскольку транзистосл

Јь

СО

со

CD

со

ры 9, 25 и 27 также открыты, на входе элемента НЕ 35 сохраняется значение О до1 тех пор, пока все входы сумматора не возвратятся в инертное . состояние.

Если на входы разряда сумматора подается нулевой рабочий набор сигналов и , то открываются транзисторы 12 - 19 и на входах элементов НЕ 34 и 36 появляется значение О, а на их выходах р и s - значение 1. При этом открывается транзистор 24 и поскольку транзисторы 20, 26 и 28 также открыты, на вхо- де элемента НЕ 36 сохраняется значение О до тех пор, пока все входы сумматора не возвратятся в инертное состояние.

Если на входы разряда сумматора подается рабочий набор сигналов, в .котором значение 1 появляется на одном прямом и двух инверсных входах (например, и ), то на входе элемента НЕ 34 устанавливается значение О, а на его выходе р - значение 1, в результате чего откроются транзисторы 10 и 11 и на входе элемента НЕ 35 установится значение И0, а на его выходе s - значе- ние 1. При этом открывается транзистор 23 и поскольку открыты также транзисторы 20, 25 и 28, значение О на входе элемента НЕ 35 будет сохраняться до тех пор, пока все входы сумматора не возвратятся в инертное состояние.

Если на входы разряда сумматора подается рабочий набор сигналов, в котором значение 1 появляется на двух-, прямых и одном инверсном входе (например, и ),то на входе элемента НЕ 33 появляется значение 0й, а на его выходе р - зна- чение 1, в результате чего откроются транзисторы 2 и 22 и на входе элемента НЕ 36 установится значение О, а на его выходе Ґ - значение

1. При этом открывается транзистор 24 и поскольку открыты также и транзисторы 20, 25 и 27, значение О на входе элемента НЕ 36 будет сохраняться до тех пор, пока все входы сумматора не возвратятся в инертное состояние .

Таким образом, рабочее состояние выходов s и а каждого разряда устанавливается только после того, как

5

о

0

5

все его входы перейдут из инертного состояния в рабочее. При этом рабочее состояние выходов переноса в следующий разряд р и р проверяется в следующем разряде. Так как переход выходов s и 1з каждого разряда в инертное состояние происходит только после того, как на всех его входах установится инертное состояние, сигналы с выходов s и Ш могут использоваться в качестве сигналов завершения переходных процессов в сумматоре.

Формула изобретения

Комбинационный сумматор, содержащий в каждом разряде четыре элемента НЕ, четыре нагрузочных элемента и двадцать восемь МОП-транзисторов, причем затворы первого, второго и третьего транзисторов объединены и подключены к прямому входу первого слагаемого, затворы четвертого, пятого и шестого транзисторов - к прямому входу второго слагаемого, затворы седьмого, восьмого и девятого транзисторов - к прямому входу переноса из предыдущего разряда, затворы десятого, одиннадцатого транзисторов и выход первого элемента НЕ - к инверсному выходу переноса в следующий разряд, затворы двенадцатого, тринадцатого и четырнадцатого транзисторов - к инверсному входу первого слагаемого, затворы пятнадцатого, шестнадцатого и семнадцатого транзисторов - к инверсному входу второго слагаемого, затворы восемнадцатого, девятнадцатого и двадцатого транзисторов - к инверсному входу переноса из предыдущего разряда, а затворы двадцать первого, двадцать второго транзисторов и выход второго элемента НЕ - к прямому выходу переноса в следующий разряд, истоки первого, второго и пятого транзисторов соединены с первым выводом первого нагрузочного элемента и входом второго элемента НЕ, истоки двенадцатого, тринадцатого и шестнадцатого транзисторов соединены с первым выводом второго нагрузочного элемента и входом первого элемента НЕ, стоки первого и двенадцатого транзисторов соединены с истоками соответственно четвертого и пятнадцатого транзисторов, стоки второго и пятого транзисторов соединены с истоком седьмого транзистора, а стоки

5I

тринадцатого и шестнадцатого транзис торов - с истоком восемнадцатого транзистора, истоки третьего и одиннадцатого транзисторов соединены с первым выводом третьего нагрузочного элемента и входом третьего элемента НЕ, выход которого соединен с прямым выходом суммы данного разряда и затвором двадцать третьего транзистора, истоки четырнадцатого и двадцать вто рого транзисторов соединены с первым выводом четвертого нагрузочного элемента и входом четвертого элемента НЕ, выход которого соединен с инверсным выходом суммы данного разряда и затвором двадцать четвертого транзистора, сток третьего транзистора соединен с истоками шестого и десятого транзисторов, а исток восьмого транзистора - со стоками шестого и одиннадцатого транзисторов, сток четырнадцатого транзистора соединен с истоками семнадцатого и двадцать первого транзисторов, а исток девятнадцатого транзистора - со стоками семнадцатого и двадцать второго транзисто433996

ров, вторые выводы нагрузочных элементов подключены к шине питания сумматора, а стоки четвертого, девятого, пятнадцатого и двадцатого транзисторов - к его общей шине, отличающийся тем, что, с целью упрощения, в каждом его разряде прямые и инверсные входы первого к вто-

1Q рого слагаемых подключены к затворам соответственно двадцать пятого, двадцать шестого, двадцать седьмого и двадцать восьмого транзисторов, истоки которых соединены между собой и с

15 истоками девятого, двадцатого, двадцать третьего и двадцать четвертого транзисторов, стоки седьмого, восьмого, десятого, восемнадцатого, девятнадцатого, двадцать первого, двадцать 2о пятого, двадцать шестого, двадцать седьмого и двадцать восьмого транзисторов объединены и подключены к общей шине сумматора, стоки двадцать третьего и двадцать четвертого транзис- 25 торов соединены с входами соответственно третьего и четвертого элементов НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Комбинационный сумматор | 1988 |

|

SU1527630A1 |

| Комбинационный сумматор | 1987 |

|

SU1411737A1 |

| Комбинационный сумматор | 1988 |

|

SU1596321A1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 2009 |

|

RU2408922C1 |

| СУММАТОР | 2008 |

|

RU2380739C1 |

| ПОЛНЫЙ СУММАТОР | 2011 |

|

RU2475811C1 |

| СУММАТОР | 2011 |

|

RU2469381C1 |

| СУММАТОР | 2010 |

|

RU2435196C1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 2009 |

|

RU2408058C2 |

| СУММАТОР | 2011 |

|

RU2455680C1 |

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ. Цель изобретения - упрощение комбинационного сумматора на МОП-транзисторах с индикацией моментов окончания переходных процессов. Комбинационный сумматор содержит в каждом разряде двадцать восемь МОП-транзисторов, четыре нагрузочных элемента и четыре элемента НЕ. Сигналы на парафазных выходах суммы сумматора используются для индикации моментов окончания переходных процессов. 1 ил.

| Комбинационный сумматор | 1987 |

|

SU1411737A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Комбинационный сумматор | 1987 |

|

SU1465881A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-15—Публикация

1987-11-17—Подача