(Л

с

28

| название | год | авторы | номер документа |

|---|---|---|---|

| Комбинационный сумматор | 1987 |

|

SU1543399A1 |

| Комбинационный сумматор | 1988 |

|

SU1527630A1 |

| Комбинационный сумматор | 1987 |

|

SU1411737A1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 2009 |

|

RU2408922C1 |

| СУММАТОР | 2008 |

|

RU2380739C1 |

| ТРЁХВХОДОВОЙ КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ | 2020 |

|

RU2761172C1 |

| СУММАТОР | 2010 |

|

RU2435196C1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 2011 |

|

RU2450324C1 |

| СУММАТОР НА КМДП ТРАНЗИСТОРАХ | 2001 |

|

RU2185655C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ВОССТАНОВЛЕНИЯ МОДИФИЦИРОВАННОГО КОДА ХЕММИНГА ДЛЯ 32-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ | 2023 |

|

RU2800768C1 |

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ. Целью изобретения является уменьшение мощности, потребляемой сумматором. Сумматор содержит в каждом разряде МОП-транзисторы N-типа 1-18 и P-типа 19-26, элементы НЕ 27,28, малосигнальные элементы НЕ 29,30 и позволяет осуществлять индикацию моментов окончания переходных процессов. 1 ил.

Wjd

а 2

ел о

W 4D

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ.

Цель изобретения - уменьшение мощности, потребляемой сумматором.

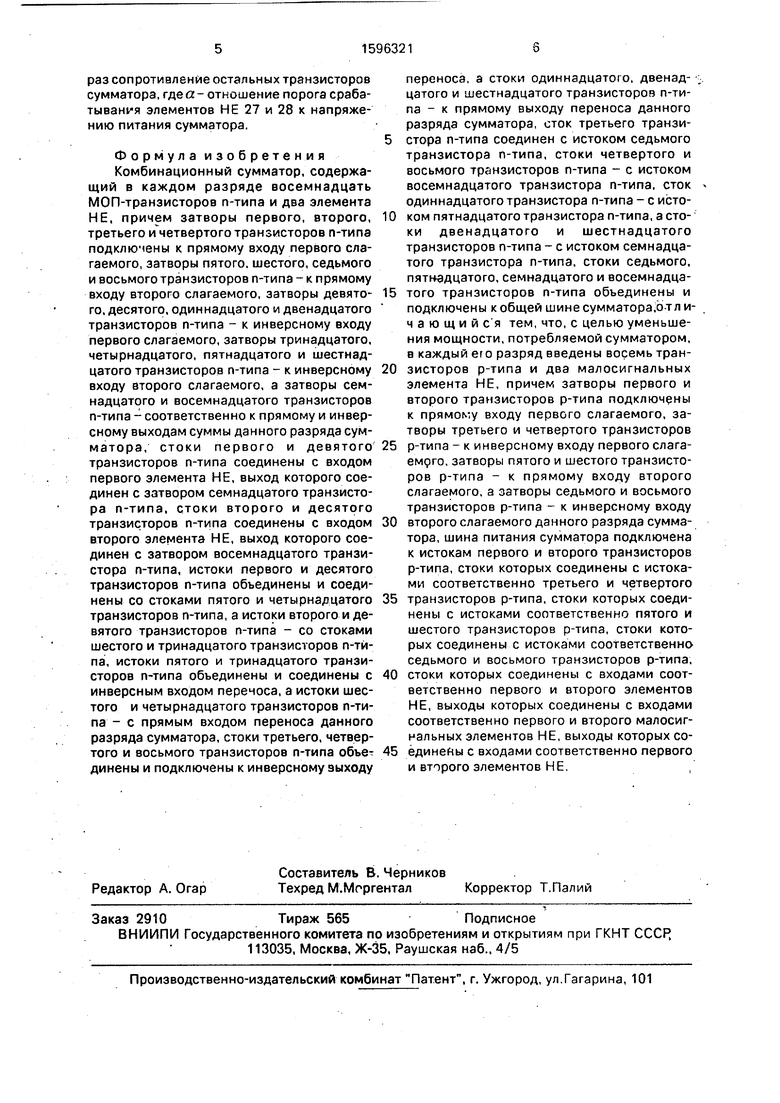

На чертеже представлена схема разряда комбинационного сумматора.

Каждый разряд комбинационного сумматора содержит МОП-транзисторы 1-18 птипа и МОП-транзисторы 19-26 р-типа, элементы НЕ 27 и 28 и малосигнальные элементы НЕ 29 и 30, имеет прямые и инверсные входы первого а, а и второго Ь, Ь слагаемых, переноса р. р, прямые и инверсные выходы суммы S, S и переноса р , р .

CyMN-aTop работает следующим образом.

При подаче на все входы слагаемых напряжения, соответствующего значению логического нуля () закрываются все транзисторы 1-18 п-типа и открываются все транзисторы 19-26 р-типа. При этом схема переходит в инертное состояние, которое характеризуется значением логического нуля на обоих выходах суммы () и высокоимпедансным состоянием выходов переноса.

Если на входах сумматора начать устанавливать рабочий набор сигналов (, b/b), то при появлении логической единицы на одном из входов слагаемых закрывается соответствующая пара транзисторов р-типа, отключая входы элементов НЕ 27 и 28 от шины питания. Однако единичный потенциал на входах элементов НЕ 27 и 28 сохраняется за счет обратных связей через элементы НЕ29.и20дотех пор, пока На всех входах данного разряда сумматора не установится какой-либо рабочий набор сигналов.

После установления на входах сумматора рабочего набора сигналов открываются транзисторы п-типа, на затворы которь1х поданы единичные потенциалы, и нулевой потенциал с одного из входов переноса (р или р) поступает на входопределенного элемента НЕ 27 или 28, где этот потенциал подсаживает выход малосигнального элемента НЕ, подключенного к данному элементу НЕ. В результате на выходе этого элемента НЕ и, следовательно, на соответствующем выходе суммы устанавливается значение логической единицы.

Если на входах сумматора устанавливается единичный рабочий набор сигналов ( ), то нулевой потенциал с общей шины сумматора через открытые транзисторы 3 и 7 поступает на выход р, а с входа р через открытые транзисторы 1 и 5 - на вход элемента НЕ 27. В результате

напряжение на выходе s принимает значение логической единицы.

Если на входах сумматора устанавливается нулевой рабочий набор сигналов

(а Ь р О и р 1), то нулевой потенциал с общей щины сумматора через открытые транзисторы 11 и 15 поступает на выход р , а с входа р через открытые транзисторы 10 и 14 - на вход элемента НЕ 28. В результате

0 напряжение на выходе s принимает значение логической единицы.

Если на входах сумматора устанавливается рабочий набор сигналов, в котором значение 1 имеется на одном прямом и двух

5 инверсных входах (например, и ), то нулевой потенциал с входа р через открытые транзисторы 1 и И поступает на вход элемента НЕ 27. На выходе s появляется значение 1, которое открывает

0 транзистор 17, и нулевой потенциал с общей шины сумматора через транзисторы 17 и 16 проходит на выход р .

Если на входах сумматора устанавливается рабочий набор сигналов,, в котором

5 значение 1 имеется на двух прямых и одном инверсном входах (например, и ), то нулевой потенциал с входа р через открытые транзисторы 2 и 13 поступает на вход элемента НЕ 28. На выходе а

0 появляется значение 1, кото рое открывает транзистор 18, и нулевой потенциал с общей шины сумматора через открытые транзисторы 18 и 4 проходит на выход р.

Благодаря обратной связи через соответствующий малосигнальный элемент НЕ 29 или 30 значение логической единицы, установившееся на одном из выходов суммы в результате подачи рабочего набора входных сигналов, сохраняется до тех пор,

0 пока всё входы сумматора не перейдут в инертное состояние.

После того, как все входы сумматора перейдут в инертное состояние, открываются транзисторы 19-26 р-типа и единичный

5 потенциал поступает на входы элементов НЕ 27 и 28, где он перетягивает выходы малосигнальных элементов НЕ 29 и 30, в результате чего на выходах элементов НЕ 27 и 28, т.е. на выходах s и s, устанавливается

0 значение логического нуля, что свидетельствует о возврате сумматора в инертное состояние. Таким образом, индикация моментов окончания переходных процессов в сумматоре осуществляется по состоянию выходов суммы всех его разрядов и выхода переноса из старшего разряда.

Для обеспечения работоспособности схемы.сопротивление открытых транзисторов р- и п-типа малосигнальных элементов НЕ 29 и 30 должно превышать более чем в 4 а

раз сопротивление остальных транзисторов сумматора, где а- отношение порога срабатывания элементов НЕ 27 и 28 к напряжению питания сумматора.

Формула изобретен и я Комбинационный сумматор, содержащий в каждом разряде восемнадцать МОП-транзисторов п-типа и два элемента НЕ, причем затворы первого, второго, третьего и четвертого транзисторов п-типа подключены к прямому входу первого слагаемого, затворы пятого, шестого, седьмого и восьмого транзисторов п-типа - к прямому входу второго слагаемого, затворы девятого, десятого, одиннадцатого и двенадцатого транзисторов п-типа - к инверсному входу первого слагаемого, затворы тринадцатого, четырнадцатого, пятнадцатого и шестнадцатого транзисторов п-типа - к инверсному входу второго слагаемого, а затворы семнадцатого и восемнадцатого транзисторов п-типа - соответственно к прямому и инверсному выходам суммы данного разряда сумматора, стоки первого и девятого транзисторов п-типа соединены с входом первого элемента НЕ, выход которого соединен с затвором семнадцатого транзистора п-типа, стоки второго и десятого транзисторов п-типа соединены с входом второго элемента НЕ, выход которого соединен с затвором восемнадцатого транзистора п-типа, истоки первого и десятого транзисторов п-типа объединены и соединены со стоками пятого и четырнадцатого транзисторов п-типа, а истоки второго и девятого транзисторов п-типа - со стоками шестого и тринадцатого транзисторов п-тйпа, истоки пятого и тринадцатого транзисторов п-типа объединены и соединены с инверсным входом переноса, а истоки шестого и четырнадцатого транзисторов п-типа - с прямым входом переноса данного разряда сумматора, стоки третьего, четвертого и восьмого транзисторов п-типа объе динены и подключены к инверсному выходу

переноса, а стоки одиннадцатого, двенад- ; цатого и шестнадцатого транзисторов п-типа - к прямому выходу переноса данного разряда сумматора, сток третьего транзистора п-типа соединен с истоком седьмого транзистора п-типа, стоки четвертого и восьмого транзисторов п-типа - с истоком восемнадцатого транзистора п-типа, сток одиннадцатого транзистора п-типа - с истоком пятнадцатого транзистора п-типа, а стоки двенадцатого и шестнадцатого транзисторов п-типа - с истоком семнадцатого транзистора п-типа, стоки седьмого, пятнадцатого, семнадцатого и восемнадцатого транзисторов п-типа объединены и подключены к общей шине сумматора,о-т л ич а ю щ и и ся тем, что, с целью уменьшения мощности, потребляемой сумматором, в каждый его разряд введены восемь транзисторов р-типа и два малосигнальных элемента НЕ, причем затворы первого и второго транзисторов р-типа подключены к прямому входу первого слагаемого, затворы третьего и четвертого транзисторов

р-типа - к инверсному входу первого слагаемфго, затворы пятого и шестого транзисторов р-типа - к прямому входу второго слагаемого, а затворы седьмого и восьмого транзисторов р-типа - к инверсному входу

второго слагаемого данного разряда сумматора, шина питания сумматора подключена к истокам первого и второго транзисторов р-типа, стоки которых соединены с истоками соответственно третьего и четвертого

транзисторов р-типа, стоки которых соединены с истоками соответственно пятого и шестого транзисторов р-типа, стоки которых соединены с истоками соответственна седьмого и восьмого транзисторов р-типа,

стоки которых соединены с входами соответственно первого и второго элементов НЕ, выходы которых соединены с входами соответственно первого и второго малосигиальных элементов НЕ, выходы которых соёдинейы с входами соответственно первого и второго элементов НЕ.,

| Комбинационный сумматор | 1987 |

|

SU1465881A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-09-30—Публикация

1988-11-14—Подача