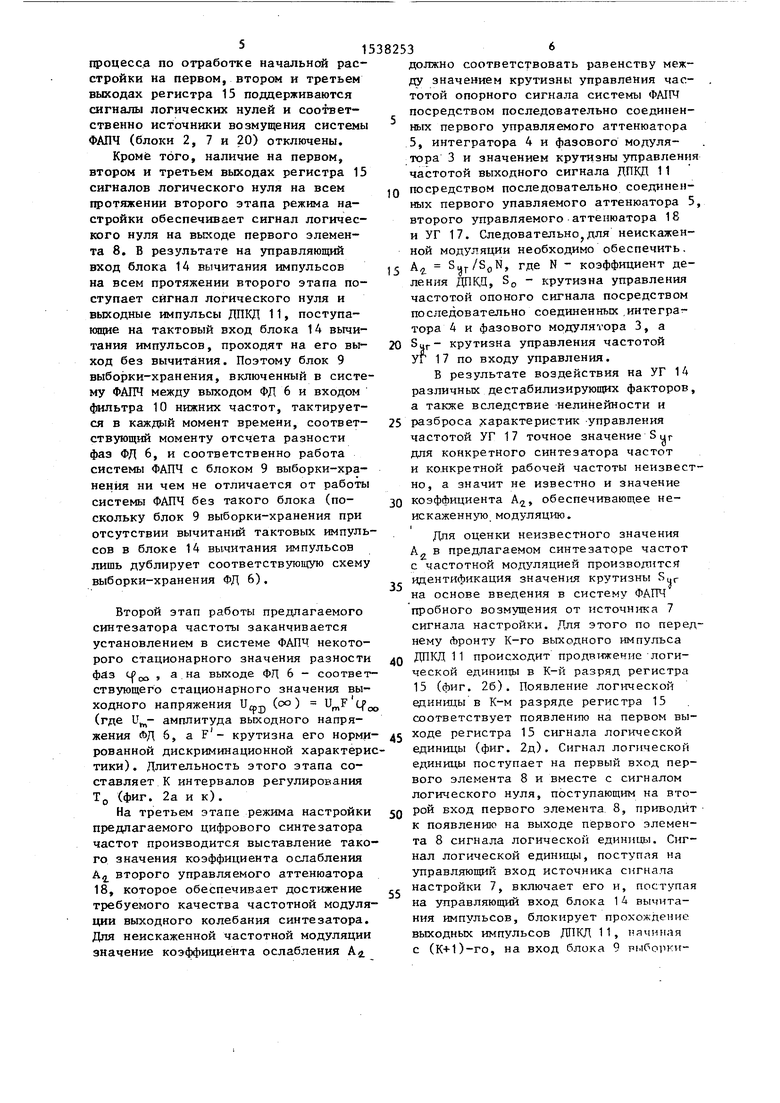

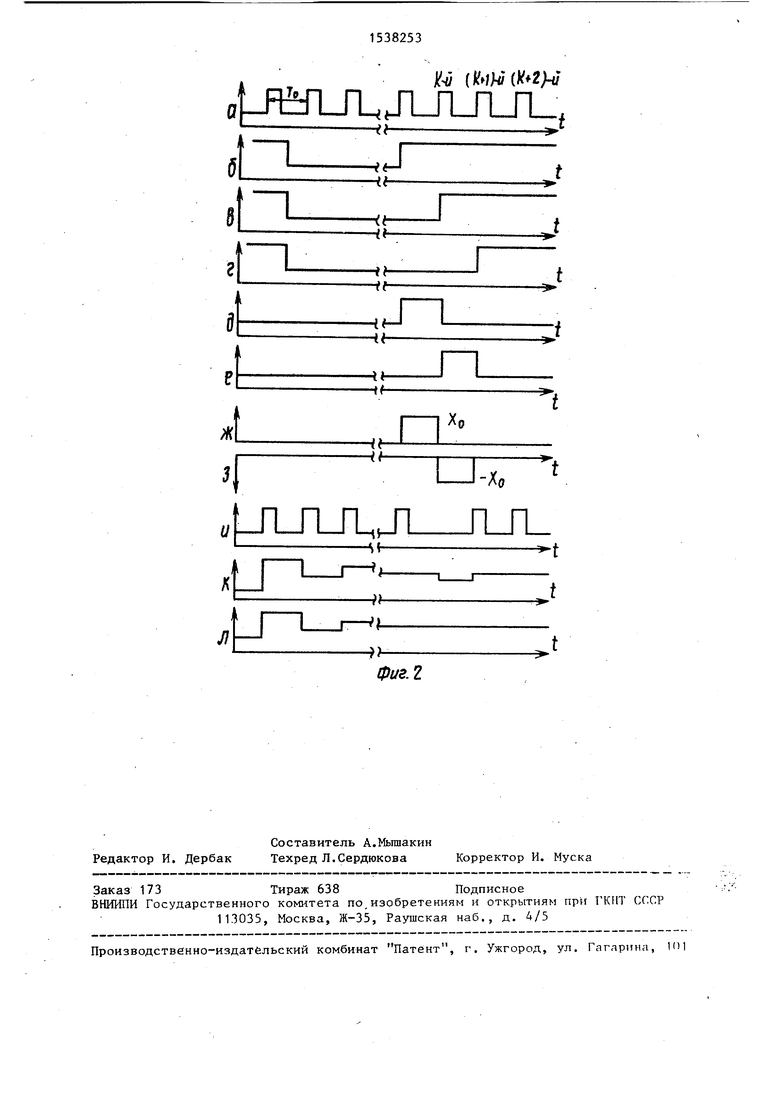

тики). Длительность этого этапа составляет К интервалов регулирования Т0 (фиг. 2а и к).

На третьем этапе режима настройки предлагаемого цифрового синтезатора частот производится выставление такого значения коэффициента ослабления А4 второго управляемого аттенюатора 18, которое обеспечивает достижение требуемого качества частотной модуляции выходного колебания синтезатора. Для неискаженной частотной модуляции значение коэффициента ослабления А.

0

5

единицы поступает на первый вход первого элемента 8 и вместе с сигналом логического нуля, поступающим на второй вход первого элемента 8, приводит к появлению на выходе первого элемента 8 сигнала логической единицы. Сигнал логической единицы, поступая на управляющий вход источника сигнапа настройки 7, включает его и, поступая на управляющий вход блока 14 вычитания импульсов, блокирует прохождение выходных импульсов ДПКД 11, начиная с (К+1)-го, на вход блока 9 выборкихранения (фиг. 2 и). Блокировка тактовых импульсов блока 9 выборки-хранения необходима для размыкания системы ФАПЧ на время введения возмуще- 5 ний в систему. В результате по переднему фронту К-го выходного импульса ДПКД 11 на вход управления УГ 17 от источника 7 сигнала настройки поступает перепад напряжения амплитудой

Х0 (фиг. 2ж). Этот перепад приводит к отклонению разности фаз сигналов, поступающих на входы ФД 6 от стационарного значения к моменту появления на выходе ДПКД 1I следующего (К+1)-го импульса. Величина этого отклонения разности фаз от стационарного значения определяется дополнительным набегом фазы за интервал времени Т0 сигнала, поступающего на дру- 20 гой вход ФД 6. Этот дополнительный набег фазы выходного сигнала ДПКД 11 обусловлен модуляцией частоты колебаний УГ 17 перепадом х0 (поступающим на вход управления УГ 17) и составляет величину х„.8иг. Tft/N.

логической единицы в (К+1)-й разряд этого регистра 6 (фиг. 2г). Появление сигнала логической единицы на втором выходе регистра 15 приводит к переключению выходного сигнала второго элемента 19 с сигнала логического нуля на сигнал логической единицы (фиг. 2е). Сигнал логической единицы поступает на управляющий вход регистра 1 6 и разрешает запись кода z, поступающего на информационный вход регистра 16 положительным перепадом, сформировавшимся на втором выходе 15 АЦП 13 в момент окончания формирования кода z. В результате код z KAU)I.x

10

V

o ToSyr/N

-0-мг/« поступает на вход управления второго управляемого аттенюатора 18. Коэффициент ослабления А,, второго управляемого аттенюатора 18 связан с кодом, поступающим на его вход управления,следующим соотношением: А„ У/К0(где Y код,

поступающий на вход управления, а К0 - коэф25 фициент передачи аттенюатора при ). Поэтому при выставлении кода управления Y z и выборе К0 F x0T0S коэффициент ослабления А второго управляемого аттенюатора 18 становится

30 равным величине, необходимой для неискаженной модуляции, т.е. Аг .

Одновременно с разрешением записи результата измерения значения А, соответствующего неискаженной модуляции,

35 сигнал логической единицы, возникающий на втором выходе регистра 15, производит следующую коммутацию источника возмущения системы ФАПЧ.

Отключается источник 7 сигнала

40 настройки, поскольку измерение требуемого значения А. уже произошло, причем отключение производится сигналом логического нуля, поступающим на управляющий вход источника 7 сигнала

-о °уг

К моменту появления на выходе ДПКД 11 (К+1)-го импульса разность фаз сигналов, поступающих на входы ФД 6, отклоняется от стационарного значения ср юна величину -x6S r-T0/N. Соответствующие этому отклонению разности фаз отклонения выходного напряжения ФД 6 от стационарного значения составляют величину x0S rT0/N (где Uw- амплитуда выходного напряжения ФД 6, а Т1 - крутизна его нормированной дискриминационной характеристики),

(К+1)-й выходной импульс ДПКД 11, поступая на вход Пуск АЦП 13, запус кает процесс преобразования аналогового напряжения, сформированного на выходе ФД 6 в результате отсчета раз- 45 настройки с выхода первого элемента 8.

0

логической единицы в (К+1)-й разряд этого регистра 6 (фиг. 2г). Появление сигнала логической единицы на втором выходе регистра 15 приводит к переключению выходного сигнала второго элемента 19 с сигнала логического нуля на сигнал логической единицы (фиг. 2е). Сигнал логической единицы поступает на управляющий вход регистра 1 6 и разрешает запись кода z, поступающего на информационный вход регистра 16 положительным перепадом, сформировавшимся на втором выходе 5 АЦП 13 в момент окончания формирования кода z. В результате код z KAU)I.x

0

V

o ToSyr/N

-0-мг/« поступает на вход управления второго управляемого аттенюатора 18. Коэффициент ослабления А,, второго управляемого аттенюатора 18 связан с кодом, поступающим на его вход управления,следующим соотношением: А„ У/К0(где Y код,

поступающий на вход управления, а К0 - коэф5 фициент передачи аттенюатора при ). Поэтому при выставлении кода управления Y z и выборе К0 F x0T0S коэффициент ослабления А второго управляемого аттенюатора 18 становится

0 равным величине, необходимой для неискаженной модуляции, т.е. Аг .

Одновременно с разрешением записи результата измерения значения А, соответствующего неискаженной модуляции,

5 сигнал логической единицы, возникающий на втором выходе регистра 15, производит следующую коммутацию источника возмущения системы ФАПЧ.

Отключается источник 7 сигнала

0 настройки, поскольку измерение требуемого значения А. уже произошло, причем отключение производится сигналом логического нуля, поступающим на управляющий вход источника 7 сигнала

5 настройки с выхода первого элемента 8.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты с частотной модуляцией | 1987 |

|

SU1543544A1 |

| Цифровой синтезатор частот с частотной модуляцией | 1985 |

|

SU1293840A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| Цифровой синтезатор частот с частотной модуляцией | 1990 |

|

SU1774465A2 |

| Синтезатор частот | 1976 |

|

SU799101A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Цифровой синтезатор частот с частотной модуляцией | 1990 |

|

SU1704266A1 |

| Цифровой синтезатор частот | 1987 |

|

SU1510080A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1991 |

|

RU2014733C1 |

| Цифровой синтезатор частот с частотной модуляцией | 1987 |

|

SU1515363A2 |

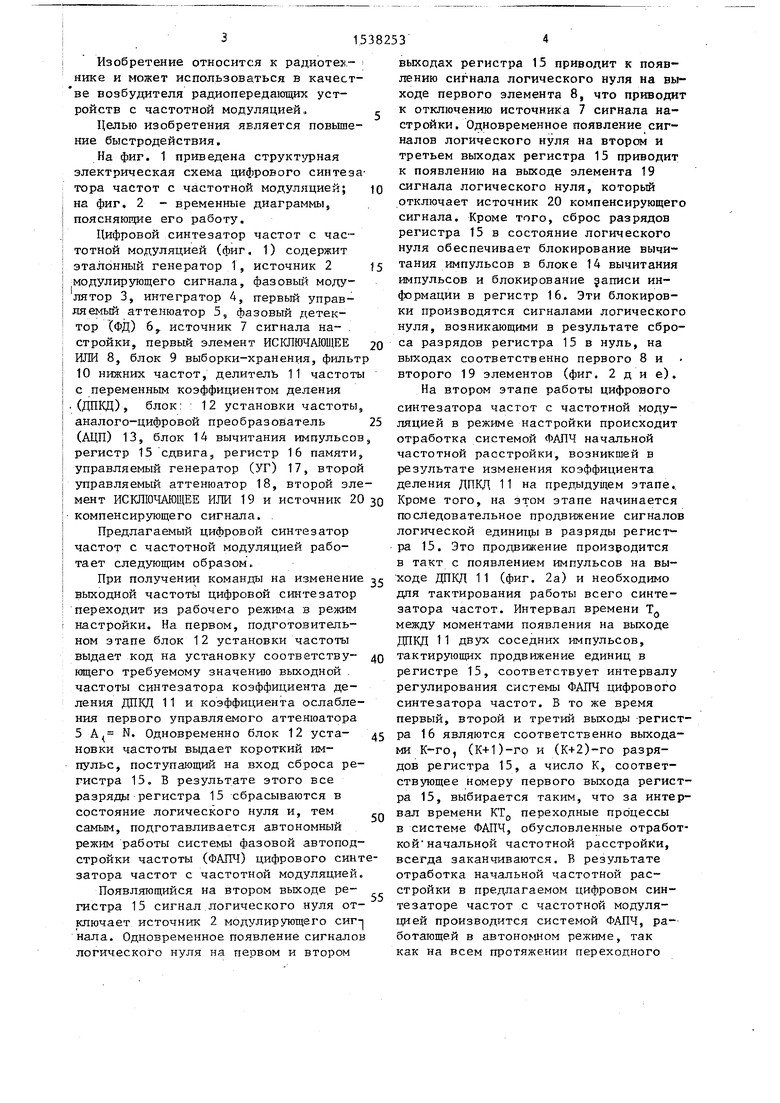

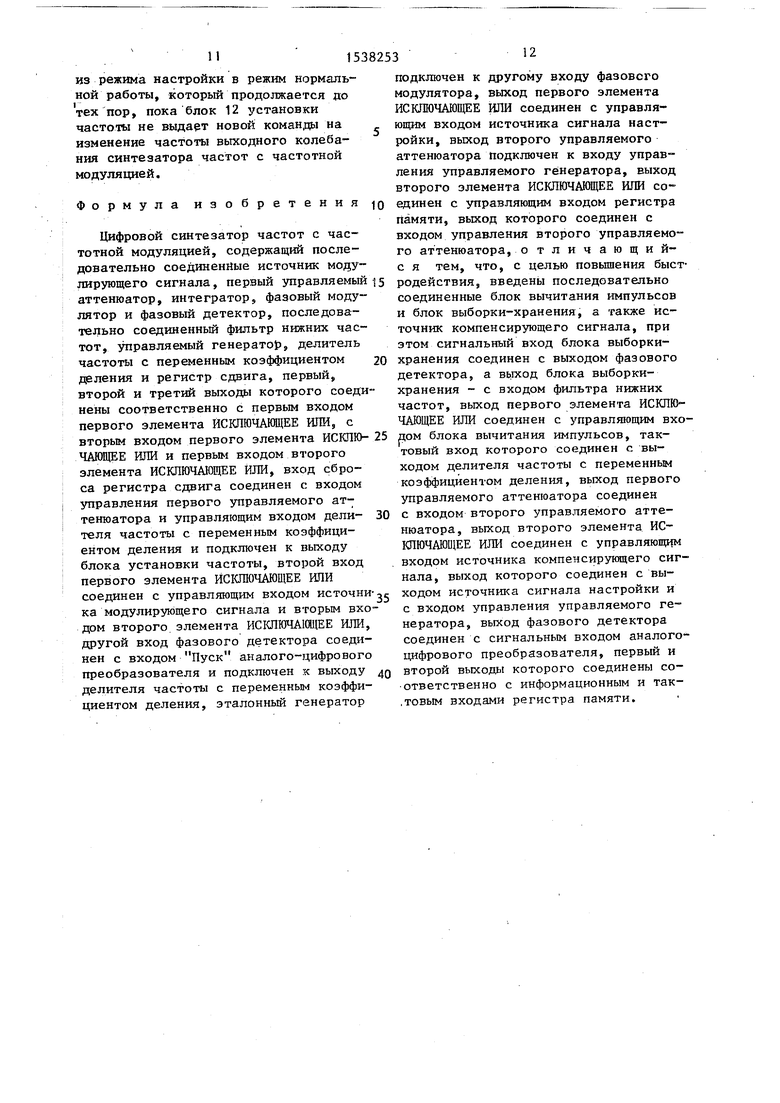

Изобретение относится к радиотехнике. Цель изобретения - повышение быстродействия. Синтезатор содержит эталонный г-р 1, источник 2 модулирующего сигнала, фазовый модулятор 3, интегратор 4, управляемые аттенюаторы 5 и 18, фазовый детектор 6, источник 7 сигнала настройка, эл-ты Исключающее ИЛИ 8 и 19, блок выборки -хранения /БВХ/, 9, фильтр 10 нижних частот, делитель 11 частоты с переменным коэф. деления, блок 12 установки частоты, АЦП 13, блок 14 вычитания импульсов, регистр 15 сдвига, регистр 16 памяти, управляемый г-р 17 и источник 20 компенсирующего сигнала. На первом этапе работы осуществляется установка блоков на заданные параметры. На втором этапе работы в режиме настройки происходит отработка системой фазовой автоподстройки частоты (ФАПЧ) начальной частотной расстройки. При этом система ФАПЧ работает в автономном режиме. На третьем этапе в режиме настройки сводится к нулю отклонение разности фаз в системе ФАПЧ от стационарного значения. Синтезатор переходит из режима настройки в нормальный режим работы. Цель достигается введением БВХ 9, блока вычитания 14 и источника 20. 2 ил.

ности фаз, возникающей к моменту появления этого импульса. На входе АЦП 13 имеется инвертирующий буферный повторитель с соответствующим разделительным конденсатором, поэтому на его сп регистра 15, поскольку на первый вход

выходе формируется цифровой коц 7., пропорциональный величине отклонения выходного напряжения ФД 6 от стационарного значения, взятый с обратным знаком, т.е. z Kau,nUwF x0T0-S r/N (где К ацп - коэффициент преобразования АЦП 13). Кроме того, (К-Н)-й выходной импульс ДПКД 11 . поступая на вход регистра г, продвигает сигнал

55

первого элемента 8 уже поступает сигнал логической единицы с первого выхода регистра 15.

Сигнал логической единицы, возникающий на втором выходе регистра 15, поступая на управляющий вход источника 2 модулирующего сигнала, включает этот источник, поскольку процесс выставления требуемого для модуляции

Сигнал логического нуля возникает в результате воздействия на второй вход первого элемента 8 сигнала логической единицы, возникающей на втором выходе

5

первого элемента 8 уже поступает сигнал логической единицы с первого выхода регистра 15.

Сигнал логической единицы, возникающий на втором выходе регистра 15, поступая на управляющий вход источника 2 модулирующего сигнала, включает этот источник, поскольку процесс выставления требуемого для модуляции

значения коэффициента ослабления аттенюатора 18 в синтезаторе практически закончен и можно переходить в режим модуляции.

Сигнал логической единицы, возникающий на втором выходе регистра 15, включает источник 20 компенсирующего сигнала. Подача компенсирующего сигнала (возмущения) необходима для компенсации отклонения разности фаз в системе ФАПЧ, которое возникает под действием источника 7 сигнала настрой ки, подававшего на вход управления УГ 17 перепад напряжения амплитудой х0 и длительностью в один интервал регулирования Т0(фиг. 2ж). Включение источника 20 компенсирующего сигнала производится сигналом логической единицы, который поступает на его управляющий вход с выхода второго элемента 19, поскольку на выходе второго элемента 19 в результате появления на втором выходе регистра 15 сигнала логической единицы также возникает сигнал логической единицы, возникающий на втором выходе регистра 15, разрешая замыкание системы ФАПЧ, которая разомкнута после появления на первом выходе регистра 16 сигнала логической единицы.

Замыкание системы ФАПЧ производится сигналом логической единицы, возникающим на выходе первого элемента 8 и поступающим на управляющий вход блока 14 вычитания импульсов. Сигнал логической единицы возникает на выходе первого элемента 8 в результате воздействия на его второй вход сигнала логической единицы с второго выхода регистра 15. В результате для всех выходных импульсов ДПКД 11, начиная с (К+2)-го, блокировка тактовых имп льсов блока 9 выборки-хранения отменяется и система ФАПЧ снова замыкается. (К+2)-й выходной импульс ДПКД 11, поступая на вход регистра 15, продвигает сигнал логической единицы в (К+2)-й разряд этого регистра, что приводит к появлению iHa третьем выходе регистра 15 сигна- |jia логической единицы. Сигнал логи- ческой единицы, воздействуя на первый вход второго элемента 19, переключает его выходной сигнал на сигнал логического нуля, поскольку на второй вход второго элемента 19 с второго «ыхода регистра 15 также поступает сигнал логической единицы. Выходной

0

5

0

5

0

5

0

5

0

5

сигнал логического нуля второго элемента 19, поступая на управляющий вход регистра 16, запрещает запись новой информации в этот регистр. Кроме того сигнал логического нуля с выхода второго элемента 19 попадает на управляющий вход источника 20 компенсирующего сигнала и отключает его.

Источник 20 компенсирующего сигнала, включенный (К+1)-м выходным импульсом ДПКД 11 и выключенный (К+2)-м импульсом, подает на вход управления УГ 17 напряжение -х0 в течение длительности одного интервала регулирования Т0 (фиг. 2з). Воздействие этого напряжения приводит к отклонению фазы сигнала, поступающего на другой вход ФД 6 с выхода ДПКД 11, на момент появления (К+2)-го выходного импульса ДПКД 11 на величину T0/N, т.е. на величину, компенсирующую отклонение под действием пробного возмущения, вводимого от источника 7 сигнала настройки.

В результате суммарное отклонение разности фаз от стационарного значения в системе ФАПЧ к моменту появления на выходе ДПКД 11 (К+2)-го импульса практически равно нулю. Наличие ненулевого остаточного отклонения разности фаз в системе может быть обусловлено лишь неидеальностью работы блока 9 выборки-хранения и неточностью компенсации сигнала настройки х0 от источника 7 сигнала настройки компенсирующим возмущением -х0 от источника 20 компенсирующего сигнала.

Третий этап работы предлагаемого синтезатора частот в режиме настройки заканчивается с появлением на выходе ДПКД 11 (К+2)-го импульса и его длительность составляет две длительности Т0 интервала регулирования системы ФАПЧ. К концу этого этапа измерение значения коэффициента ослабления А 2 второго управляемого аттенюатора 18, соответствующего неискаженной модуляции, заканчивается и результат измерения хранится в регистре 16. Откпочение разности фаз в системе ФАПЧ от стационарного значения к концу этого этапа практически сведено к нулю.

Источник модулирующего сигчтя 2 к концу третьего этапа режима ройки включен и синтезатор частоты с окончанием этого этапа перемочит

из режима настройки в режим нормальной работы, который продолжается до тех пор, пока блок 12 установки частоты не выдает новой команды на изменение частоты выходного колебания синтезатора частот с частотной модуляцией.

Формула изобретения

Цифровой синтезатор частот с частотной модуляцией, содержащий последовательно соединенные источник модуподключен к другому входу фазового модулятора, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющим входом источника сигнала настройки, выход второго управляемого аттенюатора подключен к входу управления управляемого генератора, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющим входом регистра памяти, выход которого соединен с входом управления второго управляемо го аттенюатора, отличающий- с я тем, что, с целью повышения быс

лирующего сигнала, первый управляемыйt5 родействия, введены последовательно

аттенюатор, интегратор, фазовый модулятор и фазовый детектор, последовательно соединенный фильтр нижних частот, управляемый генератор, делитель частоты с переменным коэффициентом 20 деления и регистр сдвига, первый, второй и третий выходы которого соединены соответственно с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с

соединенные блок вычитания импульсов и блок выборки-хранения, а также источник компенсирующего сигнала, при этом сигнальный вход блока выборки- хранения соединен с выходом фазового детектора, а выход блока выборки- хранения - с входом фильтра нижних частот, выход первого элемента ИСКЛЮ ЧАЮЩЕЕ ИЛИ соединен с управляющим вх

вторым входом первого элемента ИСКЛЮ- 25 дом блока вычитания импульсов, так- ЧАЮЩЕЕ ИЛИ и первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вход сброса регистра сдвига соединен с входом управления первого управляемого аттенюатора и управляющим входом дели- 30 теля частоты с переменным коэффициентом деления и подключен к выходу блока установки частоты, второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющим входом источни-,,- ка модулирующего сигнала и вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, другой вход фазового детектора соединен с входом Пуск аналого-цифрового преобразователя и подключен к выходу до делителя частоты с переменным коэффициентом деления, эталонный генератор

товый вход которого соединен с выходом делителя частоты с переменным коэффициентом деления, выход первого управляемого аттенюатора соединен с входом второго управляемого аттенюатора, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющим входом источника компенсирующего сиг нала, выход которого соединен с выходом источника сигнала настройки и с входом управления управляемого генератора, выход фазового детектора соединен с сигнальным входом аналого цифрового преобразователя, первый и второй выходы которого соединены соответственно с информационным и тактовым входами регистра памяти.

подключен к другому входу фазового модулятора, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющим входом источника сигнала настройки, выход второго управляемого аттенюатора подключен к входу управления управляемого генератора, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющим входом регистра памяти, выход которого соединен с входом управления второго управляемого аттенюатора, отличающий- с я тем, что, с целью повышения быстродействия, введены последовательно

соединенные блок вычитания импульсов и блок выборки-хранения, а также источник компенсирующего сигнала, при этом сигнальный вход блока выборки- хранения соединен с выходом фазового детектора, а выход блока выборки- хранения - с входом фильтра нижних частот, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющим входом блока вычитания импульсов, так-

товый вход которого соединен с выходом делителя частоты с переменным коэффициентом деления, выход первого управляемого аттенюатора соединен с входом второго управляемого аттенюатора, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющим входом источника компенсирующего сигнала, выход которого соединен с выходом источника сигнала настройки и с входом управления управляемого генератора, выход фазового детектора соединен с сигнальным входом аналого цифрового преобразователя, первый и второй выходы которого соединены соответственно с информационным и тактовым входами регистра памяти.

ft/ (M(MM

Л

.pULTUJI

Ј

-itt

-Xe

t

фиг. 2

| Цифровой синтезатор частоты с частотной модуляцией | 1982 |

|

SU1035776A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой синтезатор частот с частотной модуляцией | 1985 |

|

SU1293840A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-01-23—Публикация

1988-03-30—Подача