%

Изобретение относится к технике дискретных измерений непрерывно изменяющихся во времени электрических сигналов и может быть использовано при необходимости сокращения избыточности (сжатия) информации.

Цель изобретения - повышение ин- формативности и точности устройства.

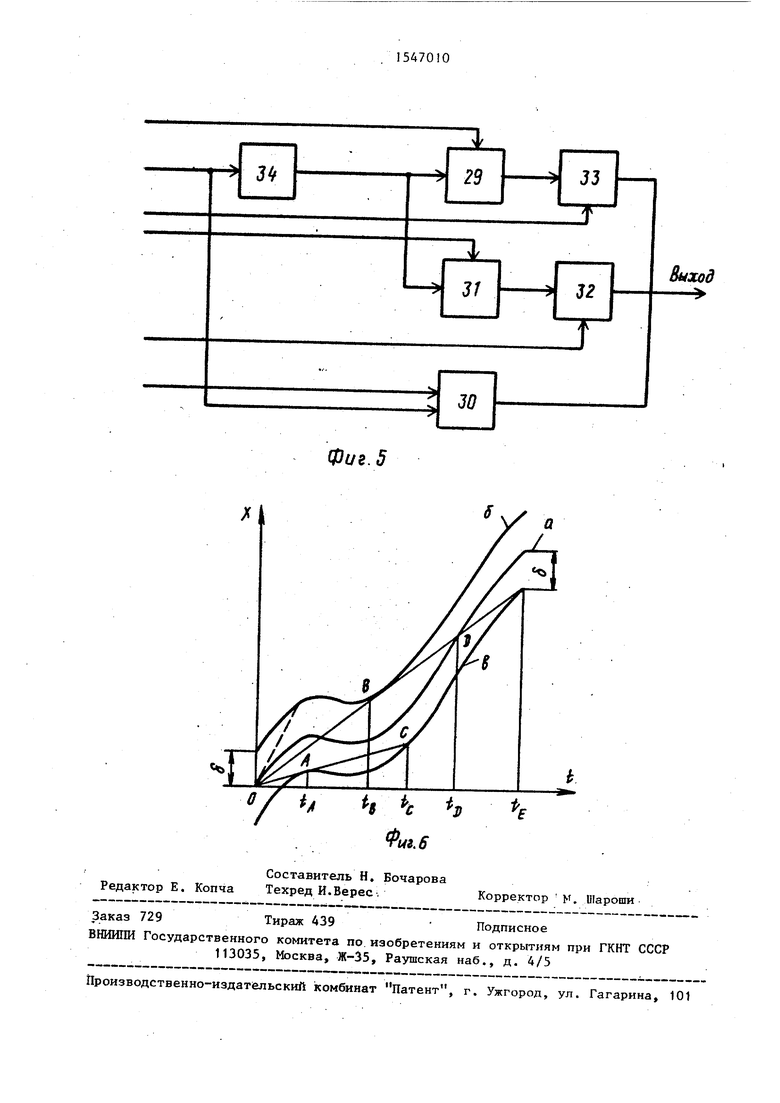

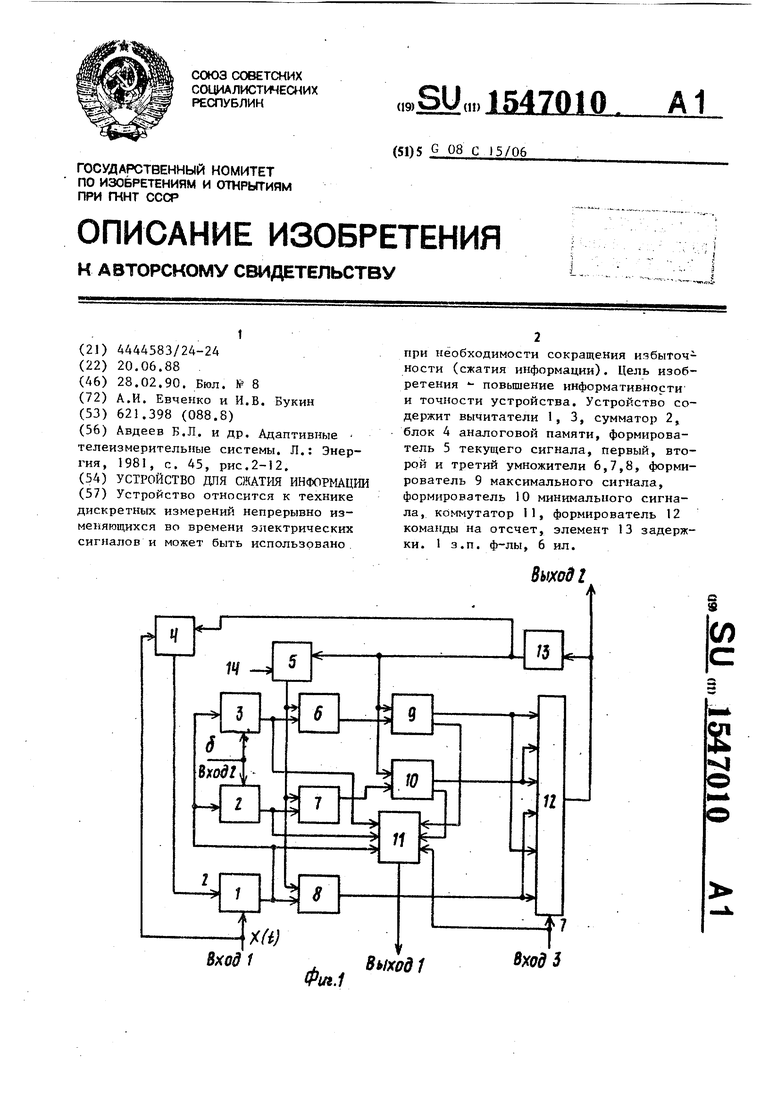

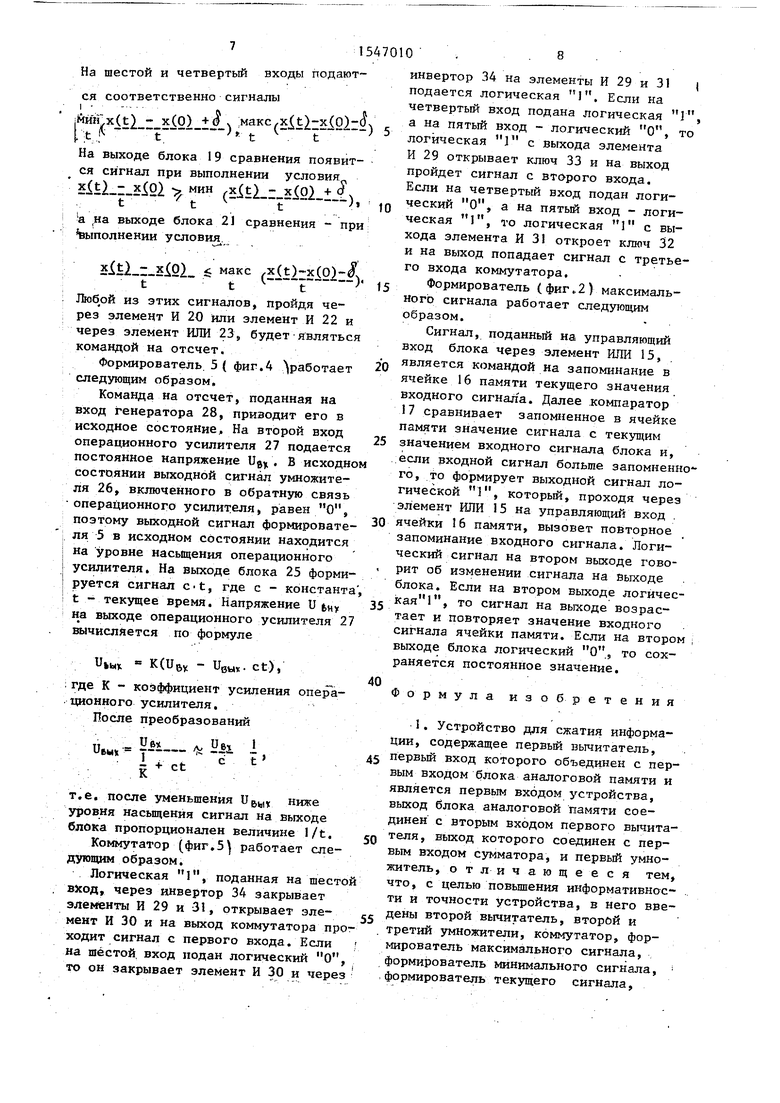

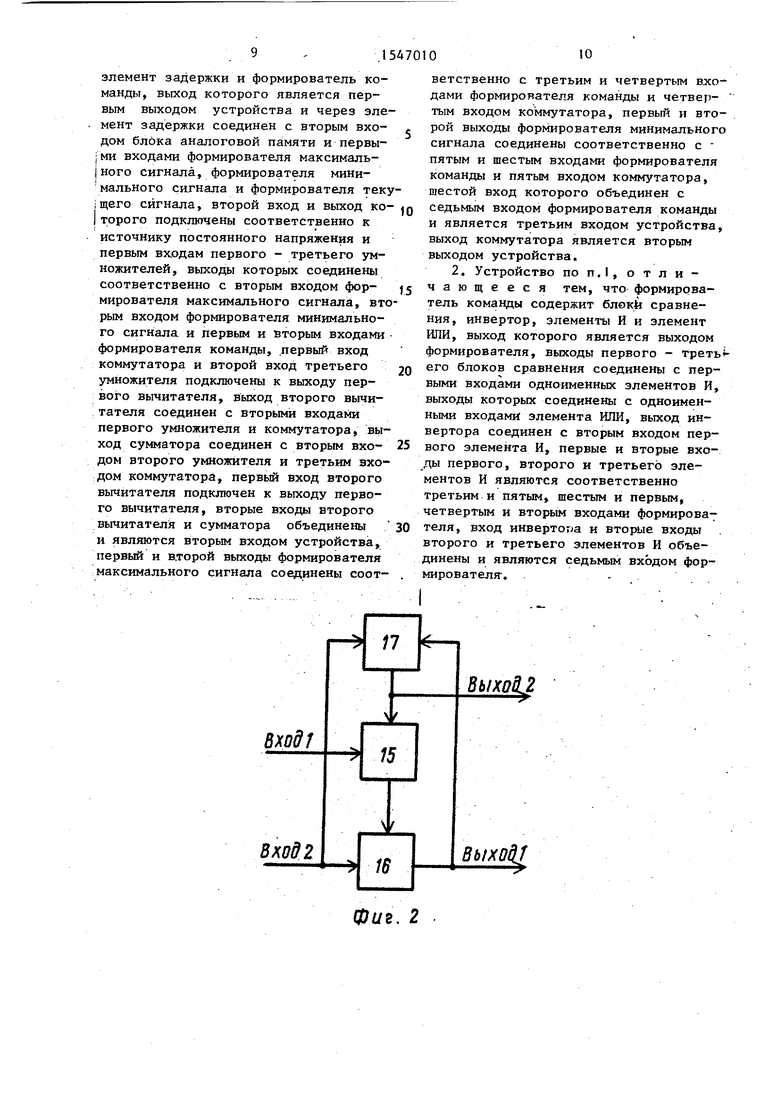

На фиг.1 изображена структурная схема предлагаемого устройства; на фиг.2 - 5 возможные схемы реализации соответственно формирователя максимального сигнала, формирователя команды на отсчет, формирователя текуще го сигнала, коммутатора; на фиг,6 - временные диаграммы работы предлагаемого устройства.

Устройство для сжатия информации , содержит (фиг.1) первый вычитатель 1, сумматор 2, второй вычитатель 3, блок 4 аналоговой памяти, формирователь 5 текущего сигнала, первый 6, второй 7 и третий 8 умножители, формирователь 9 максимального сигнала, формирователь 10 минимального сигнала, коммутатор 11, формирователь 12 команды на отсчет, элемент 13 задержки, шину 14 постоянного напряжения.

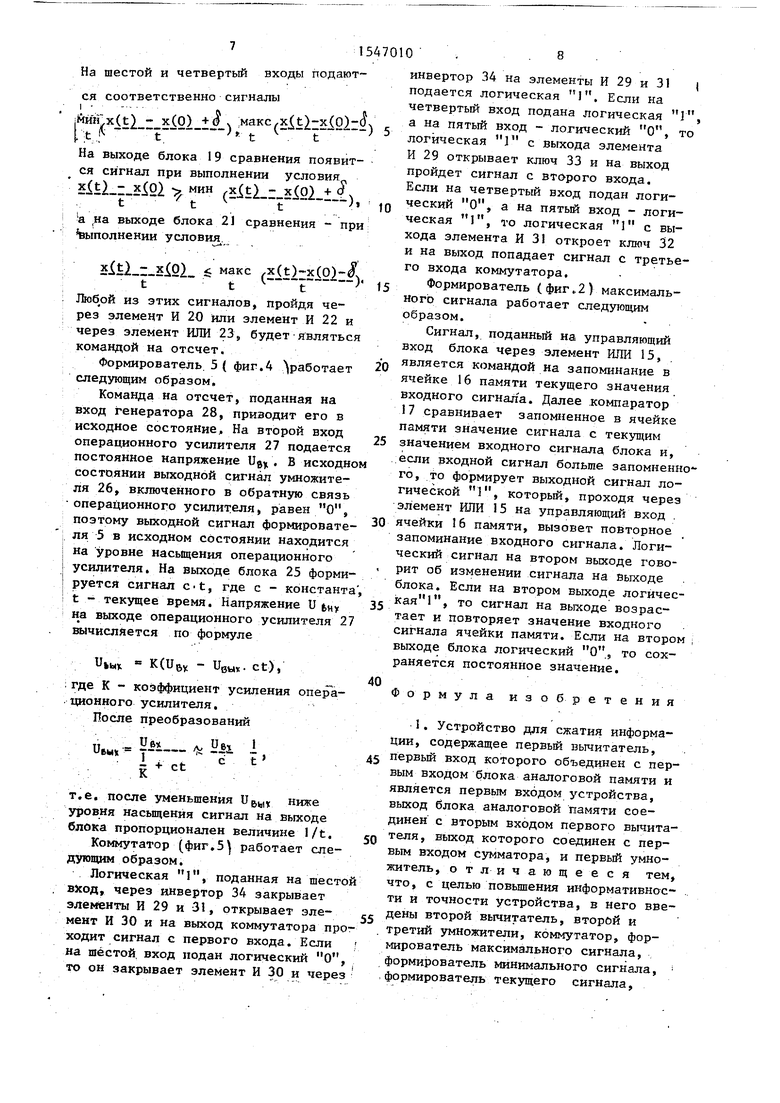

Формирователь 9 максимального сигнала (фиг.2) содержит элемент ИЛИ 15, ячейку 16 памяти, компаратор 17, причем первый формирователь 12 команды на отсчет (фиг.З) содержит первый элемент И 18, второй блок 19 сравне- ния, второй элемент И 20, третий блок 21 сравнения, третий элемент И 22, элемент ИЛИ 23, инвертор 24, первый блок 25 сравнения.

.с

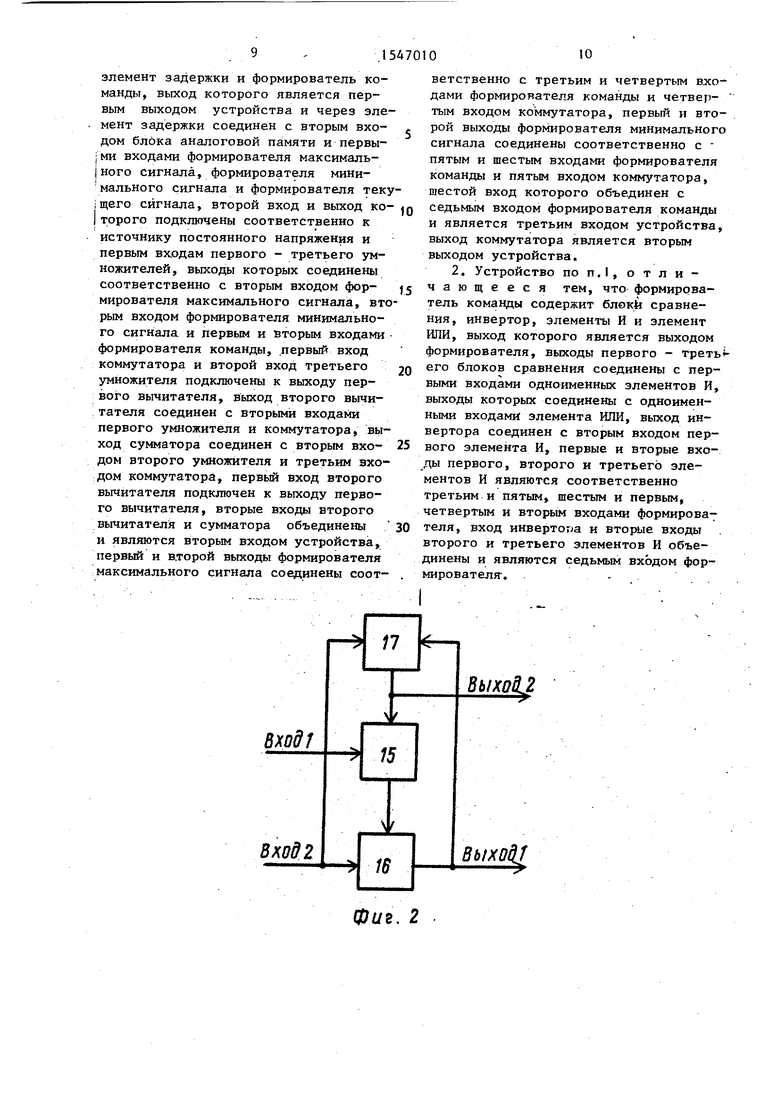

Формирователь 5 текущего сигнала

(фиг.4) содержит умножитель 26, операционный усилитель 27, генератор 28 линейного напряжения.

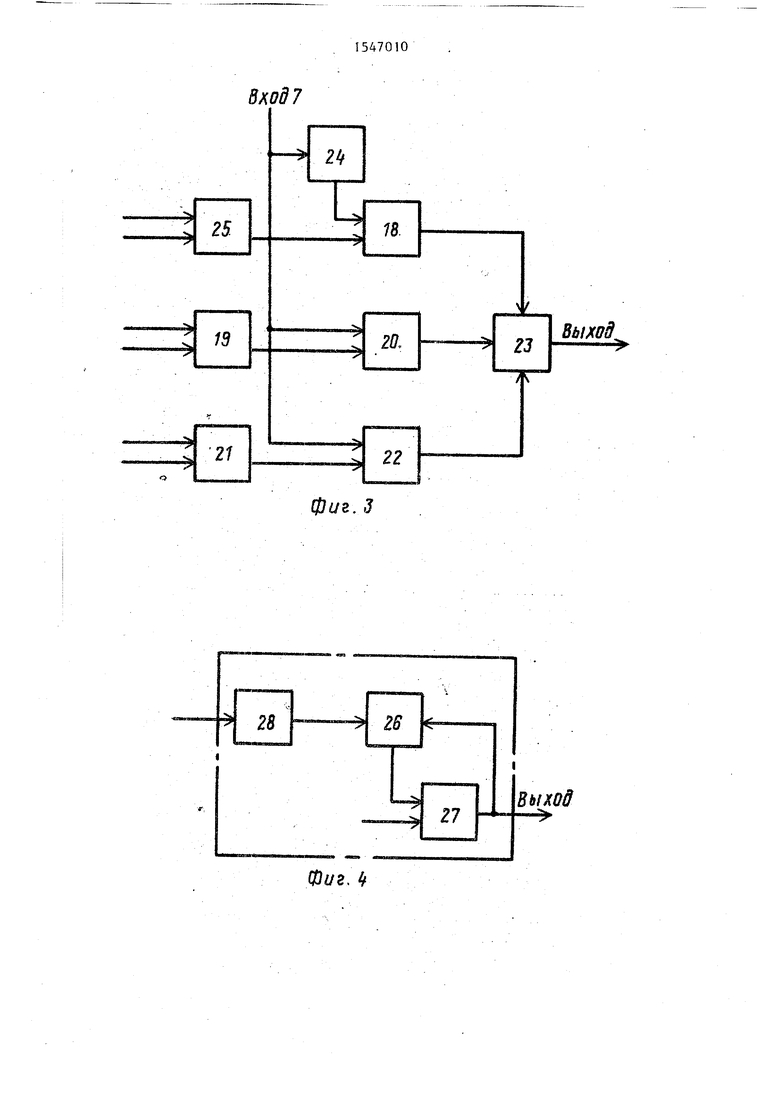

Коммутатор (фиг,4) содержит эле- менты И 29-31, ключи 32 и 33, инвертор 34.ч

Устройство работает следующим образом.

На первый вход устройства подается сжимаемый сигнал x(t). Ka второй вход устройства из измерительной системы, в состав которой входит устройство сжатия, подается сигнал of пропорциональный допустимой погреошос ти аппроксимации сигнала x(t) лома- ной x(t), соединяющей значения отсчета. На третий вход устройства подается сигнал логического О или логи-

ческой 1, который задает режим работы устройства. Если на третий г вход устройства подан сигнал логичес кий О (режим 1), то на аппроксимирующую ломаную не накладывается дополнительных ограничений, кроме выполнения условия

x(t) - S(t)T. (i)

При этом к моменту отсчета очередной отрезок ломаной как и в прототипе отличается от сжимаемого сигнала на величину о (иначе отрезок можно было бы продолжать дальше и не делать отсчета сигнала). Однако в отличие от прототипа наклон x(t) аппроксимирующего сигнала не совпадает с производной x(t) контролируемого сигнала в момент tj предыдущего отсчета, а определяется из условия i максимизации интервала t)+4-- tj между двумя отсчетами.

Если на третий вход устройства подана логическая 1 (режим 2), то дополнительно к условию (1) аппрок- симирующая ломаная удовлетворяет требованиям непрерывности совпадения значений x(t) и x(t) в моменты произ ведения счетов. ,

При пуске устройства и в моменты Формирования отсчетов на управляющие входы блока 4, формирователей 9,10 и 5 подается сигнал, приводящий их в исходное состояние и осуществляющий запись входного сигнала x(t) в блок 4. На выходе первого вычитате- ля 1 формируется сигнал x(t)-x(0), где x(t) - текущее значение сжимаемого сигнала; х(0) - значение сигнала в момент предыдущего отсчета. На вы ходе сумматора 2 формируется сигнал x(t)-x(0) +о, а на выходе второго вычитателя 3 - сигнал x(t)-x(0)-$. На выходе формирователя 5 формируется сигнал, при малых t ограниченный уровнем насыщения операционного усилителя, а в дальнейшем приблизительно равный 1/t, где t - текущее время с момента последнего отсчета. На выходе первого 6, второго 7 и третьего 8 умножителей формируются соответственно сигналы .fx(t)-x (0)- #1 /tj Ix(t)-x(0) +S /t; rx(t)-x(0)/t. Ha первом выходе формирователя 9 формируется сигнал, равный максимальному значению выходного сигнала с первого умножителя 6, причем на втором выходе формирователя 9 формируется логическая 1, если максимальное значение сигнала совпадает с текущим значением. На первом выходе формирователя

10аналогично формируется сигнал, равный минимальному значению выходного сигнала второго умножителя 7. Формирователь 12 формирует команду на отсчет.

Значение отсчитываемого сигнала x(t) вводится в измерительную систему с выходов одного из вычи тателей 1 и 3 и сумматора 2 через коммутатор

11в зависимости от режима, установленного на третьем входе устройства, и сигналов на вторых выходах формирователей 9 и 10.

В режиме 1 команда на отсчет формируется при нарушении условия

мин ,x(t) - ) +§. t ( t }

макс /x(t)(q)-04 (2)

К моменту отсчета на одном из формирователей 9 и 10 значение выходного сигнала совпадает со значением входного сигнала. Коммутатор 11 пропускает на второй выход устройства выходной сигнал вычитателя 3, равный x(t)-x(0) -О, если равны выходной и входной сигналы формирователя 9 максимума. В противном случае на второй выход устройства подается сигнал x(t)-x(0) + о с сумматора 2.

Во втором режиме команда на отсчет формируется формирователем 12 при нарушении любого из условий

rx(tL.(0) x(t2 - x«))

1 t t

(x( xЈti-I 2l°i

Значение отсчета в этом режиме равно x(t)-x(0), снимается через коммутатор 11 с: выхода вычитателя 1.

Элемент 13 задержки предназначен для того, чтобы устройство не было приведено в исходное состояние командой на отсчет раньше, чем сигнал с первого выхода устройства будет зафиксирован в аналого-цифровом преоб- раз вателе измерительной системы.

На фиг.6 приведена графическая иллюстрация работы устройства. Нача

5

0

5

0

ло координат на фиг.6 совмещено с моментом отсчета. Буквой q обозначена кривая, соответствующая выходному сигналу x(t)-x(0) вычитателя 1 , а , кривые б и & соответствуют сигналам у,(t) x(t)-x(0) + & и ) x(t) - х(0) + о на выходах сумматора 2 и вычитателя 3. Угол наклона отрезка, соединяющего начало координат с точкой (t, y(t)) на кривой у равен величине входного сигнала формирователя 10 минимального сигнала в момент времени t, а угол наклона отрезка, соединяющего начало координат с точкой на кривой у/2 равен величине входного сигнала формирователя 9 максимального сигнала. Из фиг.6 видно, что при О t it4 сигнал на входе формирователя 10 падает, а на входе формирователя 9 растет. Начиная с момента tp, сигнал на входе формирователя 9 начнет уменьшаться и на первом его выходе будет сохраняться до момента tc постоянный сигнал t/Mr, равный углу наклона отрезка ОС к оси

) arctg(y(tA)/tfl).

Блок формирования команды на отсчет (фиг.4} работает следующим образом.

На первый вход блока подается

35

сигнал макс

, x(t) - х(0) -(5, ( - }

на второй вход сигнал

МИН().

40

На выходе блока 17 сравнения появится сигнал при выполнении условия

MHH.)(g) макс,х(ь2-хЈ0)..

t.

В режиме 1 сигнал логического О поданный на седьмой вход формирователя 12, пройдя через инвертор 21, откроет элемент И 18, поэтому выходной сигнал компаратора 17 пройдет через элементы И 18 и ИЛИ 23 и будет являться командой на отсчет. Во втором режиме на седьмой вход блока подана логическая 1, которая открывает элементы И 20 и 22 и через инвертор 24 закрывает элемент И 18.

На первый вход и второй вход форx(tbxjCO) t

мирователя подается сигнал

71547010

На шестой и четвертый входы подаются соответственно сигналы

.ifofliXt:) - х(0) + v макс хХЈ -хЈо1:Л) t | t t

На выходе блока 19 сравнения появится сигнал при выполнении условия 5&1-1-2.Й2 мин () t t v t а на выходе блока 21 сравнения - при выполнении условия

10

Ј макс /x tbxjCg2;04 у

Люб/зй из этих сигналов, пройдя через элемент И 20 или элемент И 22 и через элемент ИЛИ 23„ будет являться командой на отсчет.

Формирователь 5( фиг.4 работает следующим образом.

Команда на отсчет, поданная на вход генератора 28, приводит его в исходное состояние, На второй вход операционного усилителя 27 подается постоянное напряжение U. В исходно состоянии выходной сигнал умножителя 26t включенного в обратную связь операционного усилителя, равен О, поэтому выходной сигнал формирователя 5 в исходном состоянии находится на уровне насыщения операционного усилителя. На выходе блока 25 формируется сигнал с t, где с - константа t - текущее время. Напряжение U fc«Ґ на выходе операционного усилителя 27 вычисляется по формуле

1W K(UBX - ивш. ct),

где К - коэффициент усиления операционного усилителя.

После преобразований

f

и 6

к

ct

А, V 1

- ™- Ё

50

т.е. после уменьшения UBwr ниже уровня насыщения сигнал на выходе блока пропорционален величине 1/t.

Коммутатор (фиг.5} работает следующим образом.

Логическая 1, поданная на шестой вход, через инвертор 34 закрывает элементы И 29 и 31, открывает эле- 5 мент И 30 и на выход коммутатора проходит сигнал с первого входа. Если на шестой вход подан логический О, то он закрывает элемент И 30 и через

8

инвертор 34 на элементы И 29 и 31 | подается логическая 1. Если на четвертый вход подана логическая 1, а на пятый вход - логический О, то логическая J с выхода элемента И 29 открывает ключ 33 и на выход пройдет сигнал с второго входа. Если на четвертый вход подан логический О, а на пятый вход - логическая 1, то логическая 1 с выхода элемента И 31 откроет ключ 32 и на выход попадает сигнал с третьего входа коммутатора.

Формирователь (фиг,2) максимального сигнала работает следующим образом.

Сигнал, поданный на управляющий вход блока через элемент ИЛИ 15,

является командой на запоминание в ячейке 16 памяти текущего значения входного сигнала. Далее компаратор 17 сравнивает запомненное в ячейке памяти значение сигнала с текущим

значением входного сигнала блока и, если входной сигнал больше запомненного, то формирует выходной сигнал логической 1, который, проходя через элемент ИЛИ 15 на управляющий вход

ячейки 16 памяти, вызовет повторное запоминание входного сигнала. Логический сигнал на втором выходе гово- рит об изменении сигнала на выходе блока. Если на втором выходе логическая М, то сигнал на выходе возрастает и повторяет значение входного сигнала ячейки памяти. Если на втором выходе блока логический то сохраняется постоянное значение.

Формула изобретения

1. Устройство для сжатия информации, содержащее первый вычитатель, первый вход которого объединен с первым входом блока аналоговой памяти и является первым входом устройства, выход блока аналоговой памяти соединен с вторым входом первого вычита- теля, выход которого соединен с первым входом сумматора, и первый умножитель, отличающееся тем, что, с целью повышения информативности и точности устройства, в него введены второй вычитатель, второй и третий умножители, коммутатор, формирователь максимального сигнала, формирователь минимального сигнала, формирователь текущего сигнала,

элемент задержки и формирователь команды, выход которого является первым выходом устройства и через элемент задержки соединен с вторым вхо- дом блока аналоговой памяти и первы- ми входами формирователя максималь- ного сигнала, формирователя минимального сигнала и формирователя теку- щего сигнала, второй вход и выход ко- JQ торого подключены соответственно к источнику постоянного напряжения и первым входам первого - третьего умножителей, выходы которых соединены соответственно с вторым входом фор- 75 мирователя максимального сигнала, вторым входом формирователя минимального сигнала и первым и вторым входами ормирователя команды, первый вход коммутатора и второй вход третьего 20 умножителя подключены к выходу первого вычитателя, выход второго вычи- тателя соединен с вторыми входами первого умножителя и коммутатора, выход сумматора соединен с вторым вхо- 25 ом второго умножителя и третьим вхоом коммутатора, первый вход второго вычитателя подключен к выходу первого вычитателя, вторые входы второго вычитателя и сумматора объединены 30 и являются вторым входом устройства, первый и в,торой выходы формирователя аксимального сигнала соединены соот- .

ветственно с третьим и четвертым входами формирователя команды и четвертым входом коммутатора, первый я второй выходы формирователя минимального сигнала соединены соответственно с - пятым и шестым входами формирователя команды и пятым входом коммутатора, шестой вход которого объединен с седьмым входом формирователя команды и является третьим входом устройства, выход коммутатора является вторым выходом устройства.

2. Устройство по п.I, о т л и - чающееся тем, что формирователь команды содержит блокЬ сравнения, инвертор, элементы И и элемент ИЛИ, выход которого является выходом формирователя, выходы первого - треть его блоков сравнения соединены с первыми входами одноименных элементов И, выходы которых соединены с одноименными входами элемента ИЛИ, выход инвертора соединен с вторым входом первого элемента И, первые и вторые входы первого, второго и третьего элементов И являются соответственно третьим и пятым, шестым и первым, четвертым и вторым входами формирова7 теля, вход инвертора и вторые входы второго и третьего элементов И объединены и являются седьмым входом формирователя-.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия информации | 1986 |

|

SU1324047A1 |

| Устройство для сжатия и передачи информации | 1988 |

|

SU1515183A1 |

| Цифровой частотный демодулятор | 1991 |

|

SU1817249A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1989 |

|

SU1672575A2 |

| СИСТЕМА НАВИГАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 1992 |

|

RU2022356C1 |

| Система передачи телевизионного сигнала | 1985 |

|

SU1277429A2 |

| Адаптивное устройство для сокращения избыточности цифровой информации | 1983 |

|

SU1136201A1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2212110C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КООРДИНАТ ГЕОМЕТРИЧЕСКОГО ЦЕНТРА ОБЪЕКТА | 1985 |

|

SU1380590A1 |

Устройство к технике дискретных измерений непрерывно изменяющихся во времени электрических сигналов и может быть использовано при необходимости сокращения избыточности (сжатия информации). Цель изобретения - повышение информативности и точности устройства. Устройство содержит вычитатели 1, 3, сумматор 2 блок 4 аналоговой памяти, формирователь 5 текущего сигнала, первый, второй и третий умножители 6,7,8, формирователь 9 максимального сигнала, формирователь 10 минимального сигнала, коммутатор 11, формирователь 12 команды на отсчет, элемент 13 задержки. 1 з.п. ф-лы, 6 ил.

Фиг. 2

goxwQ

а

Г

/г.

ЈW

б/

.

ш

г

«

Фиг. 5

| Авдеев Б.Л | |||

| и др | |||

| Адаптивные телеизмерительные системы | |||

| Л.: Энергия, 1981, с | |||

| Железобетонный фасонный камень для кладки стен | 1920 |

|

SU45A1 |

Авторы

Даты

1990-02-28—Публикация

1988-06-20—Подача