1

Изобретение относится к вычислительной технике и может быть применено в оперативных и постоянных магнитных запоминающих устройствах (ЗУ) большого объема.

Известны усилители считывания (УС), содержащие многоканальный усилитель постоянного тока (УПТ) со схемами выбора канала и стробирования, амплитудный селектор и выходной каскад 13 Q

Недостаток усилителей - всхвительность к сигналам только определенной полярности.

Наиболее близким к предлагаемому по технической сущности является уси- ,5 литель считывания, имеющий схемное решение, обеспечивающее управляемую полярочувствительность, в котором с;тробируемый усилитель постоянного тока, состоящий из предварительного и оконеч- 20 кого дифференциальных усилительных каскадов, причем одни выходы предварителзь-ных дифференциальных каскадов подключены к первому входу оконечного дифференциального каскада, щзугие - ко второму входа оконечного дифференциального .скада, стробируемые входы пред варительных дифференциальных каскадов подключены к соответствующим выходам узла выбора канала, один из входов которого подключен к выходу формирователя импульсов отбора и стробируемому входу оконечного дифференциального каскада, амплитудный селектор, инверторы и выходной каскад 2 .

Недостатком известного УС является большая потребляемая мощность.

Цель изобретения - уменьшение потребляемой схемной мощности и упрсядвние усилителя.

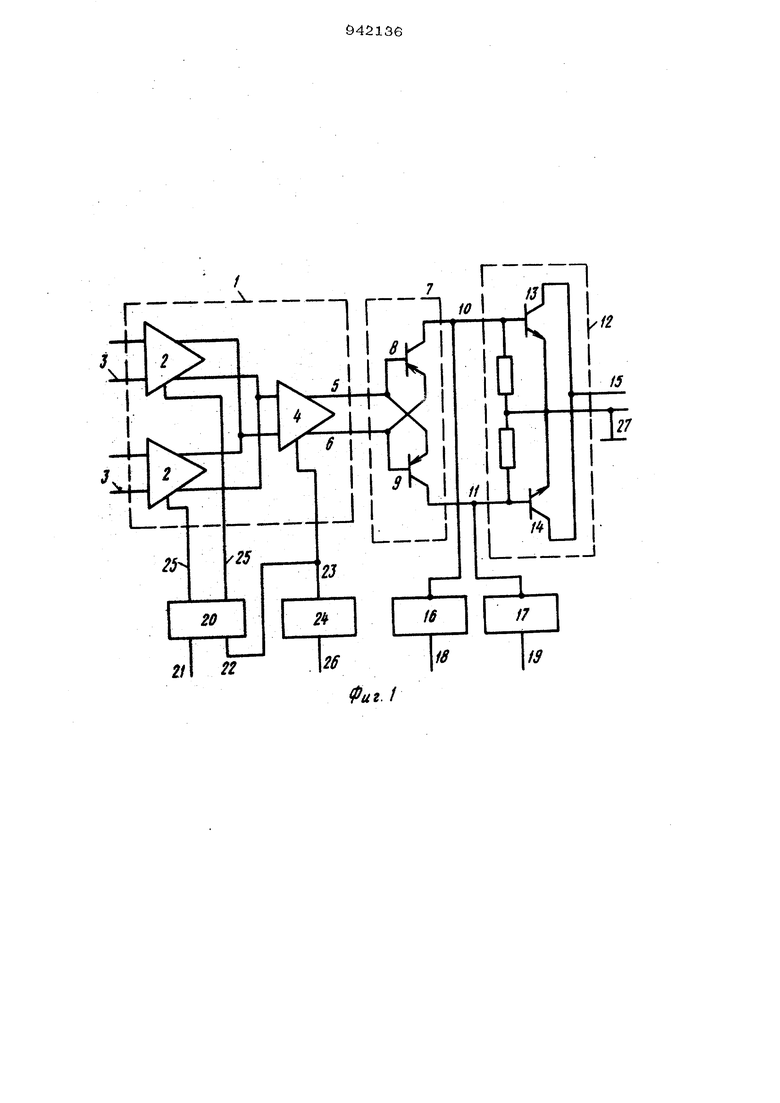

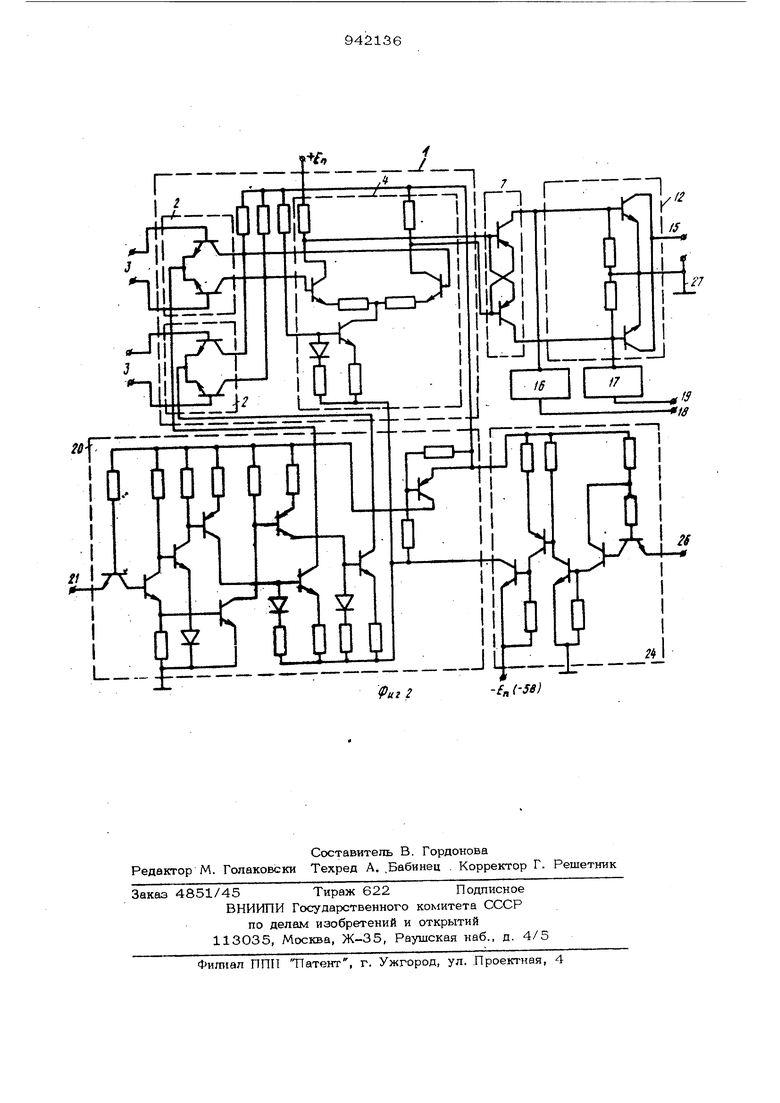

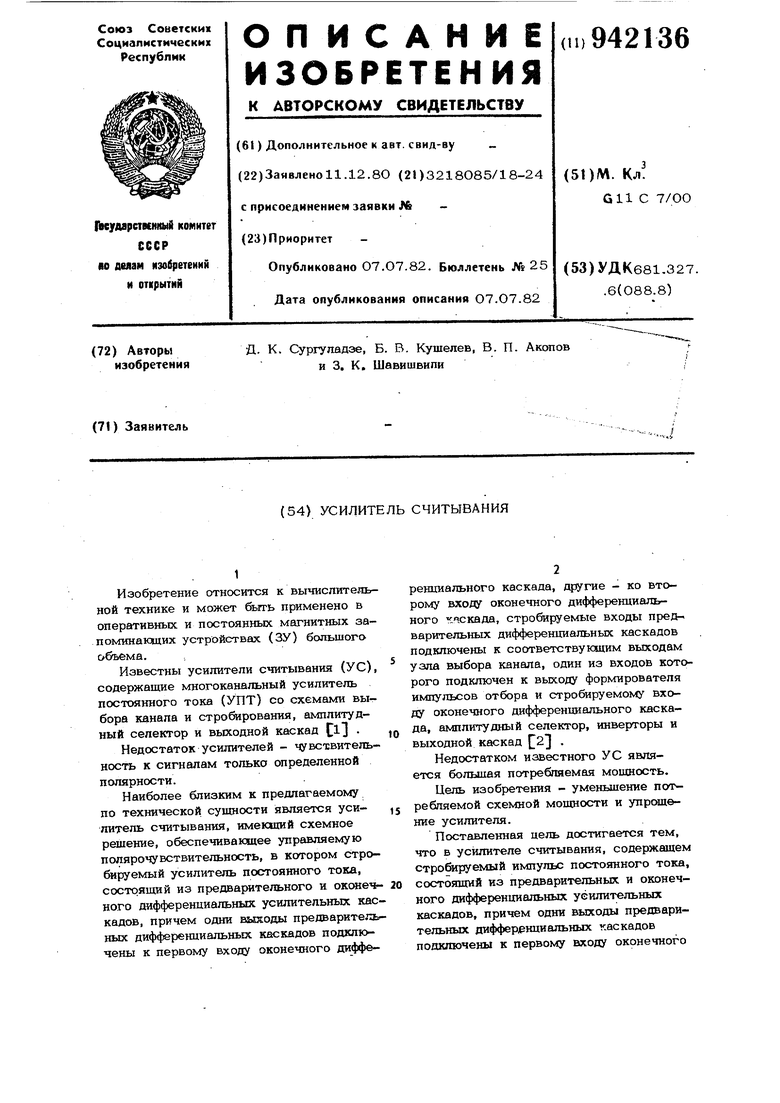

Поставленная цель достигается тем, что в усилителе считывания, содержащем стробируемый импульс постоянного тока, состоящий из предварительных и оконечного дифференциальных усилительных каскадов, причем одни выходы предварительных дифферэнциальных каскадов подключены к первому входу оконечного дифференциального каскада, другие - ко второму входу оконечного дифференциального каскада, стробируемые входы предварительных дифференциальных каскадов подключены к соответствующим выходам узла выбора канала, один из входов которого подключен к выходу формирователя импульсов строба и стробируемому входу оконечного дифференциального каскада, амплитудный селектор, инверторы и выходной каскад, амплитудный селектор вьшолнен на трешзисторах р-п-р типа с перекрестно соединенными базами и эмиттерами, ойцие точки соединения которых подключены к соответствующим выходам оконечного ди ференциального каскада, коллекторы транзисторов подключены к соответствующим выходам инверторов и входам вых ного каскада, выход которого является выходом усилителя. . На фиг. 1 представлена схема усилит ля с управляемой полярочувствительностью; на фиг. 2 - схема реализации усил теля считывания. Усилитель считывания содержит двух- канальный стробируемый усилитель 1 пос тоянного тока, состоящий из объединенных по выходу двух предварительных диф фереициальных усилительных каскадов 2 с двумя парами симметричных входных сигнальньгх шин 3 и оконечного дифферен циального усилительного каскада (ДУК) 4, выходные шины 5 и 6, которого подключены к симметричному входу амплитудного селектора 7, выполненного на транзисторах 8 и 9 р-п-р типа с перекрестно включенны м базовыми и эмиттер ными выводами и одновременно вьшолняющего функции схемы разделениясигналов по полярности и каскада савтлга уров ня между выходами оконечного дифферен циального усилителя каскада 4 и входам 10 и И выходного каскада 12, выполненного на транзисторах 13 и 14, колле торы которых объединены и подключены к основному выходу 15 усилителя. Упра ление полярочувствительностью усилител считывания осуществляется с помощью инверторов 16 и 17, открытые коллекто ные выходы котооых непосредственно подключены ко входам 10 и 11 соответственно выходного каскада 12, а на входы 18 и 19 подаются логические сигналы управления полярочувствительностью. В усилитель введена .схема 20 выбора канала, представляющая собой импульсно-потенциапьный дешифратор. на вход 21 которого подается потенциальный код адреса канала, импульсный вход 22 подключен к выходу 23 формирователя 24 стробирующего импульса, а выходы 25 соединены со стробируемыми входами предварительных дифференциальных усилительных каскадов 2. Стробирукщий импульс поступает на вход 26, а шина 27 является обдей. Усилитель работает следующим образом. б исходном состоянии на входе 26 стробирующий импульс отсутствует, на выходы 23 формирователя 24 стробируищего импульса установлен высокийзапрещающий уровень напряжения и дифференциальные усилительные каскады 2, и 4 заперты. При этом ввиду отсутствия разности потенциалов между шинами 5 и 6 транзисторы 8 и 9 амплитудного селектора 7 заперты, что приводит к выключению транзисторов 13 и 14 выходного каскада 12. На входах 18 и 19 установлен высокий потенциал, при котором инверторы 16 и 17 включены и щунтируют входы 1О и 11 выходного каскада 12. Таким офазом, в исходном состоянии весь сигнальный тракт усилителя мощности не потребляет. Рассмотрим работу устройства в цикле считывания информации для случая, когда схема усилителя чувствительна к такой полярности сигнала 1, при считывании которой на выходе оконечного каскада 4 потенциал щины 5 относительно шины 6 повышается. В начале цикла считывания подачей потенциального кода адреса на вход 21 осуществляется подготовка схемы 2О выбора каналов к включению соответствующего предварительного каскада 2. Одновременно для обеспечения заданной полярочувствительности усилителя на входе 19 устанавливается низкий уровень напряжения, при котором инвертор 17 выключается, подготавливая тем самым вход 11 выходного каскада 12 к прохождению сигнала. В момент времени, благоприятный с .точки зрения временной селекции сигнала, на вход 26 подается стробируклций импульс, в течение действия которого на выходе 23 формирователя 24 стробирующего импульса устанавливается низкий разрешающий уровень напряжения. При этом в линейный режим усиления переходят оконечный каскад 4 и один из предварительных каскадов 2, на стробируемый вход которого от схемы 20 выбора канала пост пает низкий разрешающий уровень напряжения. В случае считьшания сигнала 1, который псютупает на входные шины 3 выбранного предварительного каскада 2, на выходе оконечного каскада 4 в момент стробирования появляется дифференциальный сигнал, которому соответствует повышение потенциала шины 5 и понижение потенциала шины 6 относительйо некоторого положительного синфазного уровня, что приводит к отпиранию транзистора 9 амплитудного селектору 7, а транзистор 8 остается выключенным, так как между его базой и эмиттером действует обратное запирающее напряжение. Коллекторный ток транзистора 9 без ответвления в предварительно выключенный инвертор 17 поступает на вход 11 выходного каскада 12 и включает транзистор 14, обеспечивая тем самым установление напряжения логического О на выходной шине 15 УС. В случае считывания сигнала нуля на выходньпс шинах 5 и 6 оконечного ДУК 4 появляется дифференциальный сигнал противоположной полярности, при котором отпирается транзистор 8 амплитудного селектора 7, но так как практически весь его коллекторный ток ответвляется во включенный выход инвертора 16 и потенциал входной щины 10 остается низким, то отпирание транзистора 13 не происходит и выход УС остается в отключенном состоянии.

Переключение усилителя на противоположную полярочувствительность осуществляется выключением в цикле считывания инвертора 16 подачей на его вход 18 низкого логического уровня напряжения, а инвертор 17 остается включенным.

Технико-экономическая эффективность предлагаемого изобретения заключается в уменьшении потребляемой мощности и связанном с ним уменьшением габаритов самого устройства и источников питания, что особенно ошутимо в многоразрядных запоминающих устройствах.

Формула изобретен ия

Усилитель считывания, содержащий стробируемый усилитель постоянного тока, состоящий из предварительных и оконечного дифференциальных усилительных каскадов, причем одни выходы предварительных дифференциальгсых каскадов подключены к первому входу оконечного дифференциального каскада, другие - ко второму входу -оконечного дифференциального каскада, стробируемые входы предварительных дифференциальных каскадов подключены к соответствующим выходам узла выбора канала, один из входов которого подключен к выходу формирователя импульсов строба и стробируемому входу оконечного дифференциального каскада, амплитудный селектор, инверторы и выходной каскад., отличаю- ш и и с я тем, что, с целью уменьшения потребляемой мощности и упрощения усилителя, амплитудный селектор выполнен на транзисторах р-п-р типа с перекрестно соединенными базами и эмиттерами, о&цие точки соединения которых подклюнчены к соответствующим выходам оконечного дифференциального каскада, коллекторы транзисторов подключены к соответствующим клходам инветоров и входам выходного каскада, выход которого является выходом усилителя считывания. Источники информации,

принятые -во внимание при экспертизе

Ontegrrated CircuHs Semiconductor Data Librav-.SeHes A-VoCe. Motoroeer Sewiconductov- Products,1975

2. Каталог интегральных микросхем. Часть 1 (цифровые). Центральное конструкторское бюро, 198О, с. 341-358 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания | 1977 |

|

SU748505A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Стробируемый формирователь с парафазными ттл-выходами | 1978 |

|

SU758502A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Дифференциальный усилитель | 1988 |

|

SU1626327A1 |

| Усилитель считывания | 1981 |

|

SU970461A1 |

| Стробируемый усилитель | 1986 |

|

SU1332525A1 |

| Адресный формирователь | 1981 |

|

SU1014027A1 |

| Запоминающее устройство | 1981 |

|

SU959165A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

fai.l

Авторы

Даты

1982-07-07—Публикация

1980-12-11—Подача