ел

Јь

00

CD N3

Изобретение относится к вычислительной технике и может быть использовано для поиска неисправностей в многопроцессорных вычислительных комплексах повышенной надежности.

Цель изобретения - повышение точности диагностики.

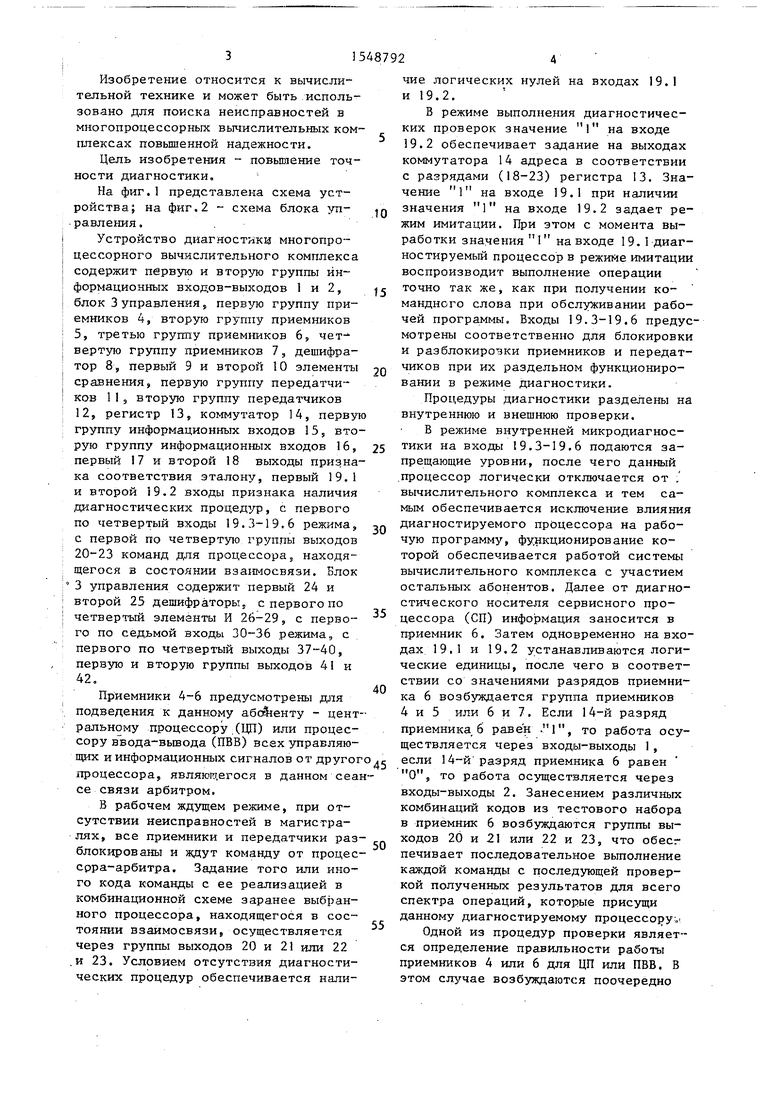

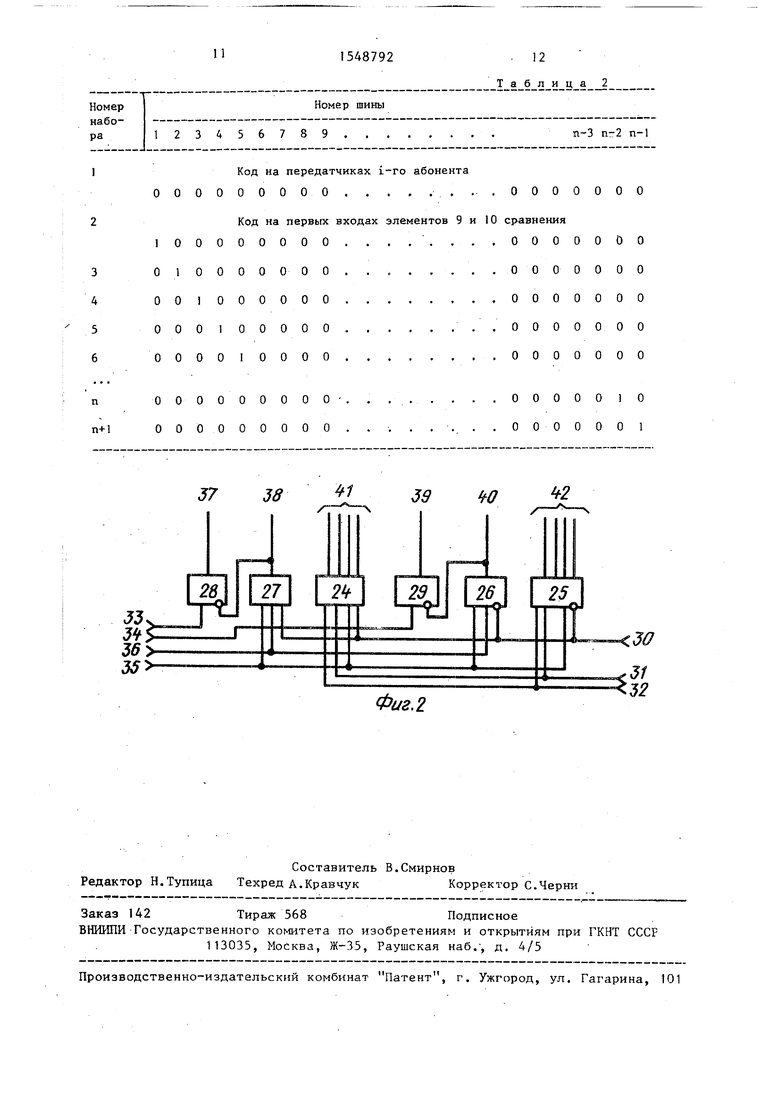

На фиг.1 представлена схема устройства; на фиг.2 - схема блока уп- JQ равления.

Устройство диагностики многопроцессорного вычислительного комплекса содержит первую и вторую группы информационных входов-выходов 1 и 2, j блок 3 управления, первую группу приемников 4, вторую группу приемников 5, третью группу приемников 6, четвертую группу приемников 7, дешифратор 8, первый 9 и второй 10 элементы 20 сравнения, первую группу передатчиков 11э вторую группу передатчиков 12, регистр 13, коммутатор 14, первую группу информационных входов 15 s вторую группу информационных входов 16, 25 первый 17 и второй 18 выходы признака соответствия эталону, первый 19.1 и второй 19.2 входы признака наличия диагностических процедур, с первого по четвертый входы 19.3-19.6 режима, ,0 с первой по четвертую группы выходов 20-23 команд для процессора, находящегося в состоянии взаимосвязи. Блок 3 управления содержит первый 24 и второй 25 дешифраторы, с первого по четвертый элементы И 26-29, с первого по седьмой входы 30-36 режима, с первого по четвертый выходы 37-40, первую и вторую группы выходов 41 и 42.

Приемники 4-6 предусмотрены для подведения к данному абоненту - центральному процессору (ЦП) или процессору ввода-вывода (ПВВ) всех управляющих и информационных сигналов от другого дс процессора, являющегося в данном сеансе связи арбитром.

В рабочем ждущем режиме, при отсутствии неисправностей в магистралях, все приемники и передатчики разблокированы и ждут команду от процес- срра-арбитра. Задание того или иного кода команды с ее реализацией в комбинационной схеме заранее выбранного процессора, находящегося в состоянии взаимосвязи, осуществляется через группы выходов 20 и 21 или 22 и 23. Условием отсутствия диагностических процедур обеспечивается нали35

40

50

55

Q

0 5 0

дс 5

0

50

5

чие логических нулей на входах 19.1 и 19.2.

В режиме выполнения диагностических проверок значение 1 на входе 19.2 обеспечивает задание на выходах коммутатора 14 адреса в соответствии с разрядами (18-23) регистра 13. Значение 1 на входе 19.1 при наличии значения 1 на входе 19.2 задает режим имитации. При этом с момента выработки значения 1 на входе 19. 1 диагностируемый процессор в режиме имитации воспроизводит выполнение операции точно так же, как при получении командного слова при обслуживании рабочей программы. Входы 19.3-19.6 предусмотрены соответственно для блокировки и разблокировки приемников и передатчиков при их раздельном функционировании в режиме диагностики.

Процедуры диагностики разделены на внутреннюю и внешнюю проверки.

В режиме внутренней микродиагностики на входы 19.3-19.6 подаются запрещающие уровни, после чего данный процессор логически отключается от , вычислительного комплекса и тем самым обеспечивается исключение влияния диагностируемого процессора на рабочую программу, функционирование которой обеспечивается работой системы вычислительного комплекса с участием остальных абонентов. Далее от диагностического носителя сервисного процессора (СП) информация заносится в приемник 6. Затем одновременно на входах 19.1 и 19.2 устанавливаются логические единицы, после чего в соответствии со значениями разрядов приемника 6 возбуждается группа приемников 4 и 5 или 6 и 7. Если 14-й разряд приемника 6 равен .1, то работа осуществляется через входы-выходы 1, если 14-й разряд приемника 6 равен О, то работа осуществляется через входы-выходы 2. Занесением различных комбинаций кодов из тестового набора в приемник 6 возбуждаются группы выходов 20 и 21 или 22 и 23, что обесг- печивает последовательное выполнение каждой команды с последующей проверкой полученных результатов для всего спектра операций, которые присущи данному диагностируемому процессору.

Одной из процедур проверки является определение правильности работы приемников 4 или 6 для ЦП или ПВВ. В этом случае возбуждаются поочередно

выходы этих приемников, используя разряды 1-7, 9 и 10-13 (если п 12), одновременно для каждого примера проверки, обеспечивая разрядами 18-23 приемника 6 равнозначный позиционный вес на первых входах элементов 9 и 10 сравнения. При соответствии значений выходов 17 или 18 эталону блок диагностики переходит к следующему примеру. В противном случае блок диагностики останавливается с точным указанием адреса диагностируемого приемника. В средствах блока диагностики, входящих в СП, предусмотрен специальный счетчик, который инкре- ментируется при каждом случае сравнения выходов диагностируемого процессора с эталоном, который заранее считан с диагностического носителя. При остановке блока диагностики счетчик сравнения указывает номер, а следовательно, и точное место неисправности.

В режиме внешней микродиагностики в процедурах проверки участвуют пары процессоров: СП ЦП, СП- ПВВ, СП- СП, ЦП-ПВВ, ЦП-ЦП, ПВВ-ЦП, . Причем дианостический тестовый набор для любых номеров одноименных процессоров при взаимной диагностике один и тот же. Например, тестовый набор пр при взаимодиагностике ПВВ и ПВВ - ПВВ j один и тот же. Как прави- ло, при выполнении внешней микродиагностики как i-й, так и j-й абоненты взаимодиагностику осуществляют средствами только одной магистрали, поэтому вычислительный комплекс в промежутке микро- диагностики выполняет рабочую прог- грамму средствами другой магистрали без участия 1-го и j-ro процессоров. При этом в средствах рабочих процессоров , занятых процедурой диагнос- тики, номера i и j зарегистрированы как абоненты отсутствующих (отключенных) в конфигурации комплекса. Кроме того, все рабочие процессоры по входу приемников и передатчиков для диагности- руемой магистрали заблокированы, чтобы было исключено влияние избыточных наложений кодов на контролируемых магистралях, а также чтобы магистраль не нарушала работу вычислительного комплекса.

Посредством двух сеансов проверки П.- П- и . микродиагностика выполняет проверку работоспособности

0 5 0

5

0 0 5 Q

5

всех приемников и передатчиков процессоров П; и Hj по рабочим входам с точным указанием места дефектного усилителя, если таковой имеется, а также проверку магистральных шин на предмет отсутствия обрывов, коротких замыканий и корректность цепей согласующих резисторов с указанием точного места неисправного разъема и номера контакта.

Рассмотрим пример взаимной микродиагностики через входы-выходы 2 для сеанса , предполагая, что оба процессора П j и П прошли стадию внутренней диагностики.

В начальный момент в обоих процессорах сбрасываются приемники 6, на входах 19,1-19.6 устанавливаются логические нули, в разрядах (8-23) приемника 6 устанавливается код 000010, где 23-й разряд имитируется четность коммутатора. Далее на входах 19.1- 19.6 устанавливаются соответственно:

в i-м процессоре 0, 1,0, 0, 0,1;

в j-м процессоре 0, 1,0, 1, О, О.

Вследствие такого управления разблокированы только группа передатчи- ков 1 2 в i-м процессоре и группа приемников 6 и 7 в j-м процессоре. В i-м процессоре активизированный выход дешифратора 8 весом один возбудит выход первого передатчика 12. В j-м процессоре первый приемник 6, активизируясь кодом единицы, сравнится с позиционным весом один, выданным дешифратором 8, и поэтому на выходе 18 должен быть код единицы. Состояние выхода 18, - сравниваясь с единичным эталоном блока диагностики, будет инициализировать чтение диагностического набора / для следующего примера проверки.

В случае несовпадения единичного эталона с выходом 18 блок диагностики приостанавливает работу и выдает адрес неисправной шины (см.табл.1).

Переход от первого сеанса взаимной микродиагностики к второму П;- П1 осуществляется новой командой, задаваемой оператором с помощью средств СП.

В табл.2 приведен один из вариантов тестового набора, с помощью которого производится внешняя диагностика шин для обнаружения обрывов, наличия коротких замыканий, наличия . ложных кодов единиц вследствие дефектов приемников и передатчиков.

В этом случае на коммутатор 14 1-го абонента из приемника 6 заносится код нулевого адреса, а входы диагностируемых передатчиков в i-м процессоре и входы диагностируемых приемников j-ro абонента разблокированы, В j-м абоненте к первому, второму, третьему и т.д. входам элемента 9 или 10) сравнения последовательно подводятся через дешифратор 8 веса: один, два, три и т„п. После каждого веса выход соответствующего элемента 9 (или 10) сравнения сравнивается единичным эталоном блока диагностики. Появление любой единицы на выходе элемента сравнения блок диагностики регистрирует как факт наличия неисправности в шине.

Формула изобретения

1. Устройство диагностики многопроцессорного вычислительного комплекса, содержащее первую и вторую группы из 25 п передатчиков в каждой, где п-число процессоров вычислительного комплекса, дешифратор, регистр, первый и второй элементы сравнения и с первой

по четвертую группы из п приемников в каждой, причем выходы передатчиков первой группы объединены с информационными входами приемников первой и второй групп и подкгючены соответственно к информационным входам-выходам

первой грзшпы устройства, выходы пе редатчиков второй L ууппы объединены с информационными входами приемников третьей и четвертой групп и подключены соответственно к информационным входам-выходам второй группы устройства з первый вход режима которого подключен к входам блокировки передатчиков первой группы, второй вход режима устройства подключен к входам блокировки передатчиков второй группы, информационные входы первой группы устройства подключены соответственно к информационным входам регистра, группы выходов дешифратора с первой по n-ю подключены соответственно к информационным входам передатчиков первой группы, к информационным вхо- дам передатчиков второй группы, к входам первой группы первого элемента сравнения и к входам первой группы второго элемента сравнения, выход первого и второго элементов сравнения подключены соответственно к первому к

0

5

0

5

0

5

40

5

0

55

второму выходам признака соответствия эталону устройства, отличающееся тем, что, с целью повышения точности диагностики, оно содержит блок управления и коммутатор, причем выходы первой группы регистра подключены соответственно к первым управляющим входам приемников первой и третьей групп, выходы второй группы регистра подключены соответственно к информационным входам первой группы коммутатора, выходы которого подключены к входам дешифратора, первый, второй и третий выходы регистра подключены соответственно к первому, второму и третьему входам режима блока управления, выходы первой группы которого подключены к первым управляющим входам приемников второй группы, выходы второй группы блока управления подключены к первым управляющим входам приемников четвертой группы, выхо- ды приемников первой группы подключены к входам второй группы первого элемента сравнения и к выходам первой группы устройства для подключения к первой группе входов команд процессора, находящегося в состоянии взаимосвязи, выходы второй группы устройства для подключения к второй группе входов команд процессора, находящегося в состоянии взаимосвязи, подключены к выходам приемников второй группы, выходы приемников третьей группы подключены к входам второй группы второго элемента сравнения и к выходам третьей группы устройства для подключения к третьей группе входов команд процессора, находящегося в состоянии взаимосвязи, выходы четвертой группы устройства для подключения к четвертой группе входов команд процессора, находящегося в состоянии взаимосвязи, подключены к выходам приемников четвертой группы, информационные входы второй группы устройства подключены соответственно к информационным входам второй группы коммутатора, третий и четвертый входы режима и первый вход признака наличия диагностических процедур устройства подключены соответственно к четвертому, пятому и шестому входам режима блока управления, первый выход которого подключен к вторым управляющим входам приемников первой и второй групп, второй вы- ход блока управления подключен к третьим управляющим входам приемкиков первой и второй групп, второй - вход признака наличия диагностических процедур устройства подключен к управляющему входу коммутатора и к Седьмому входу блока управления, - третий выход которого подключен к вторым управляющим входам приемников (третьей и четвертой групп, четвертый выход блока управления подключен к4 третьим управляющим входам приемников третьей и четвертой групп.

2. Устройство по п.1, о т л и ч а ю- щ е е с я тем, что блок управления содержит с первого по четвертый элементы И, первый и второй дешифраторы, причем первый вход блока управления подключен к первому синхровходу первого дешифратора, к первому (инверсному) синхровходу второго дешифратора, к первому (инверсному) входу первого элемента И и к первому входу второго элемента И, второй вход режима блока управления подключен к первым информационным входам первого и второго дешифраторов, третий вход режима блока управления подключен к

0

5

0

5

вторым информационным входам первого и второго дешифраторов, выходы которых подключены соответственно к выходам первой и второй групп блока управления, четвертый и пятый входы режима которого подключены соответст- л- венно к первым входам третьего и четвертого элементов И, выход третьего элемента И подключен к первому выходу блока управления, выход второго элемента И подключен к второму (инверсному) входу третьего элемента И и к второму выходу блока управления, шестой вход режима которого подключен к вторым входам первого и второго элементов И и к вторым входам синхронизации первого и второго дешифраторов, седьмой вход режима блока управления подключен к третьим входам первого и второго элементов И, выход первого элемента И подключен к четвертому выходу блока управления и к второму (инверсному) входу четвертого элемента И, выход которого подключен к третьему выходу блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для диагностики двухмашинного вычислительного комплекса | 1980 |

|

SU959086A1 |

| Устройство для сопряжения каналов ввода-вывода с абонентами | 1986 |

|

SU1406599A2 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1987 |

|

SU1442998A1 |

| Устройство для сопряжения двух процессоров | 1990 |

|

SU1762309A1 |

| Устройство для диагностики эвм | 1976 |

|

SU641453A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| МУЛЬТИПРОЦЕССОРНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1978 |

|

SU768323A1 |

| СПОСОБ ФОРМИРОВАНИЯ ОТКАЗОУСТОЙЧИВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2010 |

|

RU2439674C1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

Изобретение относится к вычислительной технике и может быть использовано для поиска неисправностей в многопроцессорных вычислительных комплексах повышенной надежности. Целью изобретения является повышение точности диагностики. Цель достигается тем, что устройство содержит блок 3 управления, с первой по четвертую группы приемников 4 - 7, дешифратор 8, первый и второй элементы 9 и 10 сравнения, первую и вторую группы передатчиков 11 и 12, регистр 13 и коммутатор 14. 1 з.п. ф-лы, 2 ил., 2 табл.

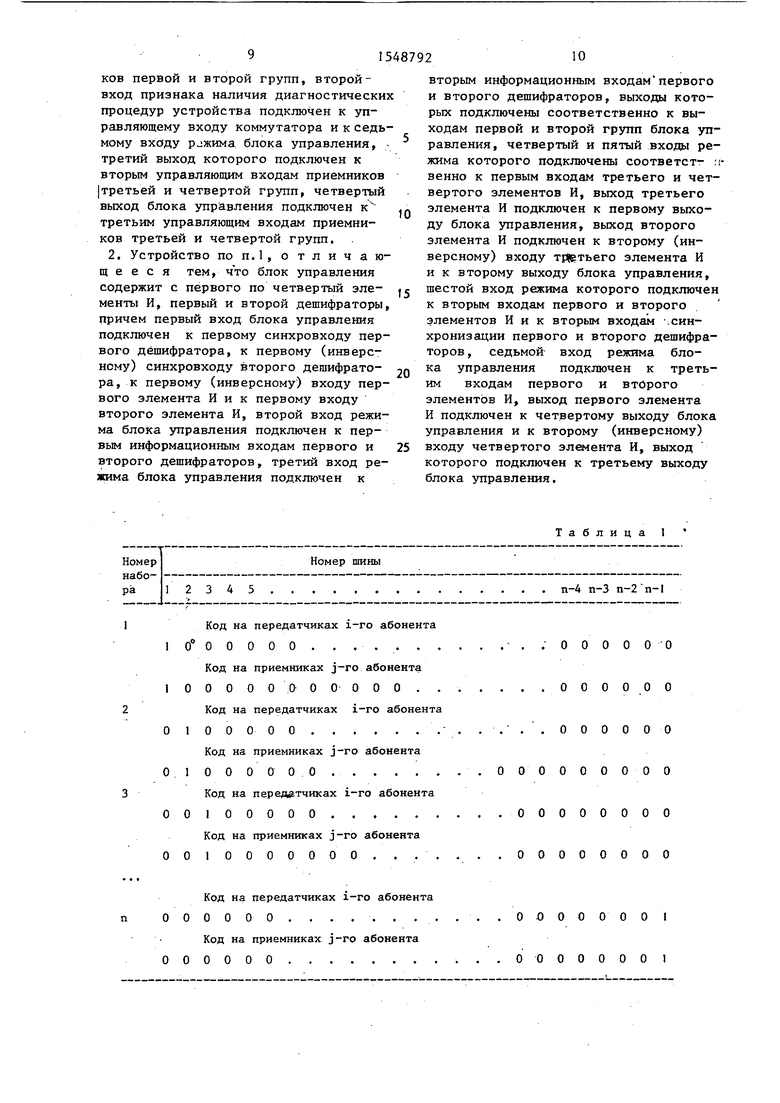

Таблица 1

НомерНомер шины

набо-

ра 1 2 3 4 5n-4 n-3 n-2 n-I

1Код на передатчиках 1-го абонента

io° ооооо . ; о о о о о о

Код на приемниках j-ro абонента 100000000000000000

2Код на передатчиках 1-го абонента

Код на приемниках j-ro абонента 01000000000000000

3Код на передатчиках 1-го абонента

0010000000000000

Код на приемниках j-ro абонента 001000000000000000

Код на передатчиках 1-го абонента

п00000000000001

Код на приемниках j-ro абонента 00000000000001

НомерНомер шины

набо-

ра123456789п-3 п-2 п-Ч

I

1Код на передатчиках 1-го абонента

оооооооооооооооо

2Код на первых входах элементов 9 и 10 сравнения 100000000ООООООО

3010000000...ООООООО

4001000000ООООООО

5000100000ООООООО

6000010000ООООООО

п ООООООООО0000010

nil ООООООООО0000001

J7

38

41

J3v

Фиг. 2

| Устройство для диагностики двухмашинного вычислительного комплекса | 1980 |

|

SU959086A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 4462099, кл | |||

| Гидравлическая передача, могущая служить насосом | 1921 |

|

SU371A1 |

Авторы

Даты

1990-03-07—Публикация

1988-06-06—Подача