Изобретение относится к вычислительной технике и может быть использовано для построения высокопроизводительных многопроцессорных вычислительных систем.

Цель изобретения - повышение производительности обмена

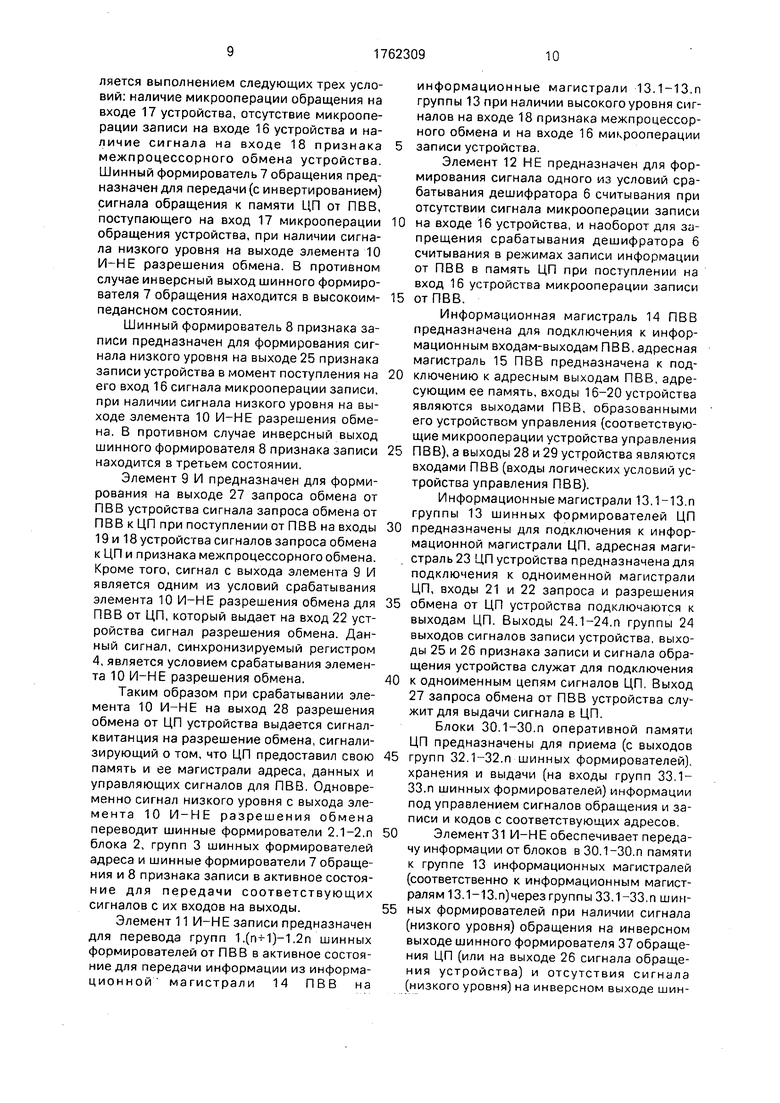

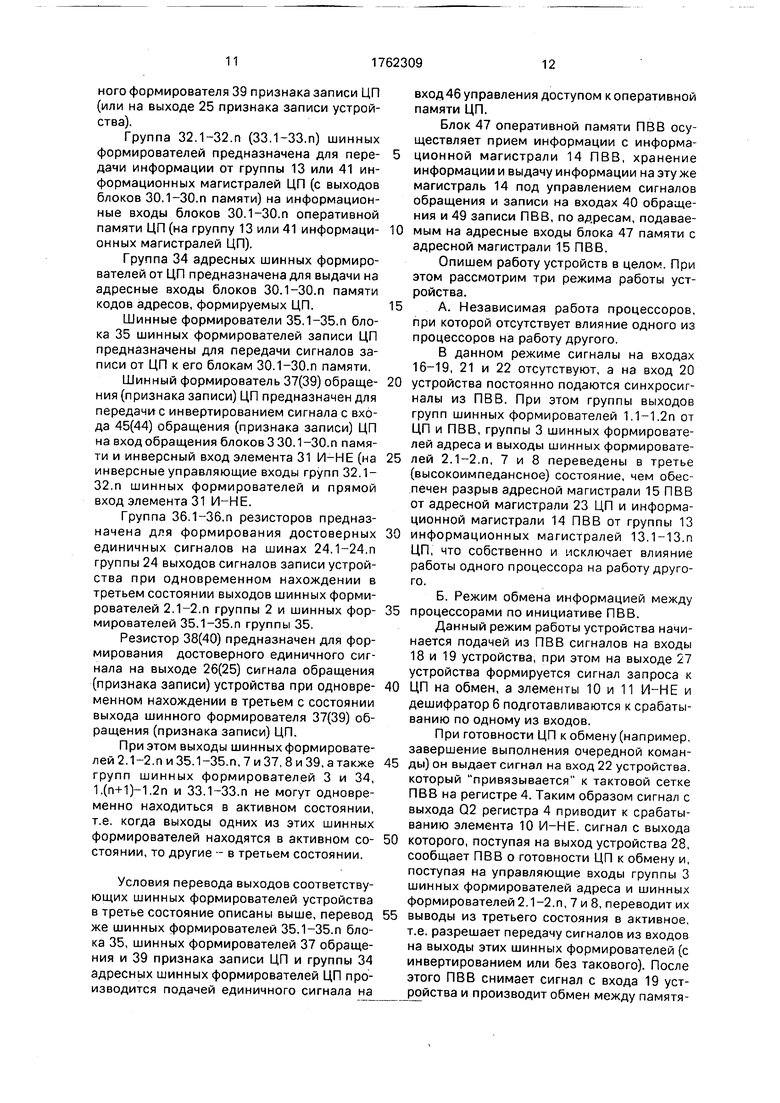

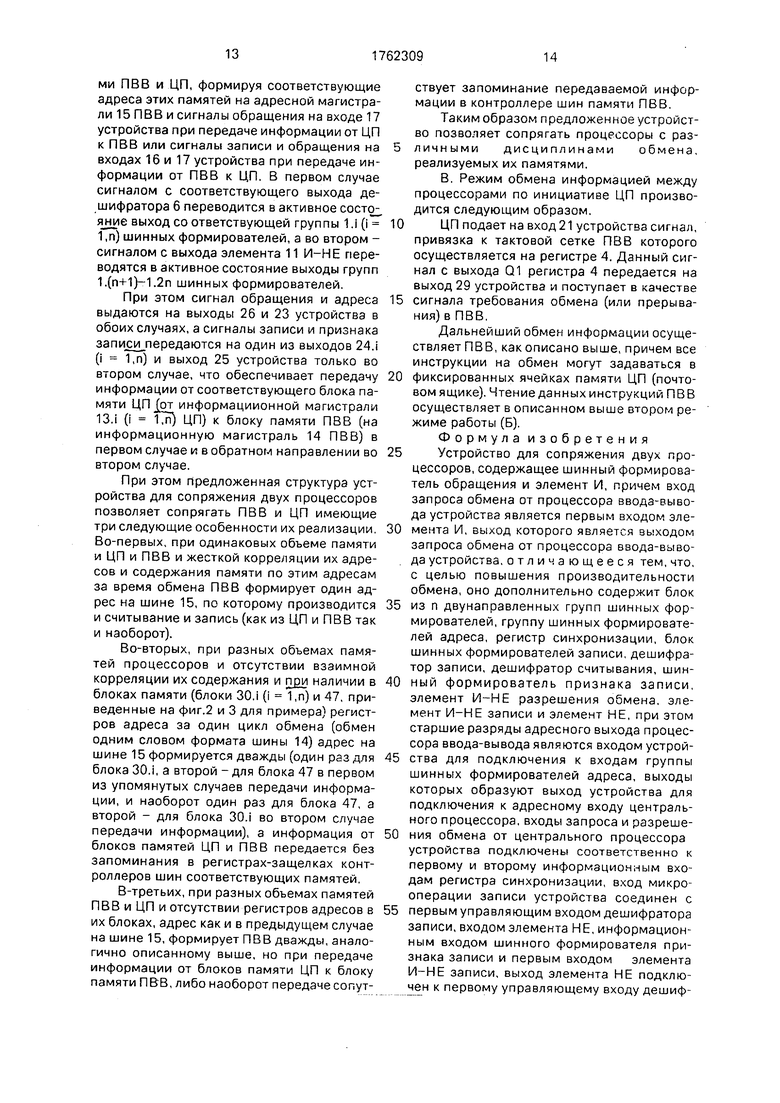

На фиг.1 представлена функциональная схема устройства для сопряжения двух процессоров; на фиг.2 - вариант реализации памяти центрального процессора; на фиг.З - пример реализации памяти процессора ввода-вывода.

Устройство для сопряжения двух процессоров (см. фиг.1) содержит блок 1 двунаправленныхгруппшинныхформирователей состоящих из 1.1-п-й 1.п групп шинных формирователей от ЦП и из первой 1.(п+1)-п-й 1 2п групп шинных формирователей от ПВВ, причем каждая ра групп шинных формирователей (i - 1, п и

п+1,2п соответственно) образует i-ю двунаправленную группу шинных формирователей; блок 2 шинных формирователей записи, включающий первый 2 1-п-й 2 п шинные формирователи записи, группу 3 шинных формирователей адреса; регистр 4 синхронизации, дешифратор 5 записи, дешифратор 6 считывания, шинный формирователь 7 обращения, шинный формирователь 8 признака записи элемент 9 И, элемент 10 И-НЕ разрешения обмена, элемент 11 И-НЕ записи и элемент 12 НЕ

Кроме того, на фиг.1 обозначены группа 13 информационных магистралей ЦП, включающая первую 13.1-п-ю 13.п информационные магистрали; информационная магистраль 14 ПВВ, адресная магистраль 15 ПВВ, вход 16 микрооперации записи устройства, вход 17 микрооперации обращения устройства, вход 18 признака

сл

С

vj

QS

1ЧЭ СА

О

ю

межпроцессорного обмена устройства, вход 19 запроса обмена от ПВВ устройства, синхровход 20 устройства, вход 21 запроса обмена от ЦП устройства, вход 22 разрешения обмена от ЦП устройства, адресная ма- гистраль 23 ЦП; группа 24 выходов сигналов записи, включающая первый 24.1-п-й 24.п выходы сигналов записи; выход 25 признака записи устройства, выход 26 сигнала обращения устройства, выход 27 запроса обмена от ПВВ устройства, выход 28 разрешения обмена от ЦП устройства, выход 29 запроса обмена от ЦП устройства.

Входы-выходы первой группы информационных входов-выходов блока 1 двунап- равленных групп шинных формирователей посредством п информационных магистралей 13.1-13.п подключены к группе 13 информационных магистралей ЦП устройства. Вторая группа информационных входов-вы- ходов блока 1 двунаправленных групп шин- ных формирователей подключена к информационной магистрали 14 ПВВ.

Адресная магистраль 15 ПВВ старшими разрядами через группу 3 шинных форми- рователей адреса подключена к адресной магистрали 23 ЦП.

Вход 21 запроса и вход 22 разрешения обмена от ЦП устройства подключены соответственно к первому Д1 и второму Д2 ин- формационным входам регистра 4 синхронизации, синхровход С которого подключен к синхровходу 20 устройства.

Вход 19 запроса обмена от ПВВ устройства соединен с первым входом элемента 9 И, выход которого соединен с выходом 27 запроса обмена от ПВВ. Вход 16 микрооперации записи устройства соединен с первыми управляющими входами дешифратора 5 записи непосредственно и дешифратора 6 считывания через элемент 12 НЕ, с информационным входом шинного формирователя 8 признака записи и с первым входом элемента 11 И-НЕ записи.

Вход 18 признака межпроцессорного обмена устройства соединен с вторым управляющим входом дешифратора 6 считывания и вторыми входами элемента 9 И и элемента 11 И-НЕ записи.

Первый Q1 и второй Q2 выходы регист- ра 4 синхронизации соединены с выходами 29 запроса обмена от ЦП устройства и первым входом элемента 10 И-НЕ разрешения обмена. Выход элемента 9 И соединен с вторым входом элемента 10 И-НЕ разреше- ния обмена, выход которого подключен к выходу 28 разрешения обмена от ЦП устройства и соединен с инверсными управляющими входами п шинных формирователей (2.1-2.п)записи группы 2, шинных формирователей 7 обращения и 8 признака записи и группы 3 шинных формирователей адреса.

Синхровход 20 устройства соединен с вторым управляющим входом дешифратора 5 записи, инверсные выходы которого через группу информационных входов блока 2 шинных формирователей записи соединены с информационными входами шинных формирователей 2.1-2.П записи группы 2.

Выходы шинных формирователей 2.1- 2,п записи группы 2 соединены с выходами 24.1-24.п сигналов записи группы 24 выходов сигнала записи устройства.

Вход 17 микрооперации обращения устройства соединен с информационным входом шинного формирователя 7 обращения и с третьими управляющими входами дешифраторов 5 записи и 6 считывания.

Младшие разряды адресной магистрали 15 ПВВ соединены с группами информационных входов Д дешифраторов 5 записи и 6 считывания. Инверсные выходы шинных формирователей 7 обращения и 8 признака записи соединены с выходами 26 сигнала обращения и 25 признака записи устройства соответственно.

Инверсные выходы дешифратора 6 считывания с первого по n-й соединены с первого по n-й управляющими входами блока 1 двунаправленных групп шинных формирователей, (п+1)-й управляющий вход которого соединен с выходом элемента 11 И-НЕ записи.

Блок 1 двунаправленных групп шинных формирователей содержит 2п двунаправленных групп шинных формирователей, каждая из которых состоит из группы 1.i (i 1,п) шинных формирователей от ЦП и группы 1.i (i n+1,2n) шинных формирователей от ПВВ.,.

Выходы каждой группы 1.i (I i+1,2n) шинных формирователей от ПВВ соединены с информационными входам соответствующей группы 1.1 (i 1,n) шинных формирователей от ЦП и образует соответствующую информационную магистраль 13,1 (i l7n) группы 13 информационных магистралей ЦП, подключенную к первой группе информационных входов-выходов блока 1 двунаправленных групп шинных формирователей, вторая группа информационных входов-выходов которого соединена с выходами каждой группы 1.i (i 1,n) шинных формирователей и с входами каждой группы 1 .i (i n-И ,2п) шинных формирователей от ПВВ. Управляющие входы блока 1 двунаправленных групп шинных формирователей с первого по n-й соединены с инвер- сными управляющими входами групп шинных формирователей от ЦП с первой 1.1

по n-ю 1.п соответственно. (п+1)-й управляющий вход блока 1 двунаправленных групп шинных формирователей соединен с инверсными управляющими входами всех п групп 1.(п+1)-1.2п шинных формирователей от ПВВ,

Для пояснения принципа работы устройства для сопряжения двух процессоров на фиг.2 приведен пример построения памяти центрального процессора, кратность формата информации которого равна п по отношению к формату информации ПВВ.

Память ЦП (см. фиг.2) представляет собой группу 30 блоков оперативной памяти ЦП, т.е. состоит из i блоков 30i (i 1,п) оперативной памяти, а также содержит элемент 31 И-НЕ считывания; блок 32 информационныхвходныхшинныхформирователей операционной памяти ЦП, состоящей из первой 32.1-п-й 32.п групп шинных формирователей блока; блок 33 информационных выходных шинных формирователей операционной памяти ЦП, состоящей из первой 33.1-п-й 33.п групп шинных формирователей блока; группу 34 адресных шинных формирователей ЦП; блок 35 шинных формирователей записи ЦП, состоящий из первого 35.1-п-го З5.п шинного формирователя записи, выходы каждого из которых через соответствующие резисторы 36.1-36.п подключены к шине питания; шинный формирователь 37 обращения ЦП, инверсный выход которого через резистор 38 подключен к шине питания; шинный формирователь 39 признака записи ЦП, инверсный выход которого через резистор 40 подключен к шине питания. Кроме того на фиг.2 обозначена информационная магистраль 41 ЦП, разрядность которой в п раз больше разрядности каждой из п информационных магистралей 13.i (i 1 ,п) группы 13 информационных магистралей ЦП; группа 42 адресных входов от ЦП; группа 43 входов сигналов записи ЦП, включающая первый 43.1-п-й 43.п входы сигналов записи ЦП,вход 44 признака записи ЦП,вход 45 обращения ЦП и вход 46 управления доступом к оперативной памяти ЦП.

Выходы шинных формирователей 35.1- 35.п записи блока 35 входами соединены с входами 43.1-43.п группы 43 входов, а выходами - к выходам 24.1-24.п группы 24 выходов устройства и к входам записи соответственно блоков 30.1-30.п оперативной памяти ЦП.

Группа 34 адресных шинных формирователей ЦП входами соединена с группой 42 адресных входов от ЦП, а выходами - к адресной магистрали 23 устройства и к адресным входам блоков 30.1-30.п опера шиной памяти ЦП.

Шинный формирователь 3/ „С.ения ЦП входом соединен с входом 45 ооращения ЦП, а инверсным выходом - с входом сигнала обращения устройства, с входами обращения блоков 30.1-30.п памяти и с инверсным входом элемента 31 И-НЕ, выход которого соединен с инверсными управляю0 щими входами групп 33.1-ЗЗ.п шинных формирователей.

Шинный формирователь 39 признака записи ЦП входом соединен с входом 44 признака записи ЦП, а выходом - с выхо5 дом 25 признака записи устройства, с инверсными управляющими входами групп 32.1-32.п шинных формирователей и с прямым входом элемента 31 И-НЕ.

Информационные выходы блоков 30.10 30.п памяти соединены с информационными входами соответственно групп 33.1-33 п шинных формирователей. Выходы групп 32.1-32.п шинных формирователей соединены с информационными входами блоков

5 30.1-30.п памяти соответственно. Выходы групп 33.1-ЗЗ.п шинных формирователей и информационные входы групп 32.1-32.п шинных формирователей соединены попарно между собой и с информационными ма0 гистралями 13.1-13.п группы 13 информационных магистралей ЦП. подключаемой к устройству и к информационной магистрали 41 ЦП.

Вход 46 управления доступом к опера5 тивной памяти ЦП соединен с инверсным управляющими входами шинных формиро вателей 35.1-35.п блока 35, группы 34 адресных шинных формирователей ЦП и шинных формирователей 37 обращения ЦП

0 и 39 признака записи ЦП.

На фиг.З приведен пример блока 47 оперативной памяти ПВВ, который информационными входами-выходами подключен к информационной магистрали 14 ПВВ, а ад5 ресными входами - к адресной магистрали 15 ПВВ. Входы обращения и записи блока 47 оперативной памяти ПВВ подключены к входам 48 обращения и 49 записи от ПВВ соответственно.

0Поскольку разрядность информации

ПВВ кратна рязрядности информации ЦП. то очевидно, что старшие разряды адреса магистрали 15 передаются на выход устройства для выдбора адресов ячеек в блоках 30

5 ЗУ ЦП, а младшие разряды через дешифраторы 5 и 6 обеспечивают работу с соответствующими группами (от первой до п-й) разрядов информации формата ЦП.

Кроме того, поскольку выход 29 запроса обмена от ЦП, аналогичен одноразрядному

выходу 27 запроса обмена от ПВВ, поэтому регистр 4 одноразрядный.

Разрядность информационной магистрали 14 ПВВ кратна разрядности информационной разрядности магистрали ЦП, степень кратности - п, поэтому разрядность магистрали 14 равна разрядности каждой из магистралей 13.1-13.п. При передаче информации от ПВВ к ЦП информация с магистрали 14 передается на каждую из магистралей 13.1...13.П, а в какой из п блоков 30 она будет записана определяют младшие разряды адреса с магистрали 15 с помощью дешифратора 5.

Перед описанием работы устройства в целом опишем назначение и работу отдельных его элементов и узлов, а также элементов и узлов приведенных для примера оперативных памятей ЦП (см. фиг.2) и ПВВ (см. фиг.З),

Блок 1 двунаправленных групп шинных формирователей предназначен для передачи информации от ЦП к ПВВ и наоборот. При передаче информации к ПВВ от ЦП (от информационной магистрали 41 ЦП (см. фиг.2)), т.е. группы 13 информационных магистралей ЦП к информационной магистрали 14 ПВВ выходы только одной из п групп 1.i (i l7n) шинных формирователей от ЦП находятся в активном состоянии, а именно того, который управляется сигналом низкого уровня из одного из п инверсных выходов дешифратора 6 считывания.

При передаче информации от ПВВ к ЦП выходы всех п групп 1.(п+1)-1.2п шинных формирователей от ПВВ находятся в активном состоянии под управлением сигнала низкого уровня с выхода элемента 11 И-НЕ записи. В этом случае информация с информационной магистрали 14 ПВВ поступает на каждую информационную магистраль 13.i (i Tn) группы 13 информационных магистралей ЦП.

В тех же случаях, когда отсутствует пе- (эедача информации от магистралей 13.i (i 1,п) ЦП к магистрали 14 ПВВ или наоборот, что соответствует отсутствию низкого уровня сигналов на инверсных выходах дешифратора 6 считывания и элемента 11 И-НЕ записи, выходы всех групп 1.1-1.2п шинных формирователей блока 1 находятся в третьем (высокоимпедансном) состоянии. При этом работа ЦП и ПВВ протекает параллельно и независимо друг от друга.

Блок 2 шинных формирователей записи предназначен для передачи на группу 24 выходов, т.е. к памяти ЦП низкого уровня сигналов записи от инверсных выходов дешифратора 5 записи, если на выходе элемента 10 И-НЕ сформирован низкий

уровень сигнала. В один и тот же момент времени низкий уровень сигнала записи может передаваться только черкез один из шинных формирователей 2.i (i 1 ,п) блока 2. При

5 высоком уровне сигнала на выходе элемента 10 И-НЕ выходы всех шинных формирователей 2.i (i 1,n) блока 2 находится в третьем, т.е. высокоимпедансном состоянии.

10 Группа 3 шинных формирователей адреса предназначена для передачи кодов адресов с адресной магистрали 15 ПВВ на адресную магистраль ЦП, если на выходе элемента 10 И-НЕ низкий уровень сигнала.

15 В противном случае выходы группы 3 шинных формирователей адреса находятся в высокоимпедансном состоянии.

Регистр4 синхронизации предназначен для синхронизации взаимодействия ЦП и

20 ПВВ, т.е. для привязки появления сигналов ЦП на входах 21 запроса обмена от ЦП и 22 разрешения обмена от ЦП к тактовой сетке ПВВ. Поэтому на синхровход 20 устройства поступает синхросигнал - один из серии

25 тактовых импульсов ПВВ, определяющих тактовые импульсы, синхронизирующие работу ПВВ.

Привязка заключается в восприятии (и соответственно в отсутствии воздействия)

30 устройства этих двух сигналов только в момент переднего фронта синхросигнала, поступающего от ПВВ на синхровход 20 устройства.

Дешифратор 5 записи предназначен

35 для формирования сигнала записи для памяти ЦП (при передаче информации от ПВВ к ЦП) только для части этой памяти, имеющей формат информации, равный формату информации ПВВ. Соответствующая часть

40 (секция) памяти ЦП определяется кодом, заданным в младших разрядах кода адреса на адресной магистрали 15 ПВВ. Сигнал записи (низкий уровень сигнала) на соответствующем инверсном выходе дешифратора 5

45 записи формируются только при выполнении трех условий: наличии микрооперации обращения на входе 17 устройства, микрооперации записи на входе 16 устройства и синхросигнала на синхровходе 20 устройст50 ва.

В противовес дешифратору 5 записи дешифратор 6 считывания предназначен для передачи информации от ЦП к ПВВ. При этом секция магистрали 41 ЦП или секция

55 оперативной памяти ЦП выбираемая для передачи информации от ЦП к ПВВ, задается младшими разрядами кода на адресной магистрали 15 ПВВ, а момента передачи этой информации (открытие одной из групп 1.i (i .n) шинных формирователей ЦП) определяется выполнением следующих трех условий: наличие микрооперации обращения на входе 17 устройства, отсутствие микрооперации записи на входе 16 устройства и наличие сигнала на входе 18 признака межпроцессорного обмена устройства. Шинный формирователь 7 обращения предназначен для передачи (с инвертированием) сигнала обращения к памяти ЦП от ПВВ, поступающего на вход 17 микрооперации обращения устройства, при наличии сигнала низкого уровня на выходе элемента 10 И-НЕ разрешения обмена. В противном случае инверсный выход шинного формирователя 7 обращения находится в высокоим- педансном состоянии.

Шинный формирователь 8 признака записи предназначен для формирования сигнала низкого уровня на выходе 25 признака записи устройства в момент поступления на его вход 16 сигнала микрооперации записи, при наличии сигнала низкого уровня на выходе элемента 10 И-НЕ разрешения обмена. В противном случае инверсный выход шинного формирователя 8 признака записи находится в третьем состоянии.

Элемент 9 И предназначен для формирования на выходе 27 запроса обмена от ПВВ устройства сигнала запроса обмена от ПВВ к ЦП при поступлении от ПВВ на входы 19 и 18 устройства сигналов запроса обмена к ЦП и признака межпроцессорного обмена. Кроме того, сигнал с выхода элемента 9 И является одним из условий срабатывания элемента 10 И-НЕ разрешения обмена для ПВВ от ЦП, который выдает на вход 22 устройства сигнал разрешения обмена. Данный сигнал, синхронизируемый регистром 4, является условием срабатывания элемента 10 И-НЕ разрешения обмена.

Таким образом при срабатывании элемента 10 И-НЕ на выход 28 разрешения обмена от ЦП устройства выдается сигнал- квитанция на разрешение обмена, сигнализирующий о том, что ЦП предоставил свою память и ее магистрали адреса, данных и управляющих сигналов для ПВВ. Одновременно сигнал низкого уровня с выхода элемента 10 И-НЕ разрешения обмена переводит шинные формирователи 2.1-2.П блока 2, групп 3 шинных формирователей адреса и шинные формирователи 7 обращения и 8 признака записи в активное состояние для передачи соответствующих сигналов с их входов на выходы.

Элемент 11 И-НЕ записи предназначен для перевода групп 1.(п+1)-1.2п шинных формирователей от ПВВ в активное состояние для передачи информации из информационной магистрали 14 ПВВ на

информационные магистрали 13.1-13.п группы 13 при наличии высокого уровня сигналов на входе 18 признака межпроцессорного обмена и на входе 16 микрооперации записи устройства.

Элемент 12 НЕ предназначен для формирования сигнала одного из условий срабатывания дешифратора 6 считывания при отсутствии сигнала микрооперации записи на входе 16 устройства, и наоборот для запрещения срабатывания дешифратора 6 считывания в режимах записи информации от ПВВ в память ЦП при поступлении на вход 16 устройства микрооперации записи от ПВВ.

Информационная магистраль 14 ПВВ предназначена для подключения к информационным входам-выходам ПВВ, адресная магистраль 15 ПВВ предназначена к подключению к адресным выходам ПВВ, адресующим ее память, входы 16-20 устройства являются выходами ПВВ, образованными его устройством управления (соответствующие микрооперации устройства управления ПВВ), а выходы 28 и 29 устройства являются входами ПВВ (входы логических условий устройства управления ПВВ).

Информационные магистрали 13.1-13.ri группы 13 шинных формирователей ЦП предназначены для подключения к информационной магистрали ЦП, адресная магистраль 23 ЦП устройства предназначена для подключения к одноименной магистрали ЦП, входы 21 и 22 запроса и разрешения обмена от ЦП устройства подключаются к выходам ЦП. Выходы 24.1-24.п группы 24 выходов сигналов записи устройства, выходы 25 и 26 признака записи и сигнала обращения устройства служат для подключения к одноименным цепям сигналов ЦП. Выход 27 запроса обмена от ПВВ устройства служит для выдачи сигнала в ЦП.

Блоки 30.1-30.п оперативной памяти ЦП предназначены для приема (с выходов групп 32.1-32.п шинных формирователей), хранения и выдачи (на входы групп 33.1- 33.п шинных формирователей) информации под управлением сигналов обращения и записи и кодов с соответствующих адресов.

Элемент31 И-НЕ обеспечивает передачу информации от блоков в 30.1-30.п памяти к группе 13 информационных магистралей (соответственно к информационным магистралям 13.1-13.п)через группы 33.1-33.п шинных формирователей при наличии сигнала (низкого уровня) обращения на инверсном выходе шинного формирователя 37 обращения ЦП (или на выходе 26 сигнала обращения устройства) и отсутствия сигнала (низкого уровня) на инверсном выходе шинного формирователя 39 признака записи ЦП (или на выходе 25 признака записи устройства).

Группа 32.1-32.п (33.1-33.п) шинных формирователей предназначена для передачи информации от группы 13 или 41 информационных магистралей ЦП (с выходов блоков 30.1-30.п памяти) на информационные входы блоков 30.1-ЗО.п оперативной памяти ЦП (на группу 13 или 41 информационных магистралей ЦП).

Группа 34 адресных шинных формирователей от ЦП предназначена для выдачи на адресные входы блоков 30.1-ЗО.п памяти кодов адресов, формируемых ЦП.

Шинные формирователи 35.1-35.п блока 35 шинных формирователей записи ЦП предназначены для передачи сигналов записи от ЦП к его блокам 30.1-ЗО.п памяти.

Шинный формирователь 37(39) обращения (признака записи) ЦП предназначен для передачи с инвертированием сигнала с входа 45(44) обращения (признака записи) ЦП на вход обращения блоков 3 30.1-ЗО.п памяти и инверсный вход элемента 31 И-НЕ (на инверсные управляющие входы групп 32.1- 32.п шинных формирователей и прямой вход элемента 31 И-НЕ.

Группа 36.1-36.п резисторов предназначена для формирования достоверных единичных сигналов на шинах 24.1-24.п группы 24 выходов сигналов записи устройства при одновременном нахождении в третьем состоянии выходов шинных формирователей 2.1-2.П группы 2 и шинных формирователей 35.1-35.п группы 35.

Резистор 38(40) предназначен для формирования достоверного единичного сигнала на выходе 26(25) сигнала обращения (признака записи) устройства при одновременном нахождении в третьем с состоянии выхода шинного формирователя 37(39) обращения (признака записи) ЦП.

При этом выходы шинных формирователей 2.1-2.П и 35.1-35.п, 7 и 37, 8 и 39, а также групп шинных формирователей 3 и 34, 1.(п+1)-1.2п и 33.1-33.п не могут одновременно находиться в активном состоянии, т.е. когда выходы одних из этих шинных формирователей находятся в активном состоянии, то другие - в третьем состоянии.

Условия перевода выходов соответствующих шинных формирователей устройства в третье состояние описаны выше, перевод же шинных формирователей 35.1-35.п блока 35, шинных формирователей 37 обращения и 39 признака записи ЦП и группы 34 адресных шинных формирователей ЦП производится подачей единичного сигнала на

вход 46 управления доступом к оперативной памяти ЦП.

Блок 47 оперативной памяти ПВВ осуществляет прием информации с информационной магистрали 14 ПВВ, хранение информации и выдачу информации на эту же магистраль 14 под управлением сигналов обращения и записи на входах 40 обращения и 49 записи ПВВ, по адресам, подаваемым на адресные входы блока 47 памяти с адресной магистрали 15 ПВВ.

Опишем работу устройств в целом. При этом рассмотрим три режима работы устройства.

А. Независимая работа процессоров, при которой отсутствует влияние одного из процессоров на работу другого.

В данном режиме сигналы на входах 16-19, 21 и 22 отсутствуют, а на вход 20

устройства постоянно подаются синхросигналы из ПВВ. При этом группы выходов групп шинных формирователей 1.1-1.2п от ЦП и ПВВ, группы 3 шинных формирователей адреса и выходы шинных формирователей 2.1-2.П, 7 и 8 переведены в третье (высокоимпедансное) состояние, чем обеспечен разрыв адресной магистрали 15 ПВВ от адресной магистрали 23 ЦП и информационной магистрали 14 ПВВ от группы 13

информационных магистралей 13.1-13.п ЦП, что собственно и исключает влияние работы одного процессора на работу другого.

Б. Режим обмена информацией между

процессорами по инициативе ПВВ.

Данный режим работы устройства начинается подачей из ПВВ сигналов на входы 18 и 19 устройства, при этом на выходе 27 устройства формируется сигнал запроса к

ЦП на обмен, а элементы 10 и 11 И-НЕ и дешифратор 6 подготавливаются к срабатыванию по одному из входов.

При готовности ЦП к обмену (например, завершение выполнения очередной команды) он выдает сигнал на вход 22 устройства, который привязывается к тактовой сетке ПВВ на регистре 4. Таким образом сигнал с выхода Q2 регистра 4 приводит к срабатыванию элемента 10 И-НЕ. сигнал с выхода

которого, поступая на выход устройства 28, сообщает ПВВ о готовности ЦП к обмену и, поступая на управляющие входы группы 3 шинных формирователей адреса и шинных формирователей 2.1-2.п, 7 и 8, переводит их

выводы из третьего состояния в активное, т.е. разрешает передачу сигналов из входов на выходы этих шинных формирователей (с инвертированием или без такового). После этого ПВВ снимает сигнал с входа 19 устройства и производит обмен между памятями ПВВ и ЦП, формируя соответствующие адреса этих памятей на адресной магистрали 15 ПВВ и сигналы обращения на входе 17 устройства при передаче информации от ЦП к ПВВ или сигналы записи и обращения на входах 16 и 17 устройства при передаче информации от ПВВ к ЦП. В первом случае сигналом с соответствующего выхода дешифратора 6 переводится в активное состо яние выход со ответствующей группы 1.1 (i 1 ,п) шинных формирователей, а во втором - сигналом с выхода элемента 11 И-НЕ переводятся в активное состояние выходы групп 1.(п+1)-1.2п шинных формирователей.

При этом сигнал обращения и адреса выдаются на выходы 26 и 23 устройства в обоих случаях, а сигналы записи и признака записи передаются на один из выходов 24.i (i 1,n) и выход 25 устройства только во втором случае, что обеспечивает передачу информации от соответствующего блока памяти ЦП Ът информациионной магистрали 13.i (i Ът) ЦП) к блоку памяти ПВВ (на информационную магистраль 14 ПВВ) в первом случае и в обратном направлении во втором случае.

При этом предложенная структура устройства для сопряжения двух процессоров позволяет сопрягать ПВВ и ЦП имеющие три следующие особенности их реализации. Во-первых, при одинаковых объеме памяти и ЦП и ПВВ и жесткой корреляции их адресов и содержания памяти по этим адресам за время обмена ПВВ формирует один адрес на шине 15, по которому производится и считывание и запись (как из ЦП и ПВВ так и наоборот).

Во-вторых, при разных объемах памятей процессоров и отсутствии взаимной корреляции их содержания и гщи наличии в блоках памяти (блоки 30.i (i 1,n) и 47, приведенные на фиг.2 и 3 для примера) регистров адреса за один цикл обмена (обмен одним словом формата шины 14) адрес на шине 15 формируется дважды (один раз для блока 30.i, а второй - для блока 47 в первом из упомянутых случаев передачи информации, и наоборот один раз для блока 47, а второй - для блока 30.i во втором случае передачи информации), а информация от блоков памятей ЦП и ПВВ передается без запоминания в регистрах-защелках контроллеров шин соответствующих памятей.

В-третьих, при разных объемах памятей ПВВ и ЦП и отсутствии регистров адресов в их блоках, адрес как и в предыдущем случае на шине 15, формирует ПВВ дважды, аналогично описанному выше, но при передаче информации от блоков памяти ЦП к блоку памяти ПВВ, либо наоборот передаче сопутствует запоминание передаваемой информации в контроллере шин памяти ПВВ.

Таким образом предложенное устройство позволяет сопрягать процессоры с различными дисциплинами обмена, реализуемых их памятями.

В. Режим обмена информацией между процессорами по инициативе ЦП производится следующим образом.

0 ЦП подает на вход 21 устройства сигнал, привязка к тактовой сетке ПВВ которого осуществляется на регистре 4. Данный сигнал с выхода Q1 регистра 4 передается на выход 29 устройства и поступает в качестве

5 сигнала требования обмена (или прерывания) в ПВВ.

Дальнейший обмен информации осуществляет ПВВ, как описано выше, причем все инструкции на обмен могут задаваться в

0 фиксированных ячейках памяти ЦП (почтовом ящике). Чтение да иных инструкций ПВВ осуществляет в описанном выше втором режиме работы (Б).

Формула изобретения

5 Устройство для сопряжения двух процессоров, содержащее шинный формирователь обращения и элемент И, причем вход запроса обмена от процессора ввода-вывода устройства является первым входом эле0 мента И, выход которого является выходом запроса обмена от процессора ввода-вывода устройства, отличающееся тем, что, с целью повышения производительности обмена, оно дополнительно содержит блок

5 из п двунаправленных групп шинных формирователей, группу шинных формирователей адреса, регистр синхронизации, блок шинных формирователей записи, дешифратор записи, дешифратор считывания, шин0 ный формирователь признака записи, элемент И-НЕ разрешения обмена, элемент И-НЕ записи и элемент НЕ, при этом старшие разряды адресного выхода процессора ввода-вывода являются входом устрой5 ства для подключения к входам группы шинных формирователей адреса, выходы которых образуют выход устройства для подключения к адресному входу центрального процессора, входы запроса и разреше0 ния обмена от центрального процессора устройства подключены соответственно к первому и второму информационным входам регистра синхронизации, вход микрооперации записи устройства соединен с

5 первым управляющим входом дешифратора записи, входом элемента НЕ, информационным входом шинного формирователя признака записи и первым входом элемента И-НЕ записи, выход элемента НЕ подключен к первому управляющему входу дешифратора считывания, синхровход устройства, образуемый тактовым синхронизирующим выходом процессора ввода-вывода, соединен с синхровходом регистра синхронизации и вторым управляющим входом дешифратора записи, вход признака межпроцессорного обмена устройства соединен с вторым управляющим входом дешифратора считывания и вторыми входами элемента И и элемента И-НЕ записи, первый выход регистра синхронизации является выходом запроса обмена от центрального процессора устройства, второй выход регистра синхронизации, соединен с первым входом элемента И-НЕ разрешения обмена, выход элемента И соединен с вторым входом элемента И-НЕ разрешения обмена, выход которого является выходом разрешения обмена от центрального процессора устройства и соединен с инверсны- ми управляющими входами шинных формирователей записи группы, шинных формирователей обращения и признака записи и шинных формирователей адреса группы, инверсные выходы дешифратора записи соединены с информационными входами шинных формирователей записи группы, выходы шинных формирователей записи группы являются выходами сигналов записи группы выходов сигналов записи устройства, вход микрооперации обращения устройства соединен с информационным входом шинного формирователя обращения и третьими управляющими входами дешифраторов записи и считывания, младшие разряды адресного выхода процессора ввода-вывода являются входами устройства для подключения к группам информационных входов дешифраторов записи и считывания, инверсные выходы шинных формирователей обращения и признака записи образуют выходы сигнала обращения и признака записи устройства соответственно, инверсные выходы дешифратора считывания с первого по n-й соединены с инверсными управляющими входами групп шинных формирователей с первой по п-ую блока двунаправленных групп шинных формирователей, инверсные управляющие входы групп шинных формирователей с (п+1)-й по 2п-ю этого же блока соединены с выходом элемента И-НЕ записи, информационные входы i-й группы (1 i п) шинных

формирователей блока двунаправленных шинных формирователей соединены с выходами (гЖ)-й группы шинных формирователей этого же блока и образуют информационный вход-выход устройства

для подключения к информационному входу-выходу центрального процессора, выходы i-й группы шинных формирователей блока двунаправленных групп шинных формирователей соединены с информационными входами (п-Н)-й группы шинных формирователей того же блока и образуют информационный вход-выход устройства для подключения к информационному входу-выходу процессора ввода-вывода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Устройство для контроля и перезапуска ЭВМ | 1987 |

|

SU1464162A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| МИКРОЭВМ | 1994 |

|

RU2108619C1 |

| Специализированный процессор | 1990 |

|

SU1705834A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения высокопроизводительных многопроцессорных вычислительных систем Целью изобретения является повышение производительности обмена С этой целью в устройство, содержащее шинный формирователь обращения и элемент И, введены блок из п двунаправленных групп шинных формирователей, группу шинных формирователей адреса, регистр синхронизации, блок шинных формирователей записи, дешифратор записи, дешифратор считывания, шинный формирователь признака записи элемент И-НЕ разрешения обмена, элемент И-НЕ записи и элемент- НЕ 3 ил

| Система доступа к памяти | 1983 |

|

SU1151974A1 |

| Устройство для сопряжения двух процессоров через общую память | 1985 |

|

SU1287167A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-09-15—Публикация

1990-03-11—Подача