Изобретение относится к вычислительной технике и может быть использовано для обнаружения и локализации неисправностей блоков ЭВМи

Цель изобретения - расширение области применения устройства

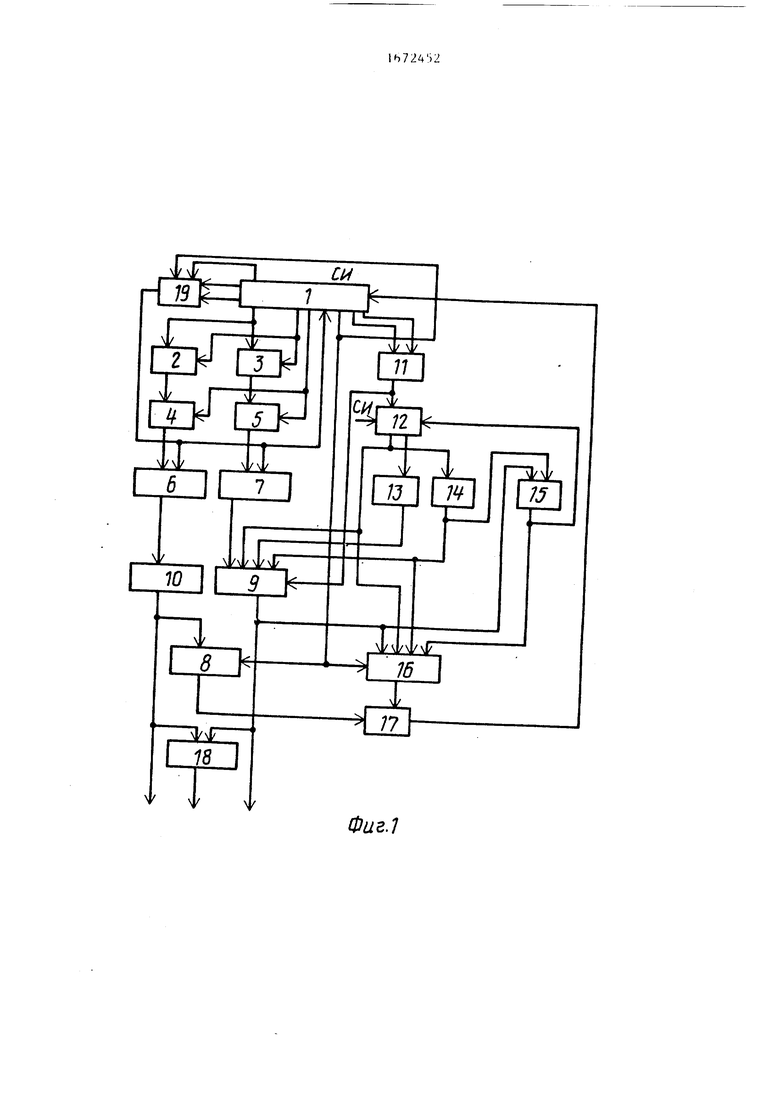

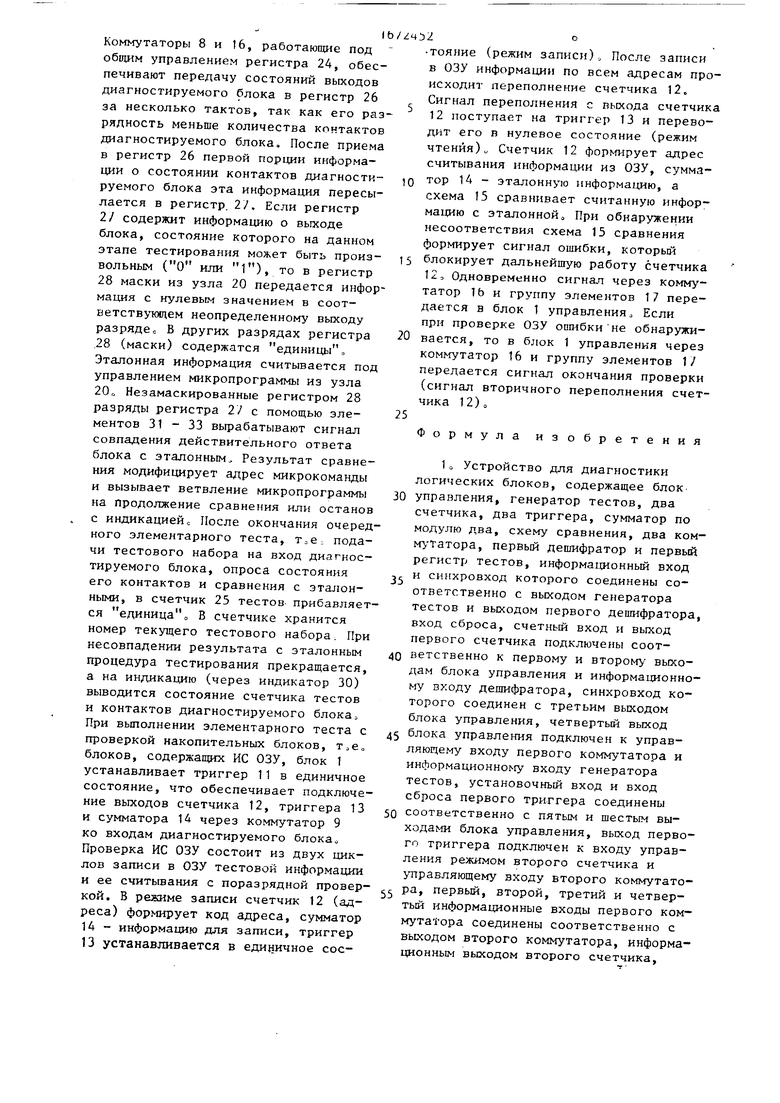

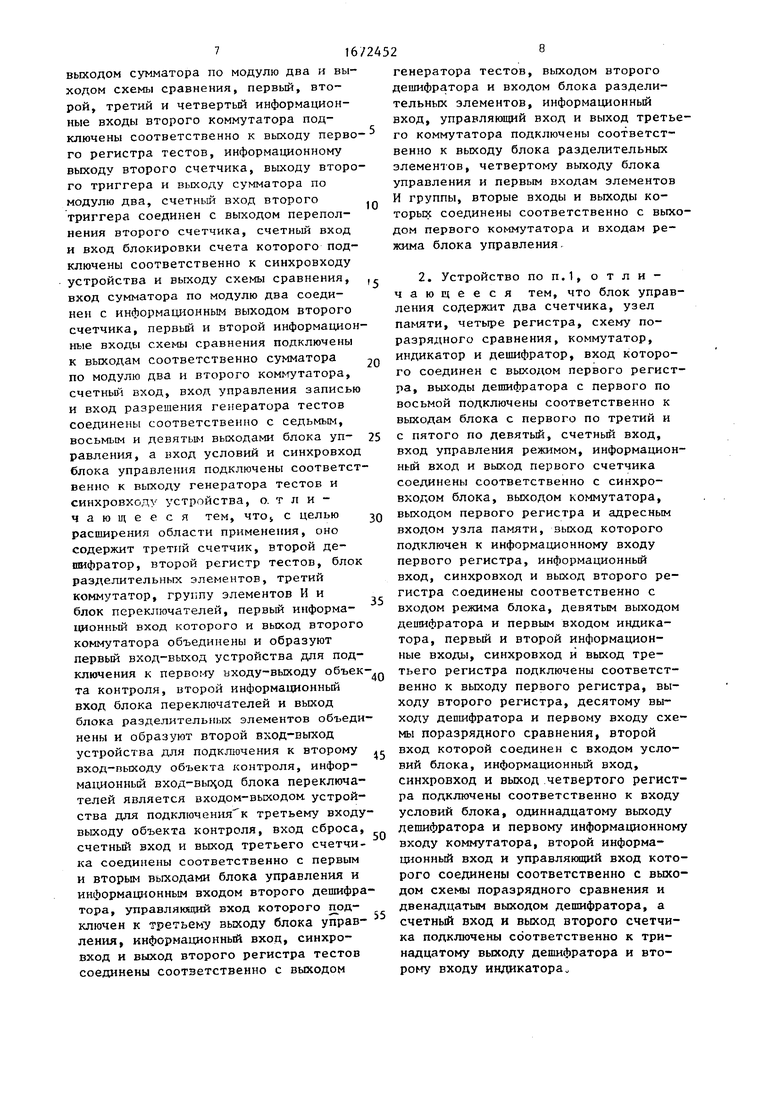

На фиго1 представлена структурная схема устройства; на фиг„2 - функциональная схема блока управления и генератора тестов„

Устройство содержит (см. фиг.,1) блок 1 управления, счетчики 2 и 3, дешифраторы 4 и 5, регистры тестов 6 и /, коммутаторы 8 и 9, блок 10 разделительных элементов (с открытым коллектором), триггер 11, счетчик 12, триггер 13, сумматор по модулю два 14, схему 15 сравнения, коммутатор 16, группу элементов И 17, блок 18 переключателей и генератор 19 тестов.В состав генератора 19 тестов (см. фиг.2) входят узел 20 памяти

тестов и счетчик 21, а блок 1 управления содержит счетчик 22, узел 23 памяти, регистр 24, счетчик 25, регистры 26 - 28, дешифратор 29, индикатор 30, схему 31 поразрядного сравнения, группу элементов И 32 и элемент ИЛИ 33, образующие коммутатор j В зависимости от применяемых в диагностируемом блоке элементов (ЭСЛ или ТТЛ) он подключается к первому или второму входу-выходу устройства„ Если в диагностируемом блоке использованы элементы как ЭСЛ, так и ТТЛ, для его проверки в устройство вставляется соответствующий блок 18, а диагностируемый блок подключается к третьему вход-выходу устройства, Блок 18 обеспечивает подключение в зависимости от типа логики (ЭСЛ или ТТЛ), связанного с внешним контактом диагностируемого блока, либо к соответствующему выходу блока 10, либо

00

с

о

XJ

го

-N ел го

3

к соответствующему выходу коммутатора 9. Алгоритм работы устройства одинаков для диагностирования блоков, подключаемых к каждому из трех его выходов Диагностические тесты блоков размещаются в узле 20 памяти (см., фиг, 2) с Микропрограммы, обеспечивающие подачу тестов на вход диагностируемого блока, и анализ его ответов путем опроса состояния выходов блока и сравнения их с эталонными размещаются в узле 23 памяти ) тестов о

Работа устройства начинается с нажатия кнопки Пуск, В результате начальный (нулевой) адрес микропрограммы заносится в счетчик 22 (адреса) и сбрасывает счетчик 25„ После этого начинается последовательное считывание из узла 23 в регистр 24 (микрокоманд) и их выполнение. Регистр 24 имеет поле констант и поле микроопе

раций Дешифрация микроопераций производится в дешифраторе 2yt Под управлением одной из микроопераций информация из поля константы регистра 24 поступает в счетчик 21 (адреса), задавая начальный адрес тестов про10

считанного из узла 20 эталона служебного кода с заданным в регистре 2/ выполняется ветвление микропрограммы путем модификации адреса в счетчике 22. Выполнение одного элементарного теста проверяемого блока сводится к подаче на его вход тестового набора, опроса результата и сравнения его с эталонным. Подача тестового набора на вход диагностируемого блока выполняется следующим образом После сброса счетчиков 2 и 3 (см, фиг.,1), триггера 11 и модификации адреса в счетчике 21 (фиг„2) на единицу из узла 20 считывается информация и передается в регистры 6 и / тестов под управлением соответственно счетчика 2 и дешифратора 4, счетчика 3 и дешифратора 5, После установки первой порции информации из узла 20 в регистры 6 и / микропрограммно прибавляется единица в счетчики 2 и 3 и засылается следую- 25 щая информация в другую группу разрядов регистров 6 и /. Так происходит до тех пор, пока регистры 6 и 7 не будут заполнены тестовым набором,, Нулевое состояние триггера 11 обес15

20

веряемого блока. Под управлением дру- 3Qпечивает передачу тестового набора с

гих микроопераций информация из узлавыхода регистра / через коммутатор 9

20 считывается и передается в соот-на первый вход-выход устройства и

ветствующие регистры. Информация тес-вход блока 18. Тестовый набор с вытов в узле 20 памяти записывается входа регистра 6 тестов поступает чеследующем порядке. Перед каждым тес-Рсз блок 10 на второй вход-выход ycr

товьи; набором, занимающим фиксирован- ройства и на вход блока 18. Для каж- ное количество байтов в узле 20, записывается служебный код, который определяет тип тестового набора, с

дого элементарного теста содержимое регистров тестов 6 и / идентично и содержит тестовые воздействия для

проверкой интегральных схем (ИС) ОЗУ 4Q входов и единицы „для выходов диаг- или без нее о За тестовым набором еле- ностируемого . Состояния выходов дует эталонная информация о состоянии диагностируемого блока опрашиваются исправного блока на тестовом наборе микропрограммно через коммутаторы 8, и информация, указывающая выходы ди- 16 и группу элементов 1/. МОНТАЖНОЕ И, агностируемого блока, состояние кото-45 образованное для выходных контактов

рых на данном тестовом напоре может быть произвольным (О или 1)с Анализ служебного кода выполняется путем пересылки его из поля константы регистра 24 в регистр 27, передачей маски (на данном шаге единицы) из узла 20 в регистр 28 (маски), считыванием эталона служебного кода из узла 20 и его сравнения с содержимым регистра 27 в схеме 31 поразрядного сравнения Благодаря единичному значению регистра 28 маски сигнал сравнения через элемент 32 поступает на выход элемента 33 При совпадении

проверяемого блока, с единичными значениями, поступающими от коммутатора 9 и блока 10, обеспечивает на входе коммутаторов 8 (16) реальные значения сигналов проверяемого блока,

Независимо от того, к какому из трех входов-выходов устройства подключен диагностируемый блок, состояние его выходных контактов передается через коммутатор 8 (16) и группу элемен 5 тов 17 в регистр 26, так как в разрядах регистров 6 и 7, соответствующих выходным контактам диагностируемого блока, содержатся единицы „

10

6/2452Л

считанного из узла 20 эталона служебного кода с заданным в регистре 2/ выполняется ветвление микропрограммы путем модификации адреса в счетчике 22. Выполнение одного элементарного теста проверяемого блока сводится к подаче на его вход тестового набора, опроса результата и сравнения его с эталонным. Подача тестового набора на вход диагностируемого блока выполняется следующим образом После сброса счетчиков 2 и 3 (см, фиг.,1), триггера 11 и модификации адреса в счетчике 21 (фиг„2) на единицу из узла 20 считывается информация и передается в регистры 6 и / тестов под управлением соответственно счетчика 2 и дешифратора 4, счетчика 3 и дешифратора 5, После установки первой порции информации из узла 20 в регистры 6 и / микропрограммно прибавляется единица в счетчики 2 и 3 и засылается следую- 25 щая информация в другую группу разрядов регистров 6 и /. Так происходит до тех пор, пока регистры 6 и 7 не будут заполнены тестовым набором,, Нулевое состояние триггера 11 обес15

20

входов и единицы „для выходов диаг- ностируемого . Состояния выходов диагностируемого блока опрашиваются микропрограммно через коммутаторы 8, 16 и группу элементов 1/. МОНТАЖНОЕ И образованное для выходных контактов

проверяемого блока, с единичными значениями, поступающими от коммутатора 9 и блока 10, обеспечивает на входе коммутаторов 8 (16) реальные значения сигналов проверяемого блока,

Независимо от того, к какому из трех входов-выходов устройства подключен диагностируемый блок, состояние его выходных контактов передается через коммутатор 8 (16) и группу элементов 17 в регистр 26, так как в разрядах регистров 6 и 7, соответствующих выходным контактам диагностируемого блока, содержатся единицы „

Коммутаторы 8 и 16, работающие под общим управлением регистра 24, обеспечивают передачу состояний выходов диагностируемого блока в регистр 26 за несколько тактов, так как его разрядность меньше количества контактов диагностируемого блока. После приема в регистр 26 первой порции информации о состоянии контактов диагностируемого блока эта информация пересылается в регистр. 2/, Если регистр 2/ содержит информацию о выходе блока, состояние которого на данном этапе тестирования может быть произвольным (О или 1), то в регистр 28 маски из узла 20 передается информация с нулевым значением в соответствующем неопределенному выходу разряде,: В других разрядах регистра 28 (маски) содержатся единицы., Эталонная информация считывается под управлением микропрограммы из узла 200 Незамаскированные регистром 28 разряды регистра 21 с помощью элементов 31-33 вырабатывают сигнал совпадения действительного ответа блока с эталонным Результат сравнения модифицирует адрес микрокоманды и вызывает ветвление микропрограммы на Продолжение сравнения или останов с индикацией После окончания очередного элементарного теста, тае подачи тестового набора на вход диагностируемого блока, опроса состояния его контактов и сравнения с эталонными, в счетчик 25 тестов прибавляется единица В счетчике хранится номер текущего тестового набора. При несовпадении результата с эталонным процедура тестирования прекращается, а на индикацию (через индикатор 30) выводится состояние счетчика тестов и контактов диагностируемого блока. При выполнении элементарного теста с проверкой накопительных блоков, т0е0 блоков, содержащих ИС ОЗУ, блок 1 устанавливает триггер 11 в единичное состояние, что обеспечивает подключение выходов счетчика 12, триггера 13 и сумматора 14 через коммутатор 9 ко входам диагностируемого блока„ Проверка ИС ОЗУ состоит из двух циклов записи в ОЗУ тестовой информации и ее считывания с поразрядной проверкой. В режиме записи счетчик 12 (адреса) формирует код адреса, сумматор 14 - информацию для записи, триггер 13 устанавливается в единичное сос тояние (режим записи) ., После записи в ОЗУ информации по всем адресам происходит переполнение счетчика 12. Сигнал переполнения с выхода счетчика 12 поступает на триггер 13 и переводит его в нулевое состояние (режим чтения)„ Счетчик 12 формирует адрес считывания информации из ОЗУ, суммзтор 14 - эталонную информацию, а

схема 15 сравнивает считанную информацию с эталонной При обнаружении несоответствия схема 15 сравнения формирует сигнал ошибки, который

5 блокирует дальнейшую работу счетчика 12, Одновременно сигнал через коммутатор 16 и группу элементов 17 передается в блок 1 управления о Если при проверке ОЗУ ошибки не обнаруживается, то в блок 1 управления через коммутатор 16 и группу элементов 1/ передается сигнал окончания проверки (сигнал вторичного переполнения счетчика 12) о

5

Формула изобретения

1 о Устройство для диагностики логических блоков, содержащее блок 0 управления, генератор тестов, два счетчика, два триггера, сумматор по модулю два, схему сравнения, два коммутатора, первый дешифратор и первый регистр тестов, информационный вход

35

и синхровход которого соединены соответственно с выходом генератора тестов и выходом первого дешифратора, вход сброса, счетный вход и выход первого счетчика подключены соответственно к первому и второму выходам блока управления и информационному входу дешифратора, синхровход которого соединен с третьим выходом блока управления, четвертый выход

блока управления подключен к управляющему входу первого коммутатора и информационному входу генератора тестов, установочный вход и вход сброса первого триггера соединены

соответственно с пятым и шестым выходами блока управления, выход первого триггера подключен к входу управления режимом второго счетчика и управляющему входу второго коммутатора, первый, второй, третий и четвертый информационные входы первого коммутатора соединены соответственно с выходом второго коммутатора, информационным выходом второго счетчика,

716

выходом сумматора по модулю два и выходом схемы сравнения, первый, второй, третий и четвертый информационные входы второго коммутатора под

ключены соответственно к выходу перво го регистра тестов, информационному выходу второго счетчика, выходу второго триггера и выходу сумматора по модулю два, счетный вход второго триггера соединен с выходом переполнения второго счетчика, счетный вход и вход блокировки счета которого подключены соответственно к синхровходу устройства и выходу схемы сравнения, вход сумматора по модулю два соединен с информационным выходом второго счетчика, первый и второй информационные входы схемы сравнения подключены к выходам соответственно сумматора по модулю два и второго коммутатора, счетный вход, вход управления записью и вход разрешения генератора тестов соединены соответственно с седьмым, восьмым и девятым выходами блока уп- равления, а вход условий и синхровход блока управления подключены соответственно к выходу генератора тестов и синхровходу устройства, о. т л и - чающееся тем, что с целью расширения области применения, оно содержит третий счетчик, второй дешифратор, второй регистр тестов, блок разделительных элементов, третий коммутатор, группу элементов И и блок переключателей, первый информационный вход которого и выход второго коммутатора объединены и образуют первый вход-выход устройства для подключения к первому ьходу-выходу объек та контроля, второй информационный вход блока переключателей и выход блока разделительных элементов объединены и образуют второй вход-выход устройства для подключения к второму вход-пыходу объекта контроля, информационный вход-вых,од блока переключателей является входом-выходом устройства для подключения к третьему входу выходу объекта контроля, вход сброса, счетный вход и выход третьего счетчика соединены соответственно с первым и вторым выходами блока управления и информационным входом второго дешифратора, управляющий вход которого подключен к третьему выходу блока управления, информационный вход, синхровход и выход второго регистра тестов соединены соответственно с выходом

0

5

5

5

0

генератора тестов, выходом второго дешифратора и входом блока разделительных элементов, информационный вход, управляющий вход и выход третьего коммутатора подключены соответственно к выходу блока разделительных элементов, четвертому выходу блока управления и первым входам элементов И группы, вторые входы и выходы которых соединены соответственно с выходом первого коммутатора и входам режима блока управления,

2. Устройство по п.отличающееся тем, что блок управления содержит два счетчика, узел памяти, четыре регистра, схему поразрядного сравнения, коммутатор, индикатор и дешифратор, вход которого соединен с выходом первого регистра, выходы дешифратора с первого по восьмой подключены соответственно к выходам блока с первого по третий и с пятого по девятый, счетный вход, вход управления режимом, информационный вход и выход первого счетчика соединены соответственно с синхро- входом блока, выходом коммутатора, выходом первого регистра и адресным входом узла памяти, выход которого подключен к информационному входу первого регистра, информационный вход, синхровход и выход второго регистра соединены соответственно с входом режима блока, девятым выходом дешифратора и первым входом индикатора, первый и второй информационные входы, синхровход и выход третьего регистра подключены соответственно к выходу первого регистра, выходу второго регистра, десятому выходу дешифратора и первому входу схемы поразрядного сравнения, второй вход которой соединен с входом условий блока, информационный вход, синхровход и выход четвертого регистра подключены соответственно к входу условий блока, одиннадцатому выходу дешифратора и первому информационному входу коммутатора, второй информационный вход и управляющий вход которого соединены соответственно с выходом схемы поразрядного сравнения и двенадцатым выходом дешифратора, а счетный вход и выход второго счетчика подключены соответственно к тринадцатому выходу дешифратора и второму входу индикатора„

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для диагностики логических блоков | 1983 |

|

SU1095182A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для контроля и диагностики цифровых узлов | 1980 |

|

SU896627A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для диагностики цифровых блоков | 1988 |

|

SU1674129A1 |

| Устройство для диагностики блоков электронных вычислительных машин | 1976 |

|

SU650080A1 |

| Устройство диагностики многопроцессорного вычислительного комплекса | 1988 |

|

SU1548792A1 |

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Устройство для диагностики блоков электронных вычислительных машин | 1978 |

|

SU746556A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

Изобретение относится к вычислительной технике и может быть использовано для обнаружения и локализации неисправностей блоков ЭВМ. Цель изобретения - расширение области применения. С этой целью в устройство, содержащее блок управления, генератор тестов, два счетчика, два триггера, сумматор по модулю два, схему сравнения, два коммутатора, первый дешифратор и первый регистр тестов, введены третий счетчик, второй дешифратор, второй регистр тестов, блок разделительных элементов, третий коммутатор, группа элементов И и блок переключателей. 2 ил.

Фиг.1

Ш

ч

/kI

i

УУ W

26

-i

f

viw

J2

ГВ1

Фиг. I

20

I

28

| Экономайзер | 0 |

|

SU94A1 |

Авторы

Даты

1991-08-23—Публикация

1988-06-06—Подача