Изобретение относится к области вычислительной техники и может быть использовано при создании вычислительных комплексов повышенной надежности.

Известны двухмашинные вычислительные комплексы, содержавшие средства взаимной диагностикиf13.

Однако такие системы не обеспечивают требуемой надежности комплекса и не позволяют выполнять микродиагностику неисправной ЭВМ с помощью исправной одновременно с выполнением в исправной ЭВМ рабочей программы. Это понижает надежность комплекса, поскольку исправная ЭВМ при диагнос: ике неисправной прекращает выполвение своих обычных функций. Программная же диагностика, которая возможна с одновременным вьтолнением исправной своих функций, не позволяет получать требуемую точностьлокализации, и следовательно, прит емлемого времени восстановления.

Наиболее близким техническим решением к -данному изобретению является устройство для диагностики двухмашинного вычислительно комплекса, содержащее два однотипных блока, каждый из которых состоит из двух

регистров сдвига, соединенных с пер вым входом и первым выходом устройства, дешифратора и буферной памяти, причем вход второго регистра сдвига соединен с выходом буферной памяти, вход которой соединен с выходом соответствующей блоку ЭВМ, а выход второго регистра сдвига соединен со входом дешифратора, выход которого

10 соединен со входом .

Недостаток данного устройства заключается в том, что для диагностики неисправной ЭВМ оно монополизирует исправную ЭВМ для выполнения про15цедуры диагностики. Это резко снижает надежность двухмашинного комплекса, фактически приводя к отказу двухмашинного комплекса На время диагностики неисправной ЭВМ,

20

Цель изобретения - повышение нгшежности двухмашинного вычислительного комплекса.

Поставленная цель достигается тем, что в устройстве для диагности25ки двухмашинного вычислительного комплекса, содержащем два блока связи ЭВМ, каждый из KOTopfJx содержит первый и второй регистры сдвига, первый и второй переключатели, пер30вый дешифратор, блок буферной памяти. причем первый и второй выходы первого переключателя соединены соответственно с информационным и синхр низационным входами первого регистра сдвига, первый и второй входы первого переключателяявляются .сЬот Ьетственно первым информационным и Ьияхронизационным входами блока, пе вый информационный выход первого регистра сдвига соединен со входом первого дешифратора, первый выход которогх является первым управляющие, выходом блока, выход блока буфе ной памяти соединен с информационным входом второго регистра сдвига, последовательный выход которого сое динен с первым входом второго переключателя, первый и второй выходы второго переключателя соединены с первым информационным и синхронизационным выходами блока, информациой ный и синхронизационный выхогил первого блока связи ЭВМ соединены соответственно с информационным и син хронизационным входами второго блока связи ЭВМ, в каждый блок связи ЭВМ введены первый и второй счетчнки, второй дешифратор, первый и второй блоки синхронизации, первый и второй блоки сравнения, регистр диагностики, регистр адреса, первый второй, третий и четвертый триггеры, первый:и второй элементы ИЛИ, первый и второй элемента И, коммутатор, узел контроля по модулю два и входной регистр, прячем первый, второй и третий информационнее выхо ды первого регистра сдвига соединен соответственно с информационным входом регистра ;виагностики, с первым входом первой схемы сравнения, с информационным входом узла контроля по модулю два выход которого соединен с третьим входом первого переключателя, третий выход первого переключателя .является первым коитрольным выходом блока, первый ynpaS ляющий выход первого регистра сдвиг соединен с первыми входаг ш первого и второго элементов И и со входом запуска первого блока синхронизация первый, второй, третий, четвертый и пятый выходы которого соединены сортветственно с синхронизационными входами узла контроля по модулю два первого регистра сдвига, второго эл MjfeHTa Н, первого и второго дешифраторов , второй управлякадий выход первого регистра сдвига соединен со вторыми входами первого и второг злементов И, а выходаз соединены соответственно со счетным и установочным входами первого счетчика, информационный выход первого счетчи ка соединен со входом второго деишфратора, выход которого соединен с управляющим входом регистра диагностики , первый, второй и третий выходы которого соединены соответственно со вторым информационным выходом уст{)ойства, со входом регистра адреса, с первым входом второй схемы сравнения, выходы первой и второй схем сравнения соединены с единичными входами первого и второго триггеров соответственно, выходы которых .первый злемент ИЛИ соединены с четвертым входом первого переключателя, выход которого является вторым контрольным выходом блока, первый, второй-, третий- и четвертый выходы первого дешифратора соединены соответственно с первым управляюгдим выходом блока, с управляющим входом входного регистра и управляющими входами первой и второй схем сравнения, выход регистра адреса соединен с адресным взводом коммутатора, выход которого соединен с информационным входом -входного регистра, второй информационьый вход блока соединен с информадионннм вхрдом коммутатора,- третий информационный вход блока соединен со вторым входом первой схемы сравнения, выход входного регистра сое- . .динен со вторым входом второй схе ivaa сравнения, вход запуска блока соединен с установочным входом второго счетчика НС первым входом запуска второго блока .синхронизации, первый и - второй выходы которого соединеиысоответственно с синхронизацнонным и управляющим входами второго регистра сдвига, управляющий шлход второго регистра сдвига соединен со счетным входом второго счетчика, со вторым входом запуска второго блока синхронизации, первый выход которого соединен со вторым входом второго переключателя, информационный выход второго счетчика соединен с адресным входом блока буферной памяти и является третьим информационным выходом блока, зы.ход переполнения счетчика является вторым управляющим выходом блока, яервый и второй контрольные входы блока соответственно соединены с третьим и четвертым входами второго переключателя, соответствующие выходы которого соединены с единичными входами третьего и четвертого триггеров соответственно, единичньзе выходы которых через второй злемент ИЛИ соединены со стоповым входом второго счетчика и являются соответстйе.нно третьим и-четвертым контрольными выходами блока, первый и второй контрольные выходы первого блока связи с ЭВМ соединены соответственно с первым и вторым контрольными входами второго блока связи с; ЭВМ, первый и второй управляющие, второй и третий информационные, l peтий и четвертый контрольнЕ 1е выходы каждого блока связ с ЭВМ образуют.соответственно первую и вторую группы информационных, управлякндих и контрольных выходов устройства, второй и третий информационные и запускакяцие входы .каждого .блока свзи с ЭВМ образуют соответственно перВую, -вторую информационную и запус- :какнцую группу входов устройства.

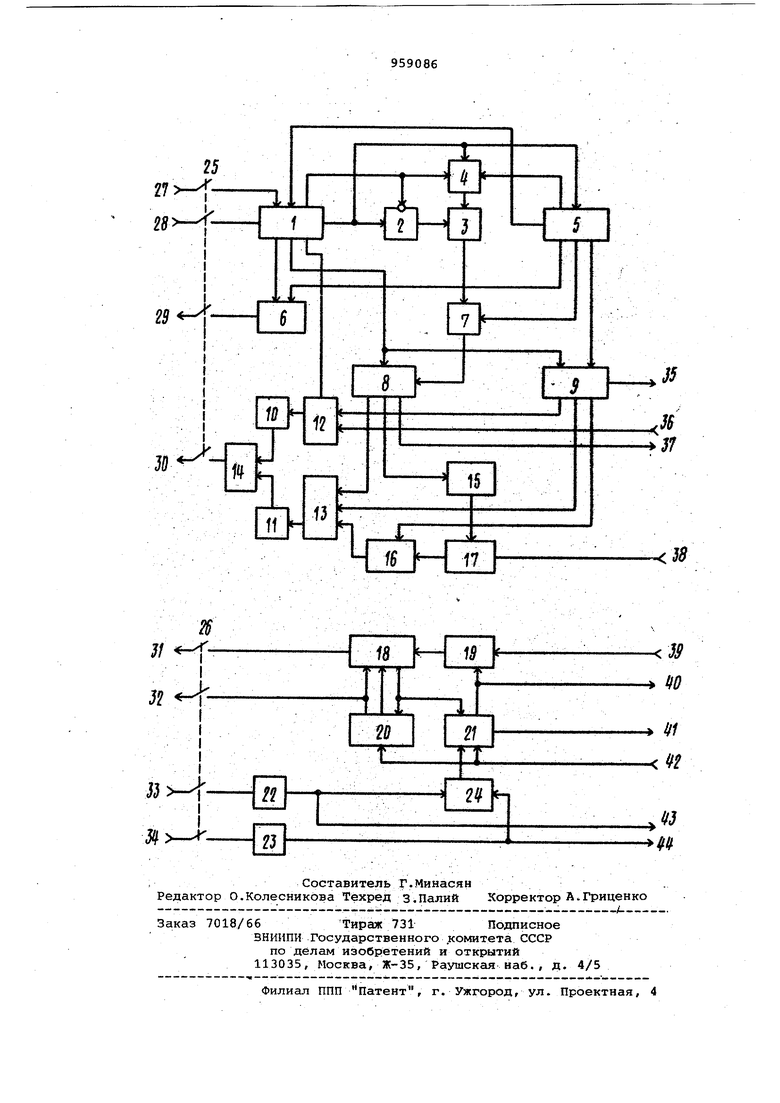

На чертеже представлена схема одного из двух идентичных блоков связи , образующих устройство для взаимной диагностики ЭВМ двухмашинного комплекса. В дальнейшем блок связи, расположенный в ЭВМ 1 (ЭВМ 2) на-зывается первым (вторым блоком связи. ЭВМ ,1 и ЭВМ 2 на чертеже не показаны.

Каждый блок связи содержит регистры сдвига 1, элемент 2 И первый счетчик 3, элемент 4 И, первый блок 5 синхронизации, узел 6 контроля, де- шифратор 7, регистр 8 диагностики, дешифратор 9, триггеры 10 и 11, схемы сравнения 12 и 13, элемент ИЛИ 14, регистр 15 адреса, входной регистр 16, коммутатор 17, регистр 18 сдвига, блок 19 буферной памяти; второй блок 20 синхронизации, второй счетчик 21, триггеры 22 и 23 элемент ИЛИ 24, переключатели 25 и 26. Входы 27, 28 и выходы 29, 30 одного блока связи соединены соответственно с выходами 31, 32 и входами 33, 34 другого блока связи. На чертеже обозначены: выход 35, вхо 36, выход 37, входы 38 и 39, выхода 40 и 41.и вход 42. Выхода 35, 37, 40, 43,44 и входы 36, 38, 39, 42 блока связи соединены с соответствующими выходами-входами своей ЭВМ. ;

Работа устройства поясняется на примере неисрпавности в ЭВМ 2 и первый блок связи устройства диагностики обеспечивает диагностировани неисравностей ЭВМ 2.

Устройство для диагностики двухмашинного вычислительного комплекса работает следукяцим образом.

При обнаружении неисправности схемами контроля ЭВМ 2 она останав ливается после сообщения о неисправности в ожидании дальнейших действий обслуживающего персонала, а ЭВМ 1 продолжает нормальное функционирование. После получения сообщения о неисравности переключатели 26 первого блока связи и 25 второго блока связи устанавливаются во включенное положение, а переключатели 25 первого блока связи и 26 второго блока сйязи - в выключенное.

На ЭВМ 1 параллельно с рабочей программой запускается программа диагностики, которая загружает первый тест микродиагностики в блок буферной памяти 19- на входы 39 первого блока связи. После загрузки буферной 19 на вход 42 первого блока связи из ЭВМ 1 поступает сигнал запуска микродиагностики. Этот сигнал запускает блок 20 синхронизации, который выдает синхронизирующий сигнал в регистр 18 сдвига, обеспечивающий прием информации из блока 19 буферной памяти. Сигнгш эапуска микродиагностики запускает также счетчик 21j который обеспечивает 0 путем приращения формирование последовательных адресов блока . 19 буферной памяти. Информация, при-. нятая в регистр 18 сдвига, начинает сдвигаться и побитно поступает на 5 выход 31 первого блока связи под управлением синхронизирующего сигнала от блока 20 синхронизации.

После завершения сдвига в счетчик 21 и блок 20 синхронизации из регистра 18 сдвига поступает сигнал приращения, по которому происходит приращение содёржимого счетчика 21, т.е. модификация адреса буферной памяти 19 и повторный запуск 5 блока 20 синхронизации. Содержимое следуквдего адреса буферной памяти 19 снова поступает в регистр 18 сдвига и дальше повторяется описанная . процедура сдвига информации. Информация теста микролиагностики с вы0хода регистра 18 сдвига последовательно бит за битом поступает через выход 31 первого блока связи и вход 27 второго блока связи на информационный вход регистра 1 сдвига : второго блока связи. Синхросигналы, iсоответствующие каждому биту передаваемой информации и обеспечивающие его прием в регистр 1 сдвига второго блока/связи, формируются в блоке 0 20 синхронизации первого блока связи и поступают через его выход 32 на вход 28 второго блока связи и далее на синхронизационный вход регистра 1 сдвига. В регистре 1 сдвига информация, поступакядая на его : информационный вход последовательным кодом, снова превращается в параллельный код.

Последовательный канал связи меж0 ДУ блоками устройства сокращает количество связей между ЭВМ двухмашинного комплекса, что особенно важно при значительной удаленности ЭВМ друг от друга, и повышает надежность 5 устройства диагностики.

После завершения сдвига информации в регистре 1 сдвига в блок 5 синхронизации .из регистра 1 сдвигапоступает сигнал, обеспечивающий запуск блока 5 синхронизации. Этот, же

Q сигнал поступает на элементы 2 и 4 И.

Накопленная в регистре 1 сдвига информация содержит бит контроля по четности. Эта информация поступает .. I навход узла б контроля. На другой 5 его вход от блока 5 синхронизации поступает сигнал, обеспечивающий проверку содержимого регистра .1 сдви га на четность. Таким образом, ошиб ка во время передачи обнаруживается узлом 6 контроля втррого блока связи Сигнал ошибки с выхода узла 6 контроля поступает на выход 29 второго блока связи и далее через вход 133 первого блока связи устанавливает в единичное состояние триггер 22. Сигнал с выхода триггера 22 через элемент 24 ИЛИ поступает на блокировку счетчика 21, прекращая его приращение и выдачу информации.тес,та микродиагностики из первого связи во второй. Одновременно |Сигнал с выхода триггера 22 через выход 43 первого блока связи поступает в ЭВМ 1, свидетельствуя о наличии ошибки в передаче. В результате программа диагностики ЭВМ 1 повторяет передачу теста микродиагностики в ЭВМ 2. Информация теста микродиагности1КИ, поступающая в регистр 1 сдвига, представляет собой часть .микрокоманды, служебную информацию или код диагностической операции. В первом и втором случаях управляющий (младший) бит регистра 1 сдвига равен нулю,а в третьем случае - единице. В первом и втором слу чаях с помощью элемента 2 И происходит приращение значения счетчика 3, а в третьем случае - обнуление счетчика 3 под управлением сигнала, поступающего из блока 5 синхронизации В первом и втором случаях информация из регистра 1 сдвига заполняет регистр 8 диагностики под управление счетчика 3, дешифратора 7 и синхронизиругацего сигнала от блока 5 синхр

низации.

Разрядность регистра диагностику в несколько раз больше разрядности регистра 1 сдвига и счетчик 3 с дешифратором 7 обеспечивают прием информации с выхода регистра 1 сдвига в соответствующие разряды регистра 8 диагностики.

В третьем случае информация с выхода регистра 1 сдвига декодируется на дешифраторе 9 диагностических операций под управлением синхрбни ирующего сигнала, постуцанадего от/ блока 5 синхронизации.

,, Диагностические операции j возбуждающие выходы 35 второго блока связи, обеспечивают.тприем с выхода 37 второго блока связи частей микрокоманды, накопленных в регистре 8 диагностики, в регистр микрокоманд ЭВМ 2 и выполнение микрокоманды после запуска синхронизации ЭВМ 2 на один такт.

Состояние триггеров и регистров ЭВМ 2 после выполнения микрокоманды опрашивается с помощью коммура 9.

При ошибке ветвления сигнал с выхода блока 12 сравнения устанавливает в единичное состояние триггер 10 ветвления, выход которого, также, как и выход триггера 11, через элемент 14 ИЛИ, через выход 30 второго блока связи поступает на вход 34 первого блока связи, устанавливая в единичное состояние триггер 23 неисправности ЭВМ 2.

После завершения обработки информации, накопленной в регистре 1 сдвига, блок 5 синхронизации выдает сигнал обнуления регистра 1 сдвига. Сигнал с выхода триггера 23 по- ступает через элемент 24 ИЛИ на блокировку счетчика 21 и на выход 44 первого блока связи..Этот сигнал поступает в ЭВМ 1 и программа диагностики формирует сообщение о неисправности. Кроме того, в ЭВМ 1 по выходу 40 первого блока связи поступает состояние счетчика, по которому программа диагностики 5 определяет место обнаружения неисптатора 17 и регистра 15 адреса. Выходы триггеров и регистров ЭВМ 2 поступают на входы 38 второго блока связи. Адрес требуемого регистра ЭВМ 2 задается информацией, поступающей в регистр 15 адреса через регистр 8 диагностики. Адрес требуемого регистра поступает далее с выхода регистра 15 на вход коммутатора 17. После этого в регистр 1 сдвига поступает код диагностической операции, возбуждакнцей выход дешифратора 9, который разрешает прием во входной регистр 16 информации о состоянии требуемого регистра. Информация с выхода входного регистра 16 поступает на вхой блока 13 сравнения. На другие входы блока 13 сравнения поступает эталонная информация с выхода регистра 8 диагностики и сигнал разрушения сравнения с выхода дешифратора 9. При несравнении сигнал ошибки с выхода блока 13 сравнения устанавливает в единичное состояние, триггер 11 ошибки состояния Результаты выполнения микрокоманды в ЭВМ 2 может явиться также модификация младших битов регистра адреса микрокоманд ЭВМ 2. Для проверки правильности функционирования схем анализа ЭВМ 2, вызывающих ветвление в микропрограмме, устройство содержит блок 12 сравнения, на вход которой по входу 36 второго блока связи из ЭВМ 2 поступает состояние младших битов регистра адреса микрокоманд ЭВМ 2. Эталонная информация для сравнения поступает из регистра 1 сдвига. Разрешение на выполнение операции сравнения поступает с выхода дешифратоjsaBHocTH в тесте микродиагностики. Если тест a кpoдиaгнocтики выполнилс успешно и выдача теста из блока 19 б ; ферной .памяти завершилась, счетчик 21 вырабатывает сигнал, который поступает на выход 41 первого блока связи в ЭВМ 1, запрашивая загрузку нового теста микродиагностики в блок 19 буферной памяти. При предложенной организации диагностики достигается высокая лока лизуемость неисправности, значительно ровышаетсй надежность двухмашинного комплекса.. Формула изобретения Устройство для диагностики двухмашинного вычислительного комплекса содержащее два блока связи ЭВМ, каждый 43 которых содержит первый и второй регистры сдвига, первый и второй переключатели, первый дешифратор, блок буферной памяти, причем первый и второй входы первого переключателя соединены соответствен но с информационным и синхронизационным входами первого регистра сдвига, первый и второй входы первого переключателя являются соотввт ствённо первым информационным и синхронизационным входами блока, первый информационный выход первого регистра сдвига соединён, со входом первого . дешифратора, первый выход которого является первым управляквдим выходов блока, выход блока буферной соединен с информационным В:ходом второго регистра сдвига. Последовательный выход которого соединен с первым входом второго переключателя первый и второй выходы второго переключателя соединены с первым инфор мационным и синхронизационным выходами блока, информационный и синхронизационный выходы первого блока связи ЭВМ соедин ены соответственно с информационным и синхронизацион ным входами второго блока связи ЭВМ от ли ча ю щ е е с я тем что, с целью повышения нгщежности комплек .са, в каждый блок связи ЭВМ введены первый и второй счетчики, второй деиетфратор, первый и второй блоки синх ронизации, первый и второй блоки сравнения,регистр диагностики,регист адреса, первый, второй, третий и четвертый триггеры, первый и второй элементы ИЛИ, первый и второй элемен ты И, коммутатор, узел контроля по м дулю два и входной регистр, причем первый, второй и третий информационные выходы первого регистра сдйига соединены соответственно с информационным входом регистра диагностики, с первым входом первой схемы сра нения, с информационным входом узла контроля по модулю два, выход которого соединен с третьим входом первого переключателя, третий, выход первого переключателя является первым контрольным выходом блока, первый управляющий выход первого регистра сдвига соединен с первыми входами первого и второго элементов И.- и со входом запуска первого блока синхронизации , первый, второй, третий, четвертый и пятый выходы которого соединены соответственно с синхронизационными входами узла контроля по модулю два, первого регистра сдвига, второго элемента И, первого и второго дешифраторов , второй управляющий выход первого регистра сдвига соединен со вторыми входами первого и второго элементов И, а выходы соединены соответственно со счетным и установочным входами первого счетчика, информационный выход первого счетчика соединен со входом второго дешифратора, выход которого соединен с управляющим входом регистра диагностики, первый, второй и третий шлходы которого соединены соответственно со вторым информационным выходом устройства, со входом регистра адреса, с первым входом второй схемы сравнения, выходы первой и второй схем сравнения соединены с единичными входами первого и второго триггеров соответственно, выходы которых через первый элемент ИЛИ соединены с четвертым входом первого переключателя, выход которого является вторым контрольным выходом блока, первый, второй, третгий и четвертый выходы первого дешифратора соединены соответственно с первым управляювщм выходом блока, с управляющем входом входного регистра и управляющими входами первой и второй схем сравнения, выход регистра адреса соединен с адресньгм 1зхояом коммутатора, выход которого соединен с информационным входом входного регистра, второй информационный вход блока соединен . с информационным входом коммутатора, третий информационный вход блока соединен со вторым входом первой схемы сравнения, выход входного регистра соединен со вторым входом второй схемы сравнения, вход запуска блока соединен с установочным входом второго счетчика и с пер- вым входом запуска второго блока синхронизации, первый и второй выходы которого соединены соответственно с -синхронизационным и управляющим входами второго регистра сдвига, управляющий выход второго регистра сдвига соединен со счетным входом второго счетчика, со вторым входом запуска второго блока синхронизации, первый выход которого соединен со вторым входом второго переключателя, информационный выход второго счетчика соединен с адресным входом блока буферной памяти и является третьим информационным выходом блока, выход переполнения счетчика является вторым управляющим 5 выходом блока, первый и втоаой контрольные входы блока соответственHO соединены с третьим и четвертым входами второго переключателя, соответствукзадие выходы которого соединены О

с едивичными входами третьего и четBepjroro триггеров соответственно, единичные выходы которых через второй элемент ИЛИ соединены со стоповым входом второго счетчика и являются 15 соответственно третьим и четвертым Контрольными выходами блока, первый И второй контрольные выхода первого блока связи с ЭВМ соединены соответственно с первым и вторым контроль- п ными входами второго блока связи с

ЭВМ, первый и второй управляющие, второй и третий информационные, третий и четвертый контрольные выходы каждого блока связи с ЭВМ образуют соответственно первую и вторую группы информационных, управляющих и контрольных выходов устройства, второй и-третий информационные и запускающие входы каждого блока связи с ЭВМ образуют соответственно первую, вторую информационные и запускающую группы входов устройства.

Источники информации, принятые во внимание при экспертизе

1.« Авторское свидетельство СССР 603995, кл. G 06 F 15/16, 1978.

2. Той В.Н, Проектирование отказоустойчивых местных процессоров для систем электоонной когФ4утацйи. ТИИЭИР, 1978, т. 66, 10, с.26-48 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для диагностики трехмашинного вычислительного комплекса | 1985 |

|

SU1383366A1 |

| Устройство для диагностики эвм | 1976 |

|

SU641453A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Устройство сопряжения двух ЭВМ | 1985 |

|

SU1334153A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1129599A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

Авторы

Даты

1982-09-15—Публикация

1980-07-16—Подача