Изобретение относится к автоматике и может быть использовано в различных отраслях промышленности в системах управления двухпозиционными объектами в функции времени, например, для программного управления переходным процессом переключения регенеративных теплообменников воздухоразделительных установок.

Цель изобретения - повышение надежности работы устройства.

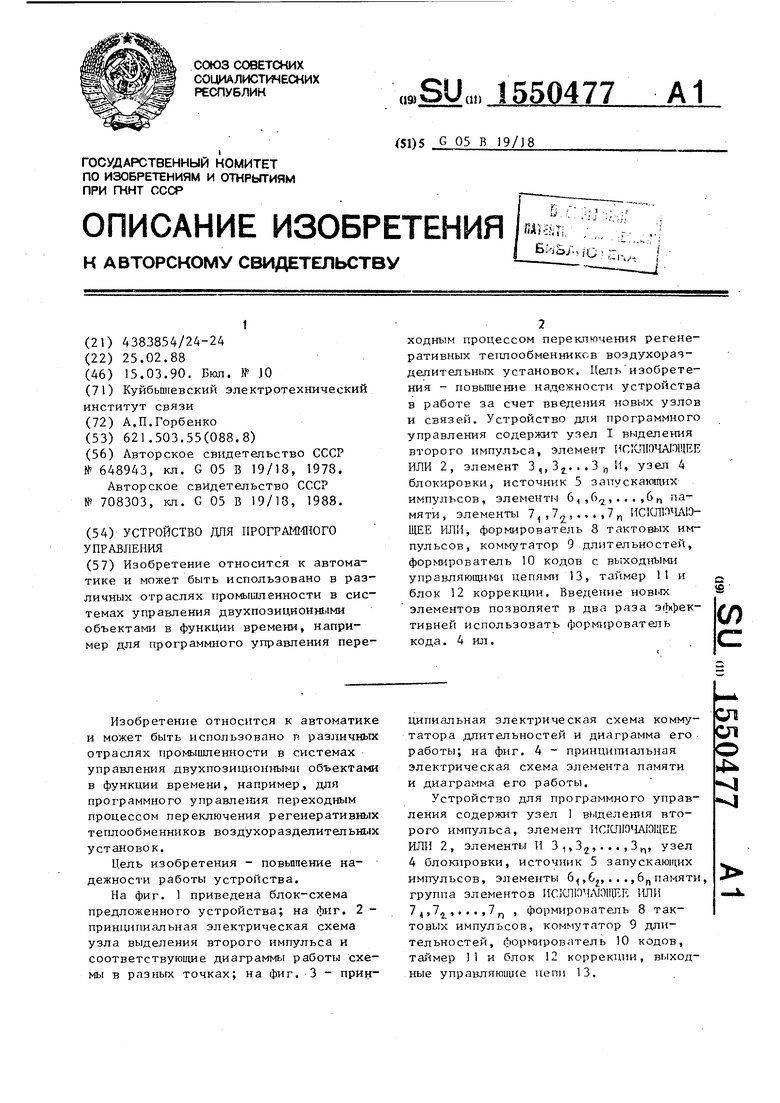

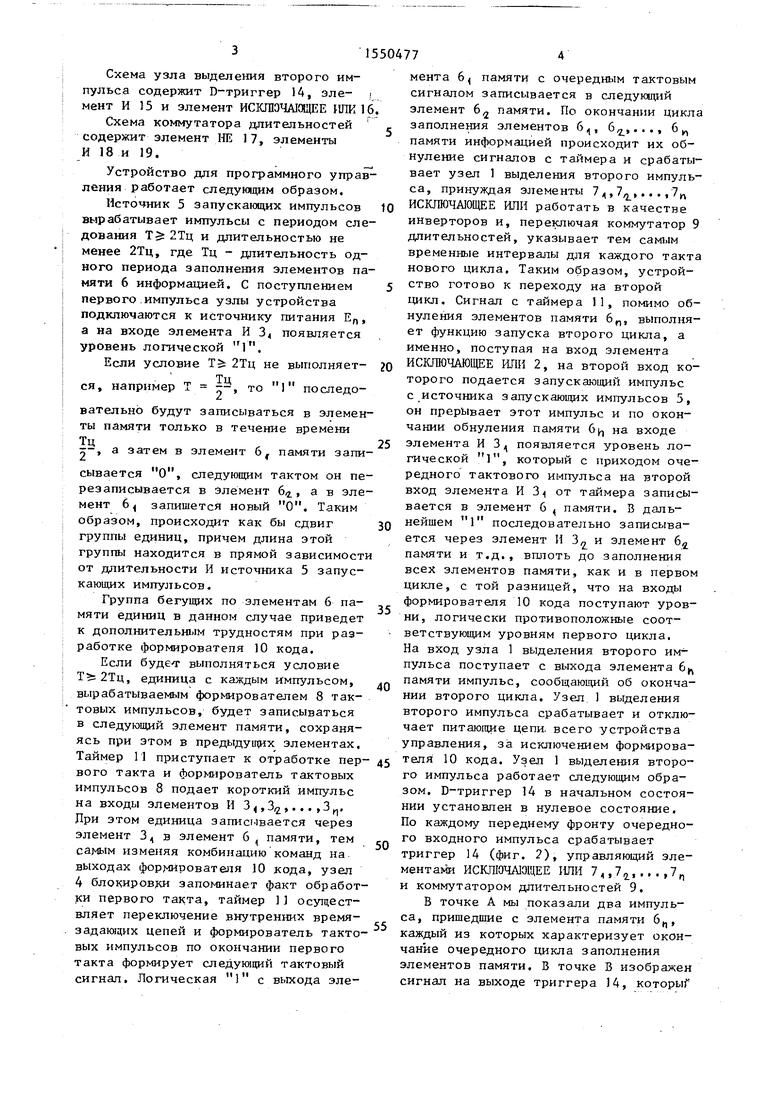

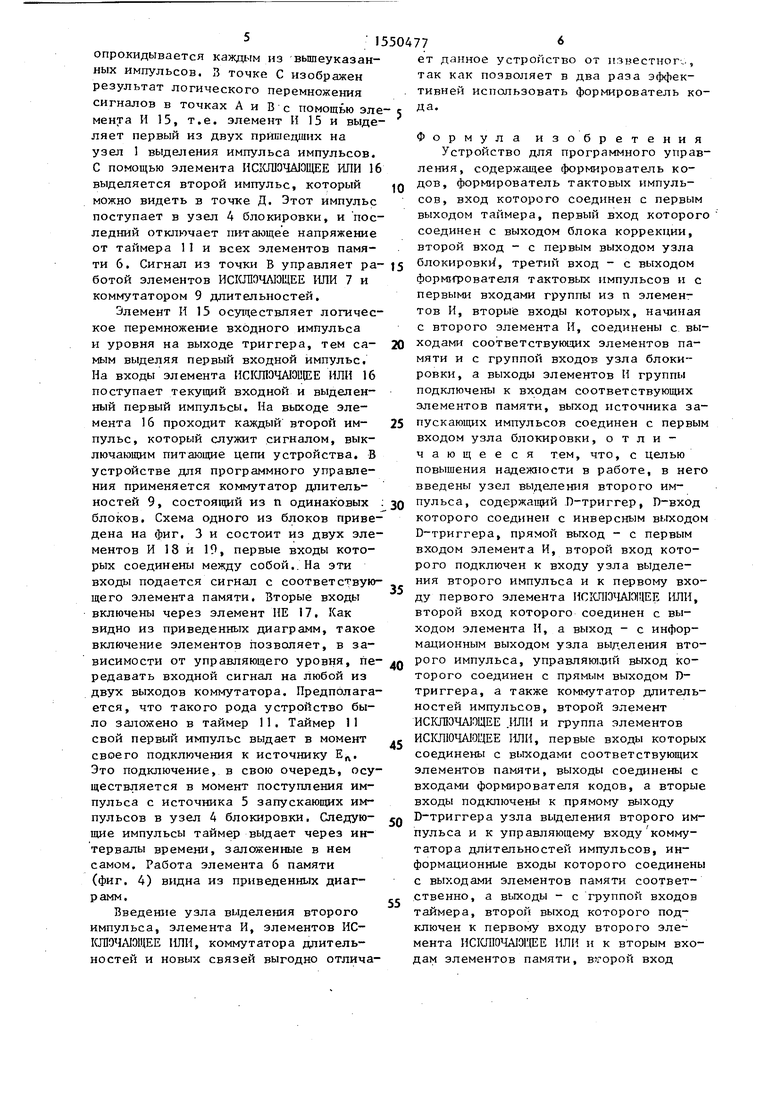

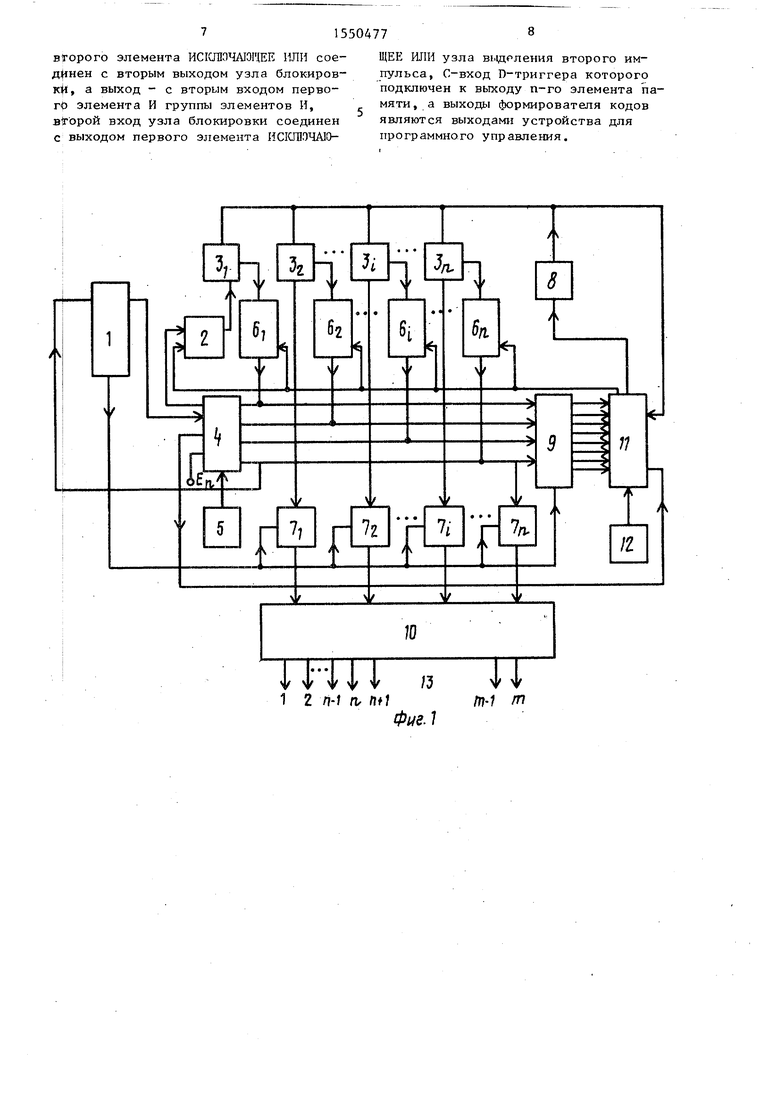

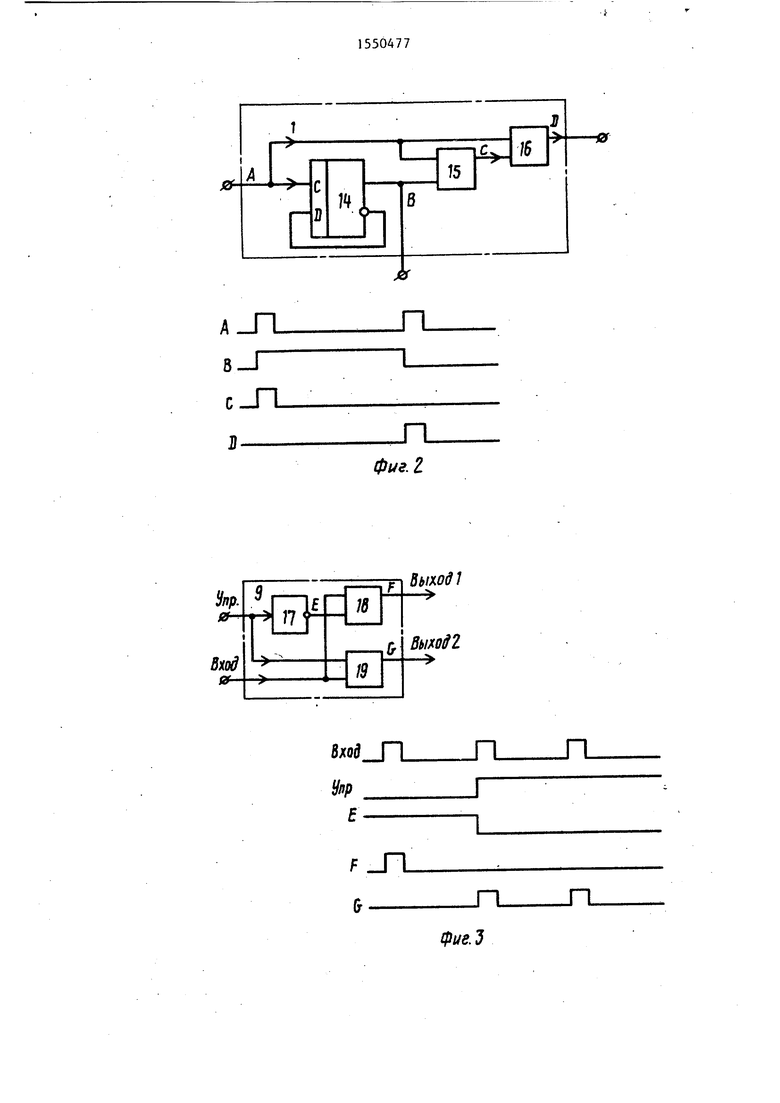

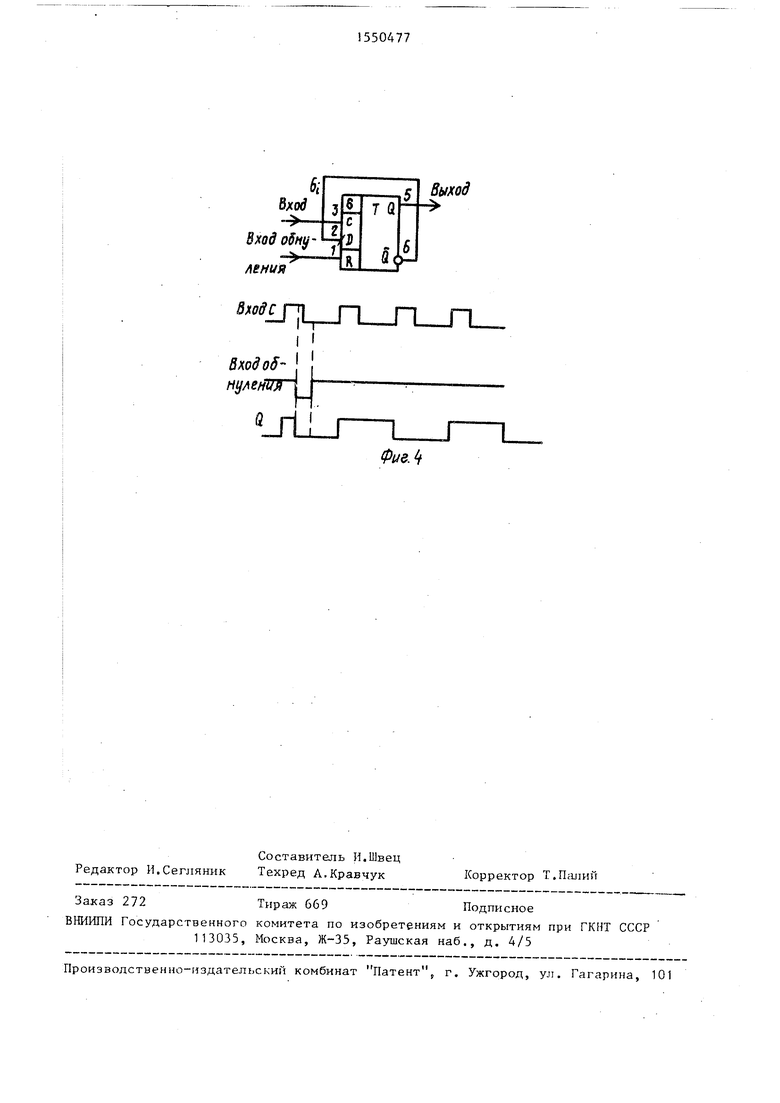

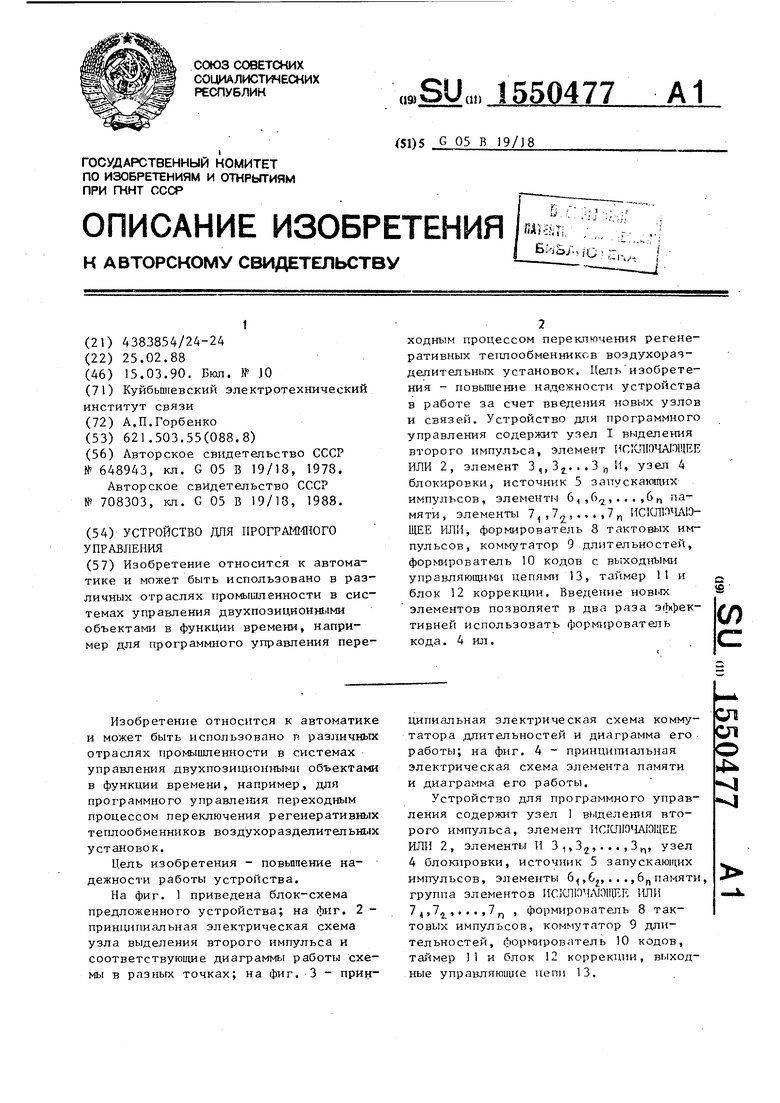

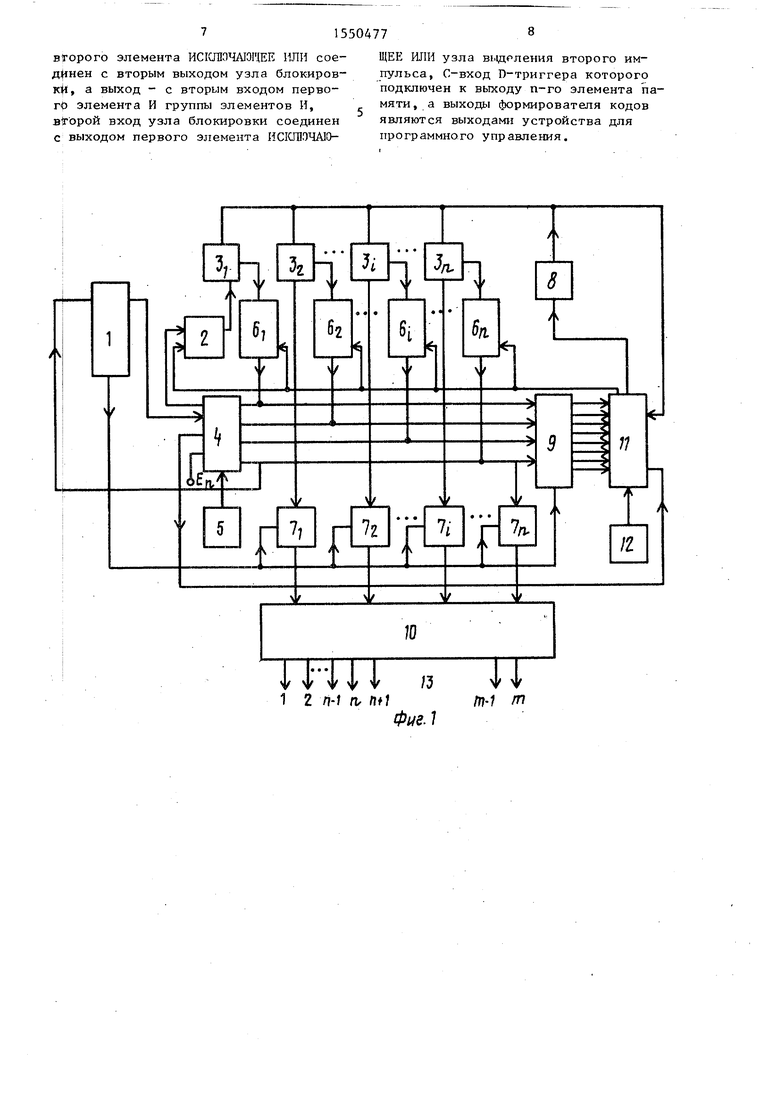

На фиг. 1 приведена блок-схема предложенного устройства; на фиг. 2 - принципиальная электрическая схема узла выделения второго импульса и соответствующие диаграммы работы схемы в разных точках; на фиг. 3 - принципиальная электрическая схема коммутатора длительностей и диаграмма его работы; на фиг. 4 - принципиальная электрическая схема элемента памяти и диаграмма его работы.

Устройство для программного управления содержит узел 1 выделения второго импульса, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2, элементы И 3 1э32,...,3П, узел 4 блокировки, источник 5 запускающих импульсов, элементы 6,6,.. .,6П памяти, группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7,,7i,...,7П , формирователь 8 тактовых импульсов, коммутатор 9 длительностей, формирователь 10 кодов, таймер 11 и блок 12 коррекции, выходные управляющие цепи 13.

сл ел

о

4

Схема узла выделения второго импульса содержит D-триггер 14, эле- i мент И 15 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 16.

Схема коммутатора длительностей г содержит элемент НЕ 17, элементы И 18 и 19.

Устройство для программного управления работает следующим образом.

Источник 5 запускающих импульсов вырабатывает импульсы с периодом следования Т$ 2Тц и длительностью не менее 2Тц, где Тц - длительность одного периода заполнения элементов памяти 6 информацией. С поступлением первого импульса узлы устройства подключаются к источнику питания Еп, а на входе элемента И 3 появляется уровень логической 1.

Если условие Т 2Тц не выполняется, например Т --, то 1 последовательно будут записываться в элементы памяти только в течение времени Тц

Г а

6 памяти запи

затем в элемент

сывается О, следующим тактом он перезаписывается в элемент 6г, а в элемент 6 запишется новый О. Таким образом, происходит как бы сдвиг группы единиц, причем длина этой группы находится в прямой зависимости от длительности И источника 5 запускающих импульсов.

Группа бегущих по элементам б памяти единиц в данном случае приведет к дополнительным трудностям при разработке формирователя 10 кода.

Если будет выполняться условие , единица с каждым импульсом, вырабатываемым формирователем 8 тактовых импульсов, будет записываться в следующий элемент памяти, сохраняясь при этом в предыдущих элементах.

0 5

о

5

0

5

0

мента 6 памяти с очередным тактовым сигналом записывается в следующий элемент 6 памяти. По окончании цикла заполнения элементов 6,,, 6,..., 6h памяти информацией происходит их обнуление сигналов с таймера и срабатывает узел 1 выделения второго импульса, принуждая элементы 707,2,.. ., 7М ИСКЛЮЧАЮЩЕЕ ИЛИ работать в качестве инверторов и, переключая коммутатор 9 длительностей, указывает тем самым временные интервалы для каждого такта нового цикла. Таким образом, устройство готово к переходу на второй цикл. Сигнал с таймера 11, помимо обнуления элементов памяти 6П, выполняет функцию запуска второго цикла, а именно, поступая на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2, на второй вход которого подается запускающий импульс с источника запускающих импульсов 5, он прерывает этот импульс и по окончании обнуления памяти 6 на входе элемента И Зц появляется уровень логической , который с приходом очередного тактового импульса на второй вход элемента И 3 от таймера записывается в элемент 6 памяти. В дальнейшем 1 последовательно записывается через элемент И 3 и элемент 62 памяти и т.д., вплоть до заполнения всех элементов памяти, как и в первом цикле, с той разницей, что на входы формирователя 10 кода поступают уровни, логически противоположные соответствующим уровням первого цикла. На вход узла 1 выделения второго импульса поступает с выхода элемента 6Л памяти импульс, сообщающий об окончании второго цикла. Узел 1 выделения второго импульса срабатывает и отключает питающие цепи, всего устройства управления, за исключением формирова

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения фазовых сдвигов сигналов от многоканальных интерферометров термоядерных установок | 1983 |

|

SU1352395A1 |

| Устройство для программного управления | 1976 |

|

SU708303A1 |

| КОДОИМПУЛЬСНОЕ ПЕРЕДАЮЩЕЕ УСТРОЙСТВО С СОКРАЩЕНИЕМ ИЗБЫТОЧНОСТИ ИНФОРМАЦИИ | 2001 |

|

RU2234738C2 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

| Программное временное устройство | 1990 |

|

SU1762298A1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2024920C1 |

| Устройство для тренировки операторов | 1989 |

|

SU1647621A1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2079165C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| Устройство для тренировки операторов | 1989 |

|

SU1730652A1 |

Изобретение относится к автоматике и может быть использовано в различных отраслях промышленности в системах управления двухпозиционными объектами в функции времени, например для программного управления переходным процессом переключения регенеративных теплообменников воздухоразделительных установок. Цель изобретения - повышение надежности устройства в работе за счет введения новых узлов и связей. Устройство для программного управления содержит узел 1 выделения второго импульса, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2, элемент 31, 32,...,3N И, узел 4 блокировки, источник 5 запускающих импульсов, элементы 61,62, ... , 6N памяти, элементы 71,72,...,7N ИСКЛЮЧАЮЩЕЕ ИЛИ, формирователь 8 тактовых импульсов, коммутатор 9 длительностей, формирователь 10 кодов с выходными управляющими цепями 13, таймер 11 и блок 12 коррекции. Введение новых элементов позволяет в два раза эффективней использовать формирователь кода. 4 ил.

Таймер 11 приступает к отработке пер- д5 теля кода. Узел 1 выделения вторового такта и формирователь тактовых импульсов 8 подает короткий импульс на входы элементов И 3,3,..., 3. При этом единица записывается через элемент 3,, в элемент б( памяти, тем самым изменяя комбинацию команд на выходах формирователя 10 кода, узел 4 блокировки запоминает факт обработки первого такта, таймер 11 осуществляет переключение внутренних время- задакнцих цепей и формирователь тактовых импульсов по окончании первого такта формирует следующий тактовый сигнал. Логическая 1 с выхода эле0

5

го импульса работает следующим образом. D-триггер 14 в начальном состоянии установлен в нулевое состояние. По каждому переднему фронту очередного входного импульса срабатывает триггер 14 (фиг. 2), управляющий элементами ИСКЛЮЧАЮЩЕЕ ИЛИ 7,7г,...,7п и коммутатором длительностей 9.

В точке А мы показали два импульса, пришедшие с элемента памяти 6М каждый из которых характеризует окончание очередного цикла заполнения элементов памяти. В точке В изображен сигнал на выходе триггера 14, которьи

опрокидывается каждым из вышеуказанных импульсов. 3 точке С изображен результат логического перемножения сигналов в точках А и В с помощью эле- мента И 15, т.е. элемент И 15 и выделяет первый из двух пришедших на узел 1 выделения импульса импульсов. С помощью элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16 выделяется второй импульс, который можно видеть в точке Д. Этот импульс поступает в узел 4 блокировки, и последний отключает питающее напряжение от таймера 11 и всех элементов памяти 6. Сигнал из точки В управляет pa- J5 блокировки1, третий вход - с выходом

ботой элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и коммутатором 9 длительностей.

Элемент И 15 осуществляет логическое перемножение входного импульса и уровня на выходе триггера, тем самым выделяя первый входной импульс. На входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16 поступает текущий входной и выделенный первый импульсы. На выходе элемента 16 проходит каждый второй импульс, который служит сигналом, выключающим питающие цепи устройства. В устройстве для программного управления применяется коммутатор длительностей 9, состоящий из п одинаковых . блоков. Схема одного из блоков приведена на фиг. 3 и состоит из двух элементов И 18 и 19, первые входы которых соединены между собой. На эти входы подается сигнал с соответствующего элемента памяти, Вторые входы включены через элемент НЕ 17. Как видно из приведенных диаграмм, такое включение элементов позволяет, в зависимости от управляющего уровня, пе- дл рого импульса, управляющий выход ко- редавать входной сигнал на любой изторого соединен с прямым выходом Dдвух выходов коммутатора. Предполагается, что такого рода устройство было заложено в таймер 11. Таймер 11 свой первый импульс выдает в момент своего подключения к источнику ЕЛ. Это подключение, в свою очередь, осуществляется в момент поступления импульса с источника 5 запускающих импульсов в узел 4 блокировки. Следующие импульсы таймер выдает через интервалы времени, заложенные в нем самом. Работа элемента 6 памяти (фиг. 4) видна из приведенных диаграмм.

Введение узла выделения второго импульса, элемента И, элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, коммутатора длительностей и новых связей выгодно отличает данное устройство от иэиестног., так как позволяет в два раза эффективней использовать формирователь кода.

Формула изобретения

Устройство для программного управления, содержащее формирователь кодов, формирователь тактовых импульсов, вход которого соединен с первым выходом таймера, первый вход которого соединен с выходом блока коррекции, второй вход - с первым выходом узла

0

5

0

5

формирователя тактовых импульсов и с первыми входами группы из п элементов И, вторые входы которых, начиная с второго элемента И, соединены с выходами соответствующих элементов памяти и с группой входов узла блокировки, а выходы элементов И группы подключены к входам соответствующих элементов памяти, выход источника запускающих импульсов соединен с первым входом узла блокировки, отличающее ся тем, что, с целью повышения надежности в работе, в него введены узел выделения второго импульса, содержащий D-триггер, П-вход которого соединен с инверсным выходом D-триггера, прямой выход - с первым входом элемента И, второй вход которого подключен к входу узла выделения второго импульса и к первому входу первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом элемента И, а выход - с информационным выходом узла выделения вто5

0

5

триггера, а также коммутатор длительностей импульсов, второй элемент ИСКЛЮЧАЮЩЕЕ .ИЛИ и группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первые входы которых соединены с выходами соответствующих элементов памяти, выходы соединены с входами формирователя кодов, а вторые входы подключены к прямому выходу D-триггера узла выделения второго импульса и к управляющему входу коммутатора длительностей импульсов, информационные входы которого соединены с выходами элементов памяти соответственно, а выходы - с группой входов таймера, второй выход которого подключен к первому входу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и к вторым входам элементов памяти, второй вход

второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ сое- с вторым выходом узла блокировки, а выход - с вторим входом первого элемента И группы элементов И, второй вход узла блокировки соединен с выходом первого элемента ИСКЛЮЧАЮФ Ф Ф | Ф /3Ф Ф

1 2 п-1 п, п 1/п-; т

Фие.1

ЩЕЕ ИЛИ узла выделения второго импульса, С-вход D-триггера которого подключен к выходу n-го элемента памяти, а выходы формирователя кодов являются выходами устройства для программного управления.

8-J

c-JT

Л

П

П

Фиг. I

Фие.З

Входе

ФигЛ

| Цикловая система управления промышленным роботом | 1977 |

|

SU648943A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для программного управления | 1976 |

|

SU708303A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1990-03-15—Публикация

1988-02-25—Подача