Изобретение относится к устрой- ётвам перемножения электрических сигналов и может быть использовано вана- йоговых вычислительных машинах.

Целью изобретения является повы- даение точности.

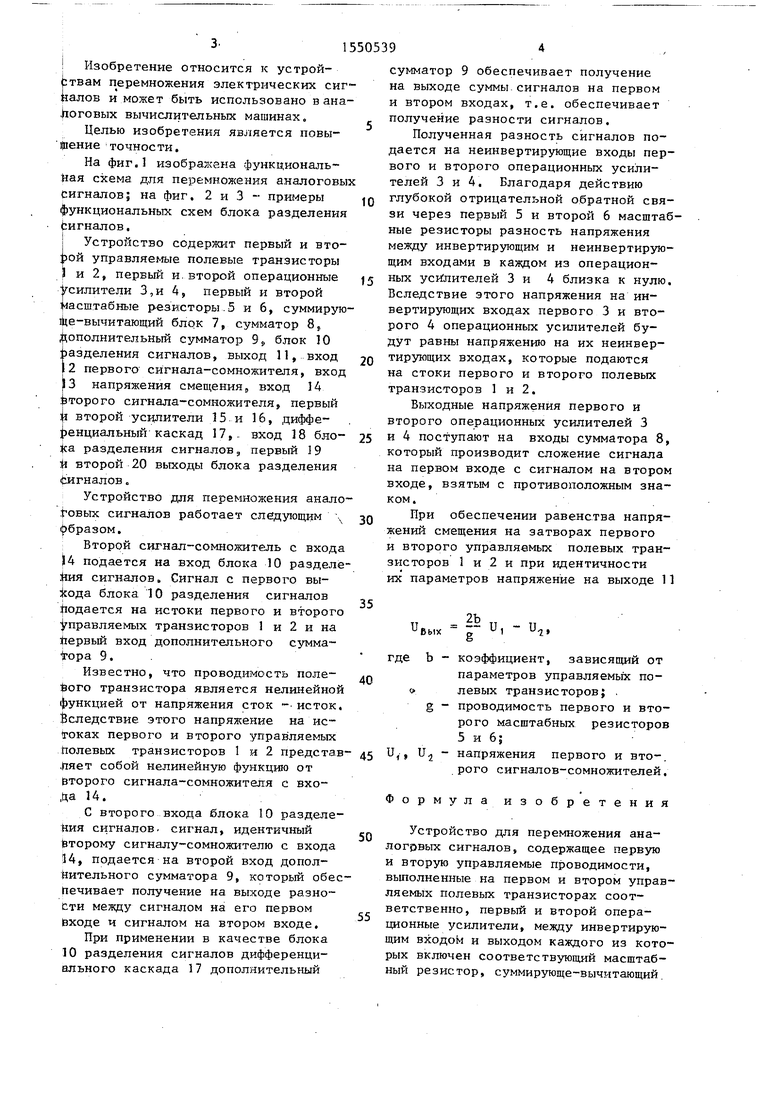

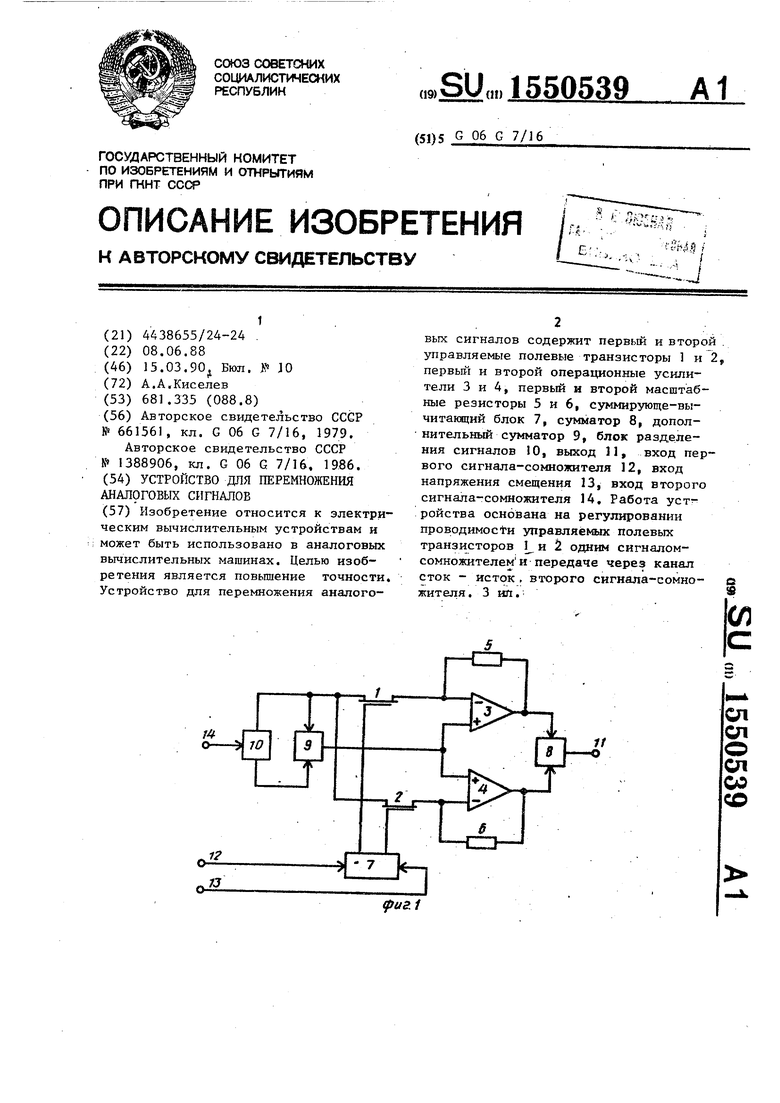

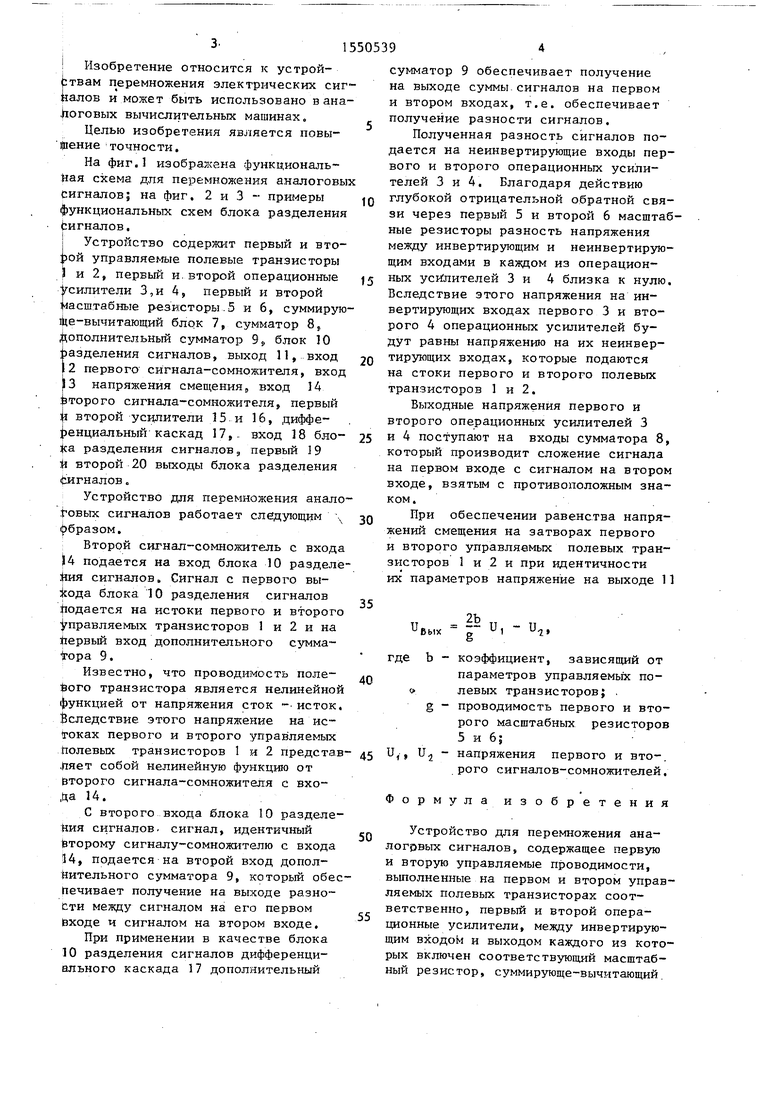

На фиг.1 изображена Јункциональ- йая схема для перемножения аналоговых Сигналов; на фиг. 2 и 3 - примеры функциональных схем блока разделения Ыгналов.

Устройство содержит первый и второй управляемые полевые транзисторы ) и 2, первый и второй операционные усилители 3,и 4, первый и второй Масштабные р-ез сторы 5 и 6, суммирую ще-вычитающий блок 1, сумматор 8, дополнительный сумматор 9г блок 10 разделения сигналов, выход 11, вход |2 первого сигнала-сомножителя, вход 3 напряжения смещения, вход 14 второго сигнала-сомножителя, первый $ второй усилители 15 и 16, дифференциальный каскад 17, вход 18 бло- fca разделения сигналов,, первый 19 ti второй 20 выходы блока разделения Јигналов „

Устройство для перемножения анапо foBbix сигналов работает следующим ч эбразом.

Второй сигнал-сомножитель с входа J4 подается на вход блока 10 разделе Йия сигналов. Сигнал с первого вывода блока 10 разделения сигналов подается на истоки первого и второго управляемых транзисторов 1 и 2 и на первый вход дополнительного сумматора 9.

Известно, что проводимость поле- вого транзистора является нелинейной функцией от напряжения сток - исток. Вследствие этого напряжение на истоках первого и второго управляемых долевых транзисторов 1 и 2 представ Ггяет собой нелинейную функцию от второго сигнала-сомножителя с входа 14.

С второго входа блока 10 разделения сигналов, сигнал, идентичный второму сигналу-сомножителю с входа 14, подается на второй вход дополнительного сумматора 9, который обеспечивает получение на выходе разности между сигналом на его первом входе ч сигналом на втором входе.

При применении в качестве блока 10 разделения сигналов дифференциального каскада 17 дополнительный

сумматор 9 обеспечивает получение на выходе суммы сигналов на первом и втором входах, т.е. обеспечивает получение разности сигналов.

Полученная разность сигналов подается на неинвертирующие входы первого и второго операционных усилителей 3 и 4. Благодаря действию глубокой отрицательной обратной связи через первый 5 и второй 6 масштабные резисторы разность напряжения между инвертирующим и неинвертирующим входами в каждом из операционных усилителей 3 и 4 близка к нулю. Вследствие этого напряжения на инвертирующих входах первого 3 и второго 4 операционных усилителей будут равны напряжению на их неинвертирующих входах, которые подаются на стоки первого и второго полевых транзисторов 1 и 2.

Выходные напряжения первого и второго операционных усилителей 3 и 4 поступают на входы сумматора 8, который производит сложение сигнала на первом входе с сигналом на втором входе, взятым с противоположным знаком.

При обеспечении равенства напряжений смещения на затворах первого и второго управляемых полевых транзисторов 1 и 2 и при идентичности их параметров напряжение на выходе 1

U

Еых

Q II - U g U

где b - коэффициент, зависящий от параметров управляемых по- о левых транзисторов;

g - проводимость первого и второго масштабных резисторов 5 и 6;

Uf, U 2 - напряжения первого и второго сигналов-сомножителей.

Формула изобретения

Устройство для перемножения аналоговых сигналов, содержащее первую и вторую управляемые проводимости, выполненные на первом и втором управляемых полевых транзисторах соответственно, первый и второй операционные усилители, между инвертирующим входом и выходом каждого из которых включен соответствующий масштабный резистор, суммирующе-вычитающий

515

блок, первый и второй выходы которог подключены соответственно к затворам первого и второго управляемых полевых транзисторов, истоки которых соединены между собой, стоки первого и второго управляемых полевых транзисторов подключены соответственно к инвертирующим входам первого и второго операционных усилителей, неин- вертирующие входы которых объединены, а выходы соединены с входами сумматора, выход которого является выходом устройства, первый и второй входы суммирующе-вычитающего блока являются соответственно входом пер- чого сигнала-сомножителя устройства

и входом напряжения смещения, отличающееся тем, что, с целью повышения точности, в него введены дополнительный сумматор и блок разделения сигналов, вход которого является входом второго сигнала-сомножителя устройства, первый и второй выходы блока разделения сигналов соединены с входами дополнительного сумматора, выход 1соторого подключен к неинвертирующим входам первого и второго операционных усилителей, первый выход блока разделения сигналов соединен с истоком первого управляемого полевого транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для перемножения аналоговых сигналов | 1986 |

|

SU1388906A1 |

| Аналоговое множительное устройство | 1987 |

|

SU1497625A1 |

| Множительное устройство | 1980 |

|

SU924720A1 |

| Аналоговое множительное устройство | 1977 |

|

SU661561A1 |

| Аналоговое множительное устройство | 1985 |

|

SU1280401A1 |

| Множительно-делительное устройство | 1986 |

|

SU1405077A1 |

| Аналоговое множительное устройство | 1986 |

|

SU1319047A1 |

| Устройство для перемножения напряжений | 1983 |

|

SU1095197A1 |

| Множительно-делительное устройство | 1991 |

|

SU1791824A1 |

| Множительно-делительное устройство | 1984 |

|

SU1176347A1 |

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является повышение точности. Устройство для перемножения аналоговых сигналов содержит первый и второй управляемые полевые транзисторы 1 и 2, первый и второй операционные усилители 3 и 4, первый и второй масштабные резисторы 5 и 6, суммирующе-вычитающий блок 7, сумматор 8, дополнительный сумматор 9, блок разделения сигналов 10, выход 11, вход первого сигнала-сомножителя 12, вход напряжения смещения 13, вход второго сигнала-сомножителя 14. Работа устройства основана на регулировании проводимости управляемых полевых транзисторов 1 и 2 одним сигналом-сомножителем и передаче через канал сток - исток второго сигнала-сомножителя. 3 ил.

10}

19

фигЗ

| Аналоговое множительное устройство | 1977 |

|

SU661561A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для перемножения аналоговых сигналов | 1986 |

|

SU1388906A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-03-15—Публикация

1988-06-08—Подача