1

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Целью изобретения является повышение точности работы.

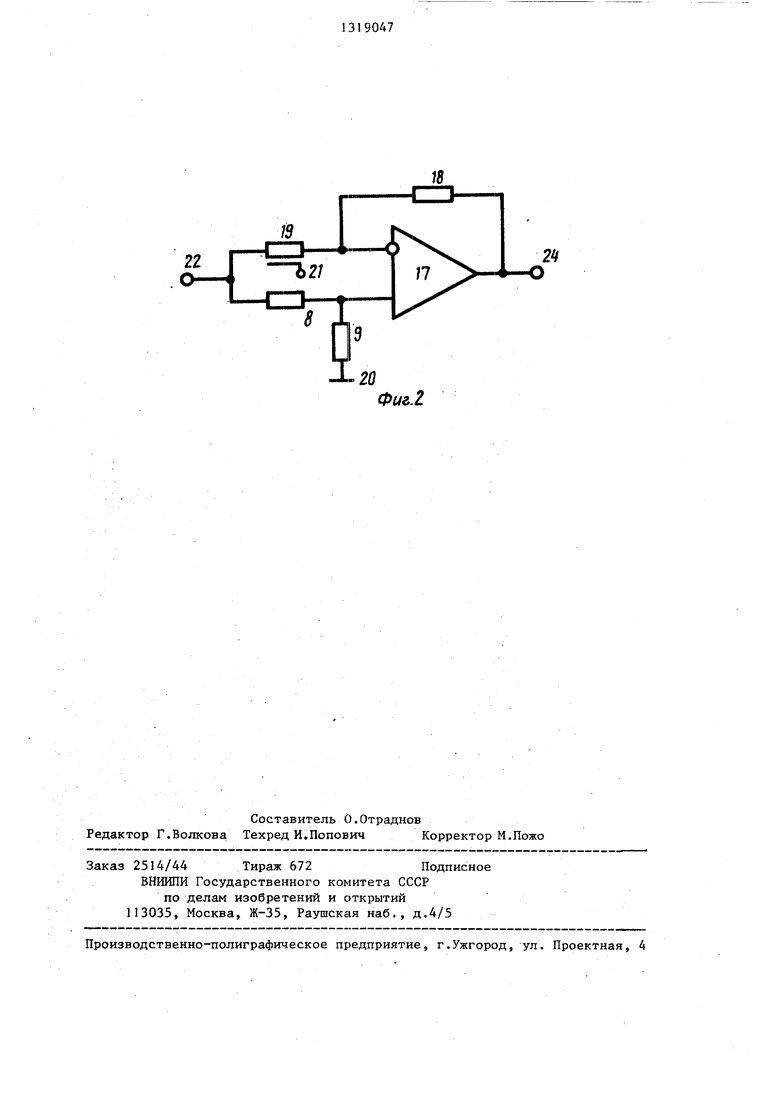

На фиг.1 дана функциональная схема аналогового множительного устройства; на фиг.2 - упрощенная схема устройства.

Устройство содержит первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый и одиннадцатый масштабные резисторы 1-11 соответственно, первый 12 и второй 13 резисторы смещения, балансировочный потенциометр 14 первый 15, второй 16 и третий 17 операционные усилители, первьй 18 и второй 19 полевые транзисторы, шина 20 нулевого потенциала, входы первого 21 и второго 22 сигналов-сом ножителей, вход 23 задания напряжения смещения, выход 24.

Устройство работает следующим образом.

Напряжение второго сигнала-сомножителя со входа 22 поступает на масштабный блок, образованный третьим операционным усилителем 17, первым 18 и вторым 19 полевыми транзисторами. Коэффициент усиления масштабного блока по инвертирующему входу равен отношению проводимости второго полевого транзистора 19 к проводи мости первого полевого транзистора 18.

Напряжение первого сигнала-сомножителя со входа 2 через второй one рационный усилитель 6 поступает на затвор второго полевого транзистора 19 и пропорционально изменяет его проводимость, т.е. коэффициент усиления масштабного блока изменяется пропорционально напряжению источника первого сигнала-сомножителя. В результате этого выходное напряжение масштабного блока, равное произведению его коэффициента усиления на напряжение источника второго сигнала-сомножителя, оказывается пропорциональным произведению напряжений первого и второго сигналов-сомножителей .

Для компенсации нелинейности ха- рактеристик первого 18 и второго 19 полевых транзисторов напряжение первого сигнала-сомножителя со входа

190472

21 подается через второй 16 и первьй 15 операционные усилители на затворы второго 19 и первого 18 полевых транзисторов, а напряжение с вы5 хода третьего операционного усилителя 17 подается через первый операционный усилитель 15 на затвор первого полевого транзистора 18. Кроме того, напряжение второго сигнала 0 сомножителя со входа 22 поступает

через делитель напряжения, образованной восьмым 8 и девятым 9 масштабными резисторами,на неинвертирующий вход третьего операционного усилите 5 ля для обеспечения равенства нулю напряжения на выходе 24 при равенстве нулю напряжения источника первого сигнала-сомножителя со входа 21. Напряжение смещения со входа 23

задает режим работы первого 18 и второго 19 полевых транзисторов в середине линейных участков их управляющих характеристик.

Балансировочный потенциометр 14 обеспечивает возможность устранения разбаланса устройства из-за неидентичности первого 18 и второго 19 полевых транзисторов.

В предложенном множительном устройстве .предусмотрена компенсация зависимости коэффициента передачи от температуры. Для анализа рассмотрим упрощенную функциональную схему 35 аналогового множительного устройства на фиг.2.

Коэффициент передачи описьшается выражением

40

45

V - л. f & ( 14

г р и ) {,q (jg+ b, GIB

где Gg , проводимости восьмого

8 и девятого 9 масштаб- . ных резисторов; G,g,G|,)- проводимости первого

18 и второго 19 полевых транзисторов.

Из выражения (Г) следует, что зависящие от температуры проводимости 50 первого 18 и второго 19 полевых транзисторов входят в выражение в виде отношения. Следовательно, при изменении их параметров от температуры отношение должно быть практически пос- 55 тоянным, особенно при идентичности полевых транзисторов.

Поэтому предложенное аналоговое множительное устройство характериэуется более высокой точностью работы за счет обеспечения эффекта термо ко тенсации параметров полевых транзисторов.

Формула изоб ре т е и и я

Аналоговое.множительное устройство, содержащее первый, второй и третий операционные усилители, первый и второй элементы с управляемым сопротивлением, выполненные соответственно на первом и втором полевых транзисторах, первый масштабный резистор, первый вывод которого сое- динен с неинвертирующим входом первого операционного усилителя и с первым вьшодом масштабного резистора, второй вьгоод которого подключен к стоку первого, полевого транзистора первый вьшод третьего масштабного резистора соединен с инвертирующим входом первого операционного усилителя, с первым вьюодом первого резистора смещения и с первым вьшодом четвертого масштабного резистора второй вывод которого подключен к выходу первого операционного усилителя и к затвору первого полевого транзистора, второй вьтод первого резистора смещения соединен с первым выводом балансировочного потенциометра, второй вьшод которого подключен к первому вьшоду второго резистора смещения, средний вьшод балансировочного потенциометра является входом задания напряжения смещения устройства, к неинвертирующе- ,му входу второго операционного усилителя подключены первые выводы пятого и шестого масштабных резисторов, первый вывод седьмого масштабного резистора соединен с инвертирующим входом второго операционного усилителя, выход которого подключен к затвору второго полевого транзистору исток которого соединен с истоком первого полевого транзистора, неинвертирующий вход третьего операционного усилителя соединен с первыми вьшодами восьмого и девятого масштабных резисторов, второй вьшод восьмого масштабного резистора подключен к стоку второго полевого транзистора, вторые вьшоды первого, третьего и шестого масштабных резисторов соединены с шиной нулевого потенциала, десятый и одиннадцатый масштабные резисторы, отличающееся тем, что, с целью повьште- ния точности работы, исток первого полевого транзистора соединен с инвертирующим входом третьего операционного усилителя, выход которого является выходом устройства и подключен к стоку первого полевого транзистора, второй вьшод седьмого мас- щтабного резистора соединен с выходом второго операционного усилителя, к инвертирующему входу которого подключены второй вьшод второго резистора смещения и первый вьшод десятого масштабного резистора, второй вьшод которого является входом первого сигнала-сомножителя, неинвертирующий вход первого операционного усилителя соединен с первым выводом одиннадцатого масштабного резистора, второй вьшод которого соединен с вторым вьшодом пятого масштабного резистора со стоком второго полевого транзистора и является входом второго сигнала-сомножителя , второй вывод девятого масштабного резистора . подключен к шине нулевого потенциала.

22

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительное устройство | 1980 |

|

SU924720A1 |

| Перемножающее устройство | 1983 |

|

SU1168971A1 |

| Аналоговое множительное устройство | 1985 |

|

SU1280401A1 |

| Множительно-делительное устройство | 1982 |

|

SU1030810A1 |

| Аналоговое множительное устройство | 1987 |

|

SU1497625A1 |

| Множительное устройство | 1977 |

|

SU667971A1 |

| Множительное устройство | 1982 |

|

SU1119037A1 |

| Аналоговое делительное устройство | 1982 |

|

SU1072061A1 |

| Множительно-делительное устройство | 1986 |

|

SU1405077A1 |

| Аналоговое множительное устройство | 1977 |

|

SU661561A1 |

Авторы

Даты

1987-06-23—Публикация

1986-01-22—Подача