Изобретение относится к вычислительной технике и может быть использовано для контроля электрических параметров и диагностики неисправностей цифровых и цифро-аналоговых блоков.

Цель изобретения - расширение области применения путем обеспечения контроля параметров аналоговых сигналов.

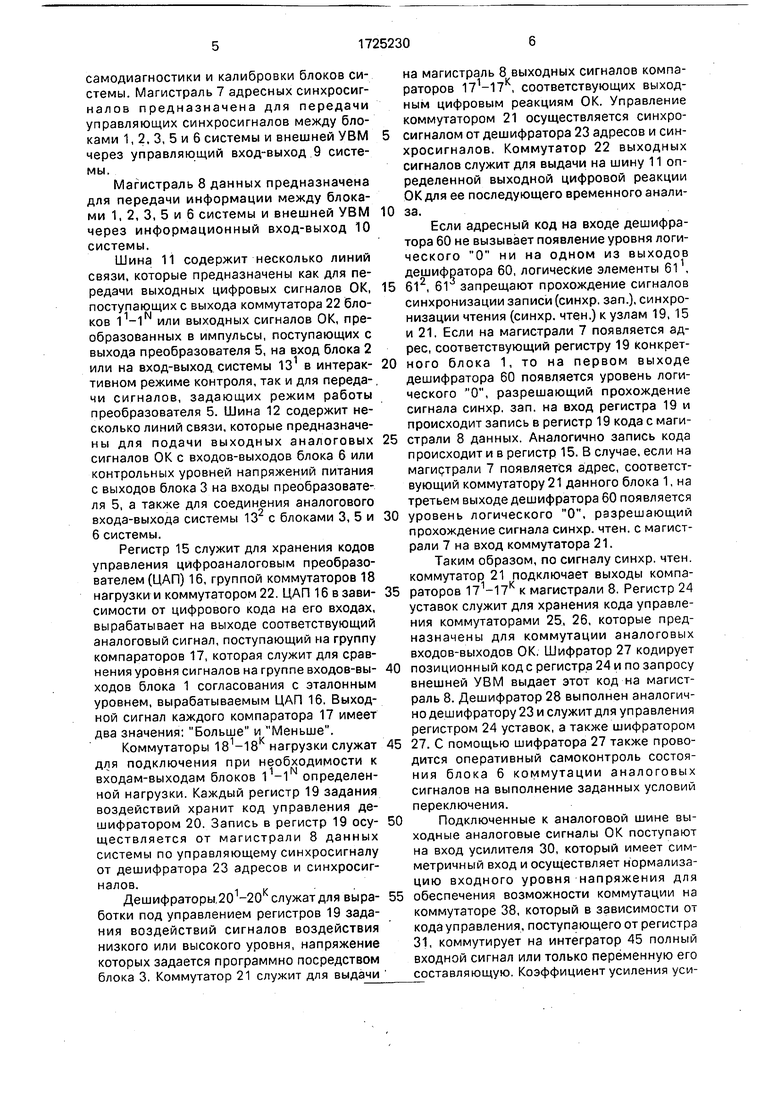

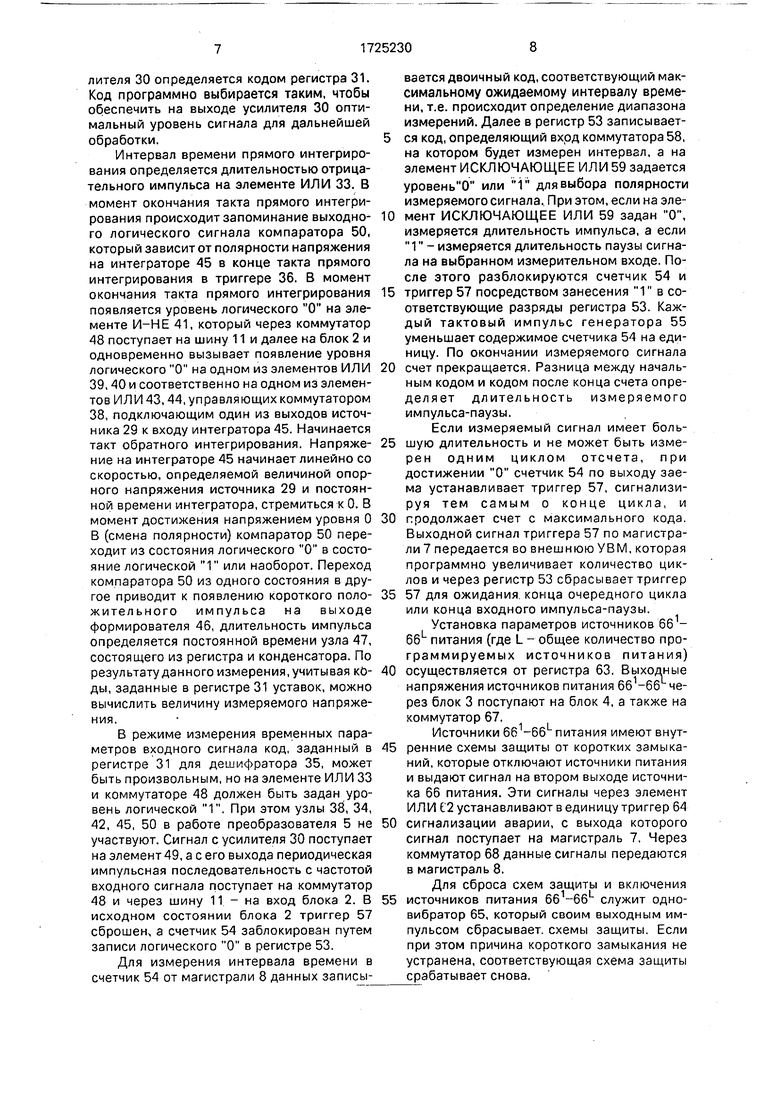

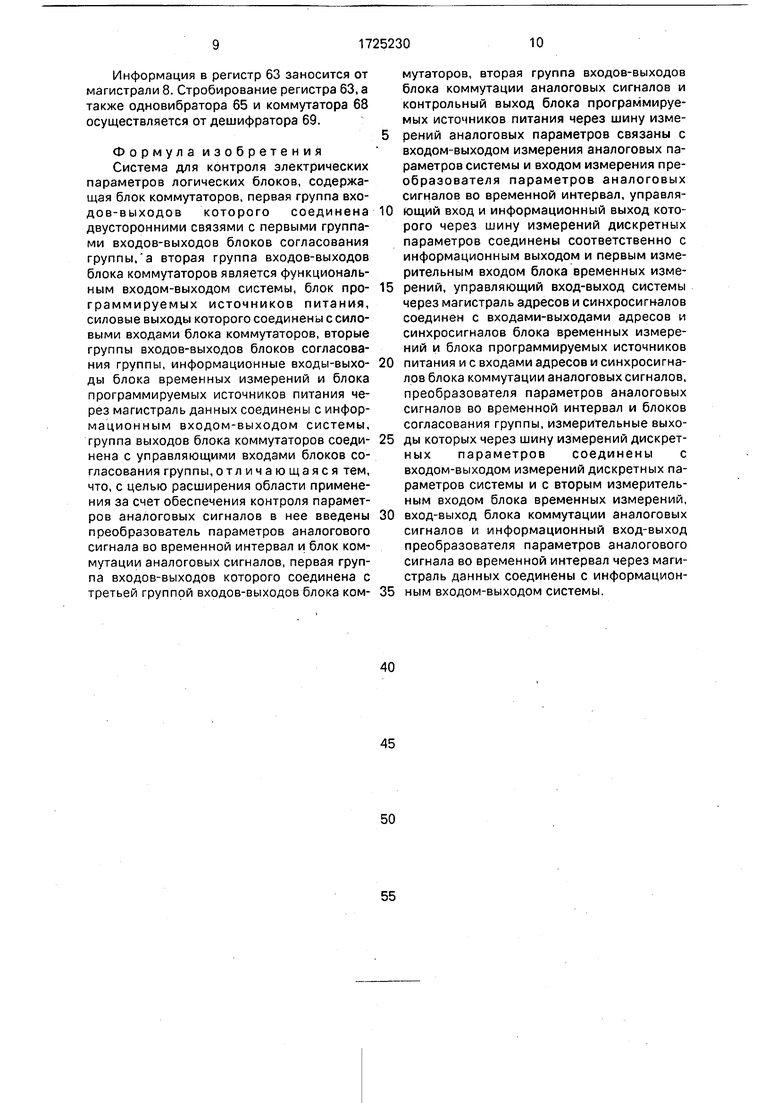

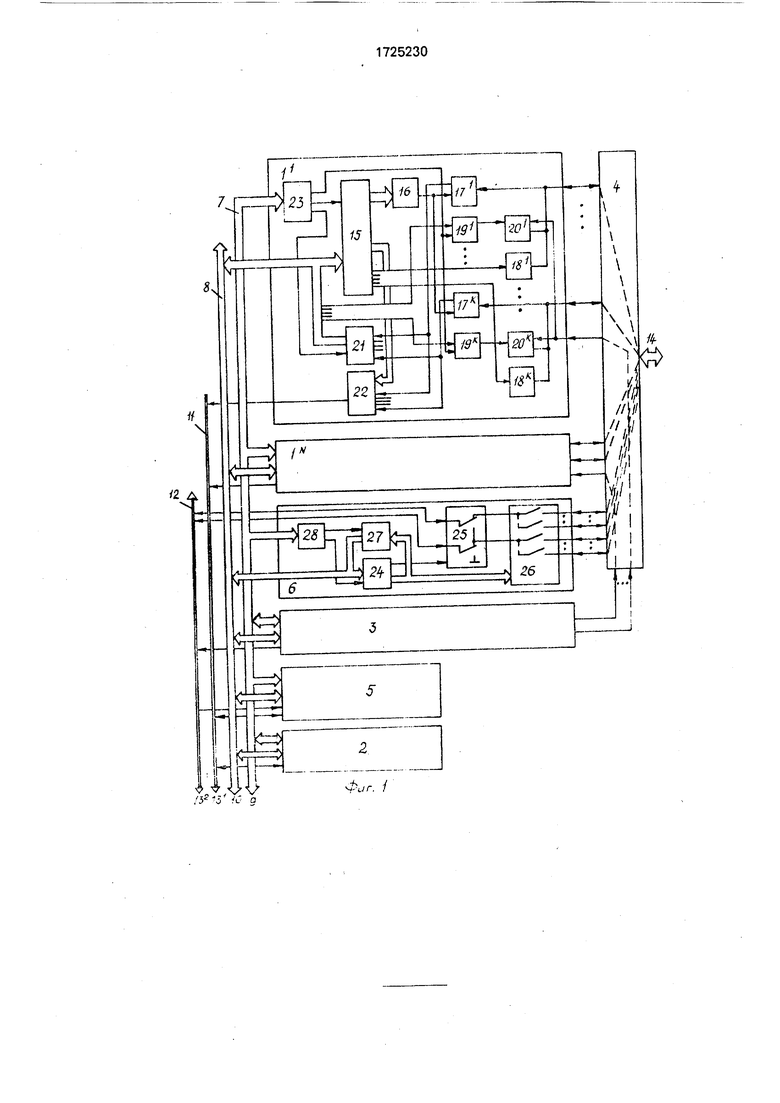

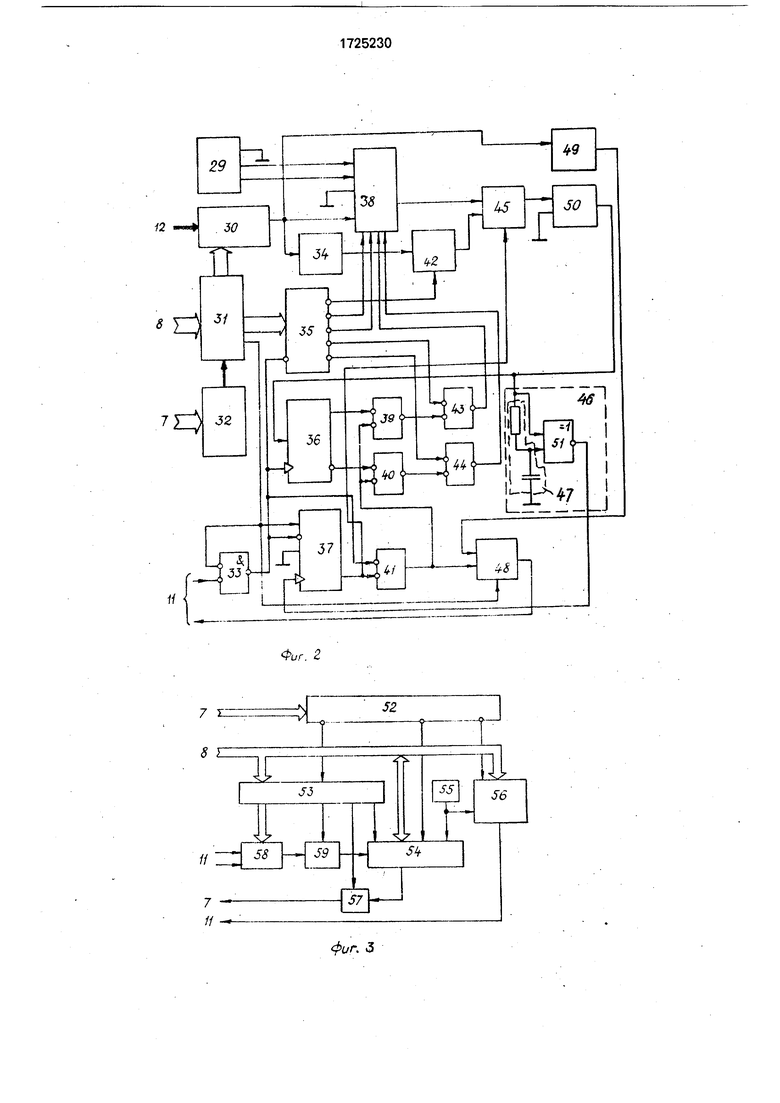

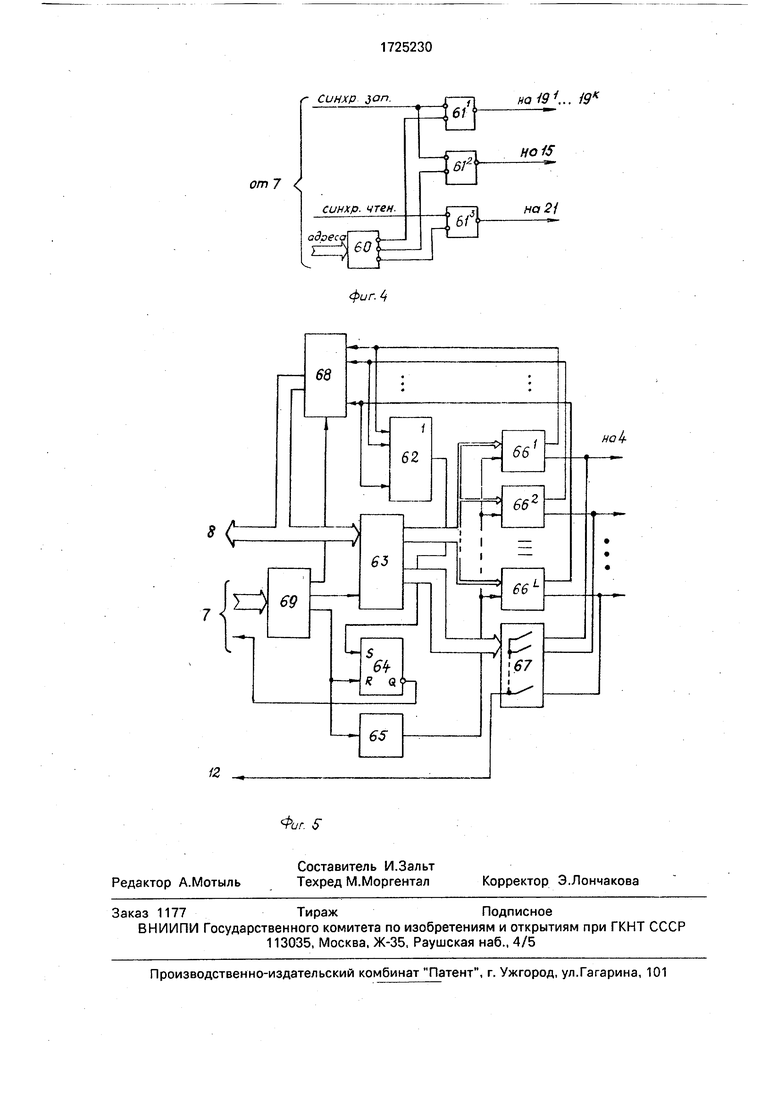

На фиг.1 представлена блок-схема устройства; на фиг,2 - функциональная схема преобразователя параметров аналогового сигнала во временной интервал; на фиг.З - функциональная схема блока временных измерений; на фиг.4 - функциональная схема дешифратора адресов и синхросигналов; на

фиг.5 - функциональная схема, блока программируемых источников питания.

Система содержит блоки 11-1 согласования, блок 2 временных измерений, блок 3 программируемых источников питания, блок 4 коммутаторов, преобразователь 5 параметров аналогового сигнала во временной интервал, блок 6 коммутации аналоговых сигналов, магистраль 7 адресных синхросигналов и магистраль 8 данных, управляющий вход-выход 9 системы, информационный вход-выход 10 системы, шину 11 измерений дискретных параметров и шину 12 измерений аналоговых параметров, вход-выход 131 измерений аналоговых параметров системы, вход-выход 13 измеXI ю сл

ГО СО О

рений параметров системы, функциональный вход-выход 14 системы.

Каждый блок 1 согласования состоит из регистра 15 уставок, цифроаналогового преобразователя 16, группы компараторов 17 - 17 , группы коммутаторов 181-18к нагрузки, группы регистров 191-19к задания воздействий, группы дешифраторов 201-20К, первого 21 и второго 22 коммутаторов выходных сигналов и дешифратора 23 адресов и синхросигналов.

Блок 6 коммутации аналоговых сигналов содержит регистр 24 уставок, коммутаторы 25,26 аналоговых сигналов, шифратор 27 и дешифратор 28 адресов и синхросигналов.

Преобразователь 5 содержит источник 29 опорных напряжений, усилитель 30 с переменным коэффициентом усиления, регистр 31 уставок, дешифратор 32 адресов и синхросигналов, первый элемент ИЛИ 33 (выполняющий функцию 2 НЕ-И- НЕ), инвертирующий однополупериодный выпрямитель 34, дешифратор 35, 6-тригге- ры 36, 37, коммутатор 38 аналоговых сигналов, второй и третий элементы ИЛИ 39, 40 (выполняющие функцию 2 НЕ-И-НЕ), элемент И-НЕ 41 (выполняющий функцию 2 НЕ-ИЛИ), аналоговый ключ 42, четвертый и пятый элементы ИЛИ 43, 44 (выполняющие функцию 2 НЕ-ИЛИ-НЕ), суммирующий интегратор 45, формирователь 46 импульса, интегрирующий узел 47, шестой коммутатор 48, пороговый элемент 49 (триггер Шмитта), аналоговый компаратор 50, первый логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 51.

Блок 2 временных измерений содержит дешифратор 52 адресов и синхросигналов, регистр 53 уставок, счетчик 54, тактовый генератор 55, формирователь 56 серий импульсов, триггер 57, седьмой коммутатор 58, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 59. Дешифратор 23 адресов и синхросигналов содержит дешифратор 60 и первый 611, второй 612, третий 613 логические элементы ИЛИ, выполняющие функцию 2 НЕ-И-НЕ.

Блок 3 программируемых источников питания содержит логический элемент ИЛИ 62, регистр 63 уставок, RS-триггер 64, одно- вибратор 65, группу источников питания 661-66L, аналоговый коммутатор 67, коммутатор 68, дешифратор 69 адресов и синхросигналов.

Блоки 1-1 предназначены для формирования входных цифровых воздействий заданного уровня и подачи их через блок 4 на входы объекта контроля (ОК), а также для сравнения выходных цифровых сигналов ОК, поступающих через блок 4, с заданными

пределами по амплитуде и передачи сигналов результата сравнения посредством коммутатора 21 через магистраль 8 данных на внешнююУВМ, а посредством коммутатора

5 22 - на блок 2 для дальнейшего анализа их временных параметров или взаимных временных соотношений.

Блок 2 предназначен для генерации временных интервалов и для определения

0 временных параметров и взаимных временных соотношений сигналов, поступающих по шине 11 от блоков 11-1N или от преобразователя 5 и передачи результата измерения на внешнюю УВМ через магистрали 7 и

5 8.

Блок 3 предназначен для выработки уровней напряжений питания группы дешифраторов 201-20К и ОК постоянными и переменными напряжениями, кроме того,

0 вырабатывается сигнал аварий источников питания и передает их на внешнюю УВМ.

Блок 4 предназначен для соединения входов-выходов блоков 11-1N, блока 6 сиг5 налов и блока 3 с требуемыми контрольными точками ОК через его выходной разъем или через внутрисхемные точки посредством игольчатого поля, входящего в состав блока 4. Последний содержит также, при

0 необходимости, специфичные пассивные нагрузочные элементы для обеспечения требуемых нагрузочных режимов аналоговых входов-выходов конкретного ОК.

Преобразователь 5 осуществляет при5 ем сигналов, поступающих по шине 12 от блока 3 или от блока 6, преобразование этих сигналов в одиночные импульсы с длительностью, пропорциональной среднему значению постоянного или перемен0 ного напряжения поступающих сигналов или в периодическую импульсную последовательность с частотой, равной частоте входного сигнала, и выдачу сформированных дискретных импульсов по шине 11 в

5 блок 2 для дальнейшей их обработки.

Блок 6 коммутирует выходные аналоговые сигналы ОК на шину 12 для осуществления амплитудных и временных измерений как в несимметричном, так и в дифференци0 альном режимах, коммутирует сигналы аналоговых воздействий, поступающие по шине 12 от блока 3 или от внешних стимулирующих приборов (через аналоговый вход- выход системы 13 на аналоговые входы О К,

5 осуществляет взаимную коммутацию аналоговых входов-выходов ОКдля обеспечения заданных связей или нагрузочных режимов, а также осуществляет коммутацию сигналов аналоговых воздействий системы в шине 12

на вход преобразователя 5 для проведения

самодиагностики и калибровки блоков системы. Магистраль 7 адресных синхросиг- налов предназначена для передачи управляющих синхросигналов между блоками 1, 2, 3, 5 и 6 системы и внешней УВМ через управляющий вход-выход 9 системы.

Магистраль 8 данных предназначена для передачи информации между блоками 1, 2, 3, 5 и 6 системы и внешней УВМ через информационный вход-выход 10 системы.

Шина 11 содержит несколько линий связи, которые предназначены как для передачи выходных цифровых сигналов ОК, поступающих с выхода коммутатора 22 блоков 11-1N или выходных сигналов ОК, преобразованных в импульсы, поступающих с выхода преобразователя 5, на вход блока 2 или на вход-выход системы 131 в интерактивном режиме контроля, так и для переда-, чи сигналов, задающих режим работы преобразователя 5. Шина 12 содержит несколько линий связи, которые предназначе- ны для подачи выходных аналоговых сигналов ОК с входов-выходов блока 6 или контрольных уровней напряжений питания с выходов блока 3 на входы преобразователя 5, а также для соединения аналогового входа-выхода системы 13 с блоками 3, 5 и 6 системы.

Регистр 15 служит для хранения кодов управления цифроаналоговым преобразователем (ЦАП) 16, группой коммутаторов 18 нагрузки и коммутатором 22. ЦАП 16 в зависимости от цифрового кода на его входах, вырабатывает на выходе соответствующий аналоговый сигнал, поступающий на группу компараторов 17, которая служит для сравнения уровня сигналов на группе входов-выходов блока 1 согласования с эталонным уровнем, вырабатываемым ЦАП 16, Выходной сигнал каждого компаратора 17 имеет два значения: Больше и Меньше.

Коммутаторы 18-18 нагрузки служат для подключения при необходимости к входам-выходам блоков 11-1N определенной нагрузки. Каждый регистр 19 задания воздействий хранит код управления дешифратором 20. Запись в регистр 19 осуществляется от магистрали 8 данных системы по управляющему синхросигналу от дешифратора 23 адресов и синхросигналов.

Дешифраторы,201-20к служат для выработки под управлением регистров 19 задания воздействий сигналов воздействия низкого или высокого уровня, напряжение которых задается программно посредством блока 3. Коммутатор 21 служит для выдачи

на магистраль 8 выходных сигналов компараторов 171-17к, соответствующих выходным цифровым реакциям ОК. Управление коммутатором 21 осуществляется синхросигналом от дешифратора 23 адресов и синхросигналов. Коммутатор 22 выходных сигналов служит для выдачи на шину 11 определенной выходной цифровой реакции ОК для ее последующего временного анали0 за.

Если адресный код на входе дешифратора 60 не вызывает появление уровня логического О ни на одном из выходов дешифратора 60, логические элементы 611,

5 612, 61 запрещают прохождение сигналов синхронизации записи (синхр. зап.), синхронизации чтения (синхр. чтен.) к узлам 19, 15 и 21. Если на магистрали 7 появляется адрес, соответствующий регистру 19 конкрет0 ного блока 1, то на первом выходе дешифратора 60 появляется уровень логического О, разрешающий прохождение сигнала синхр, зап. на вход регистра 19 и происходит запись в регистр 19 кода с маги5 страли 8 данных. Аналогично запись кода происходит и в регистр 15. В случае, если на магистрали 7 появляется адрес, соответствующий коммутатору 21 данного блока 1, на третьем выходе дешифратора 60 появляется

0 уровень логического О, разрешающий прохождение сигнала синхр. чтен. с магистрали 7 на вход коммутатора 21.

Таким образом, по сигналу синхр. чтен. коммутатор 21 подключает выходы компа5 раторов 171-17к к магистрали 8. Регистр 24 уставок служит для хранения кода управления коммутаторами 25, 26, которые предназначены для коммутации аналоговых входов-выходов ОК, Шифратор 27 кодирует

0 позиционный коде регистра 24 и по запросу внешней УВМ выдает этот код на магистраль 8. Дешифратор 28 выполнен аналогично дешифратору 23 и служит для управления регистром 24 уставок, а также шифратором

5 27. С помощью шифратора 27 также проводится оперативный самоконтроль состояния блока 6 коммутации аналоговых сигналов на выполнение заданных условий переключения.

0 Подключенные к аналоговой шине выходные аналоговые сигналы ОК поступают на вход усилителя 30, который имеет симметричный вход и осуществляет нормализацию входного уровня напряжения для

5 обеспечения возможности коммутации на коммутаторе 38, который в зависимости от кода управления, поступающего от регистра 31, коммутирует на интегратор 45 полный входной сигнал или только переменную его составляющую. Коэффициент усиления усилителя 30 определяется кодом регистра 31. Код программно выбирается таким, чтобы обеспечить на выходе усилителя 30 оптимальный уровень сигнала для дальнейшей обработки.

Интервал времени прямого интегрирования определяется длительностью отрицательного импульса на элементе ИЛИ 33. В момент окончания такта прямого интегрирования происходит запоминание выходного логического сигнала компаратора 50, который зависит от полярности напряжения на интеграторе 45 в конце такта прямого интегрирования в триггере 36. В момент окончания такта прямого интегрирования появляется уровень логического О на элементе И-НЕ 41, который через коммутатор 48 поступает на шину 11 и далее на блок 2 и одновременно вызывает появление уровня логического О на одном из элементов ИЛИ 39,40 и соответственно на одном из элементов ИЛ И 43,44, управляющих коммутатором 38, подключающим один из выходов источника 29 к входу интегратора 45. Начинается такт обратного интегрирования. Напряжение на интеграторе 45 начинает линейно со скоростью, определяемой величиной опорного напряжения источника 29 и постоянной времени интегратора, стремиться к 0. В момент достижения напряжением уровня О В (смена полярности) компаратор 50 переходит из состояния логического О в состояние логической 1 или наоборот. Переход компаратора 50 из одного состояния в другое приводит к появлению короткого положительного импульса на выходе формирователя 46, длительность импульса определяется постоянной времени узла 47, состоящего из регистра и конденсатора. По результату данного измерения, учитывая коды, заданные в регистре 31 уставок, можно вычислить величину измеряемого напряжения.

В режиме измерения временных параметров входного сигнала код, заданный в регистре 31 для дешифратора 35, может быть произвольным, но на элементе ИЛИ 33 и коммутаторе 48 должен быть задан уровень логической 1. При этом узлы 38 34, 42, 45, 50 в работе преобразователя 5 не участвуют. Сигнал с усилителя 30 поступает на элемент 49, а с его выхода периодическая импульсная последовательность с частотой входного сигнала поступает на коммутатор 48 и через шину 11 - на вход блока 2. В исходном состоянии блока 2 триггер 57 сброшен, а счетчик 54 заблокирован путем записи логического О в регистре 53.

Для измерения интервала времени в счетчик 54 от магистрали 8 данных записывается двоичный код, соответствующий максимальному ожидаемому интервалу времени, т.е. происходит определение диапазона измерений. Далее в регистр 53 записывает- ся код, определяющий вход коммутатора 58, на котором будет измерен интервал, а на элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 59 задается уровень 0 или 1 для выбора полярности измеряемого сигнала. При этом, если на эле0 мент ИСКЛЮЧАЮЩЕЕ ИЛИ 59 задан О, измеряется длительность импульса, а если 1 - измеряется длительность паузы сигнала на выбранном измерительном входе. После этого разблокируются счетчик 54 и

5 триггер 57 посредством занесения 1 в соответствующие разряды регистра 53. Каждый тактовый импульс генератора 55 уменьшает содержимое счетчика 54 на единицу. По окончании измеряемого сигнала

0 счет прекращается. Разница между начальным кодом и кодом после конца счета определяет длительность измеряемого импульса-паузы.

Если измеряемый сигнал имеет боль5 шую длительность и не может быть измерен одним циклом отсчета, при достижении О счетчик 54 по выходу зае- ма устанавливает триггер 57, сигнализируя тем самым о конце цикла, и

0 продолжает счет с максимального кода. Выходной сигнал триггера 57 по магистрали 7 передается во внешнюю УВМ, которая программно увеличивает количество циклов и через регистр 53 сбрасывает триггер

5 57 для ожидания, конца очередного цикла или конца входного импульса-паузы.

Установка параметров источников 66 - 66L питания (где L - общее количество программируемых источников питания)

0 осуществляется от регистра 63. Выходные напряжения источников питания 661-66 через блок 3 поступают на блок 4, а также на коммутатор 67.

Источники 661-66L питания имеют внут5 ренние схемы защиты от коротких замыканий, которые отключают источники питания и выдают сигнал на втором выходе источника 66 питания. Эти сигналы через элемент ИЛИ €2 устанавливают в единицу триггер 64

0 сигнализации аварии, с выхода которого сигнал поступает на магистраль 7. Через коммутатор 68 данные сигналы передаются в магистраль 8.

Для сброса схем защиты и включения

5 источников питания 661-66 служит одно- вибратор 65, который своим выходным импульсом сбрасывает, схемы защиты. Если при этом причина короткого замыкания не устранена, соответствующая схема защиты срабатывает снова.

Информация в регистр 63 заносится от магистрали 8. Стробирование регистра 63, а также одновибратора 65 и коммутатора 68 осуществляется от дешифратора 69.

Ф о р м у л а и з о б р е т е н и я Система для контроля электрических параметров логических блоков, содержащая блок коммутаторов, первая группа вхо- дов-выходов которого соединена двусторонними связями с первыми группами входов-выходов блоков согласования группы, а вторая группа входов-выходов блока коммутаторов является функциональным входом-выходом системы, блок про- граммируемых источников питания, силовые выходы которого соединены с силовыми входами блока коммутаторов, вторые группы входов-выходов блоков согласования группы, информационные входы-выхо- ды блока временных измерений и блока программируемых источников питания через магистраль данных соединены с инфор- мационным входом-выходом системы, группа выходов блока коммутаторов соеди- нена с управляющими входами блоков согласования группы, отл и ч а ю щаяся тем, что, с целью расширения области применения за счет обеспечения контроля параметров аналоговых сигналов в нее введены преобразователь параметров аналогового сигнала во временной интервал и блок коммутации аналоговых сигналов, первая группа входов-выходов которого соединена с третьей группой входов-выходов блока ком-

мутаторов, вторая группа входов-выходов блока коммутации аналоговых сигналов и контрольный выход блока программируемых источников питания через шину измерений аналоговых параметров связаны с входом-выходом измерения аналоговых параметров системы и входом измерения преобразователя параметров аналоговых сигналов во временной интервал, управляющий вход и информационный выход которого через шину измерений дискретных параметров соединены соответственно с информационным выходом и первым измерительным входом блока временных измерений, управляющий вход-выход системы через магистраль адресов и синхросигналов соединен с входами-выходами адресов и синхросигналов блока временных измерений и блока программируемых источников питания и с входами адресов и синхросигналов блока коммутации аналоговых сигналов, преобразователя параметров аналоговых сигналов во временной интервал и блоков согласования группы, измерительные выходы которых через шину измерений дискрет- ных параметров соединены с входом-выходом измерений дискретных параметров системы и с вторым измерительным входом блока временных измерений, вход-выход блока коммутации аналоговых сигналов и информационный вход-выход преобразователя параметров аналогового сигнала во временной интервал через магистраль данных соединены с информационным входом-выходом системы.

/LA W

| название | год | авторы | номер документа |

|---|---|---|---|

| Автоматизированная система контроля | 1989 |

|

SU1695269A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1980 |

|

SU907556A1 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

| Многоканальное устройство для сбора данных | 1983 |

|

SU1095163A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПАРАМЕТРОВ | 1996 |

|

RU2106679C1 |

| Устройство для автоматизированного контроля источников питания | 1986 |

|

SU1366978A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ЭЛЕКТРОДВИГАТЕЛЕМ СУДОВОЙ ЛЕБЕДКИ | 1994 |

|

RU2074501C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1988 |

|

SU1683244A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля электрических параметров и диаг- ностики непрерывностей цифровых и циф- роаналоговых блоков. Цель изобретения - расширение области применения путем обеспечения контроля параметров аналоговых сигналов. Цель достигается за счет введения преобразователя параметров аналогового сигнала во временной интервал и блока коммутации аналоговых сигналов. Изобретение позволяет обеспечить измерение амплитудных (в т.ч. и высоковольтных) и временных параметров аналоговых сигналов, временных взаимоотношений цифровых и аналоговых сигналов, коммутацию аналоговых выходов объекта контроля между собой или для осуществления дифференциальных измерений, а также для подключения требуемой нагрузки.5 ил. сл

. ГУ

uU

/i Y,О j L

//;

7

ii

л

фиг. 3

л

С Синхр jan

юЯ1... 19

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Авторское свидетельство СССР №1154680, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-07—Публикация

1988-12-12—Подача