1

Изобретение-относится к технике связи, а именно к технике передачи дискретных данных и может быть использовано в устройствах автоматической подстройки частоты для обеспечения синхронной работы в системах передачи-приема дискретной информации.

Известно дискретное устройство синхронизации, содержащее блок выделения фронтов и последовательно соединенные задающий генератор, блок управления и управляемый делитель ij.

Однако такое устройство обладает малым частотным диапазоном синхронизации и не обеспечивает выполнения условия синхронизации при приеме сигналов большой скважности.

-Целью изобретения является расшиоение частотного диапазона

Для этого в дискретное устройство синхронизации, содержащее блок выделения фронтов и последовательно соединенные задающий генератор, блок управления, управляемый делитель, введены регистр задержки, регистр памяти, сумматор, элементы ИЛИ, И, ИЛИ-НЕ, .коммутатор и дешифратор, выход которого через последовательно соединенные регистр задержки,элементы И и ИЛИ-НЕ подключен к другому входу блока управления. Выходблока выделения фронтов подключен .к первому входу регистра памяти и соответственно через коммутатор и через элемент ИЛИ к соответствующим входам управляемого делителя, выход которого подключен к входам деишфратора. Выходы регистра памяти подключены

10 ко входам сумматора, первый выход которого подключен к другому входу элемента И, а вторые выходы - к вторым входам регистра памяти, третий вход которого соединен с вторым дом элемента ИЛИ-НЕ, другим входом элемента ИЛИ и другим выходом регистра задержки, второй вход которого соединен с выходом задающего генератора и входом блока выделения фронтов, выход которого подключен к

третьему входу элемента ИЛИ-НЕ. Другие входы сумматора и коммутатора объединены.

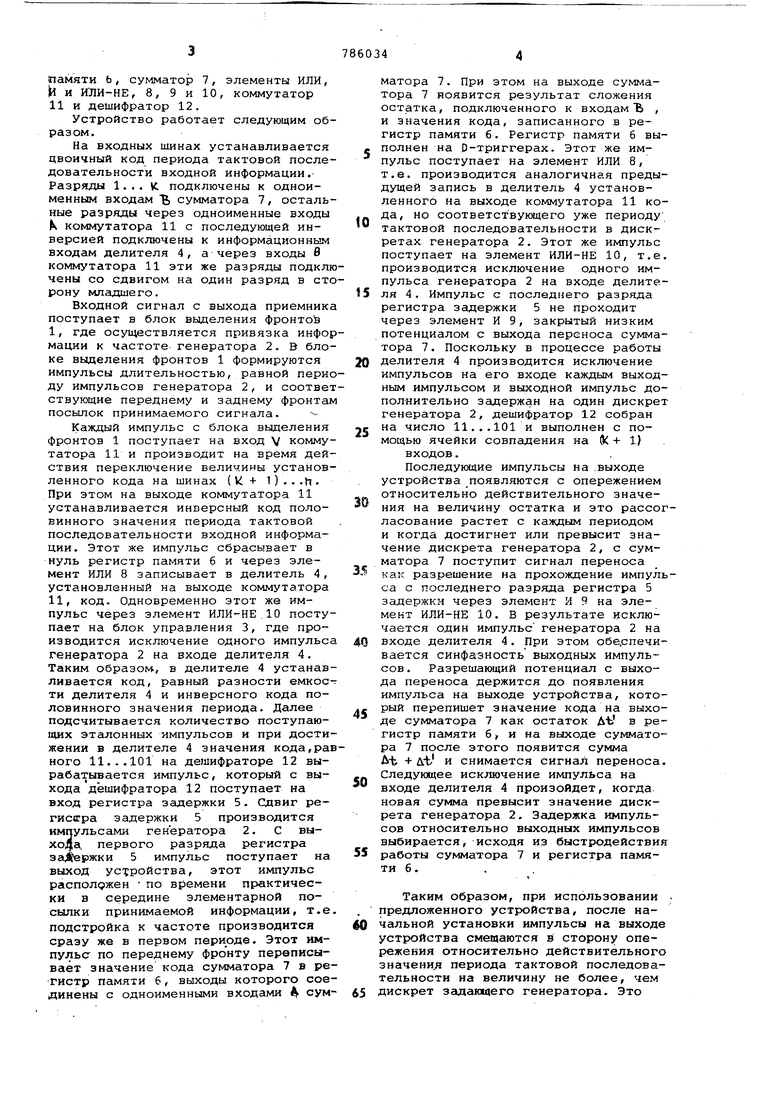

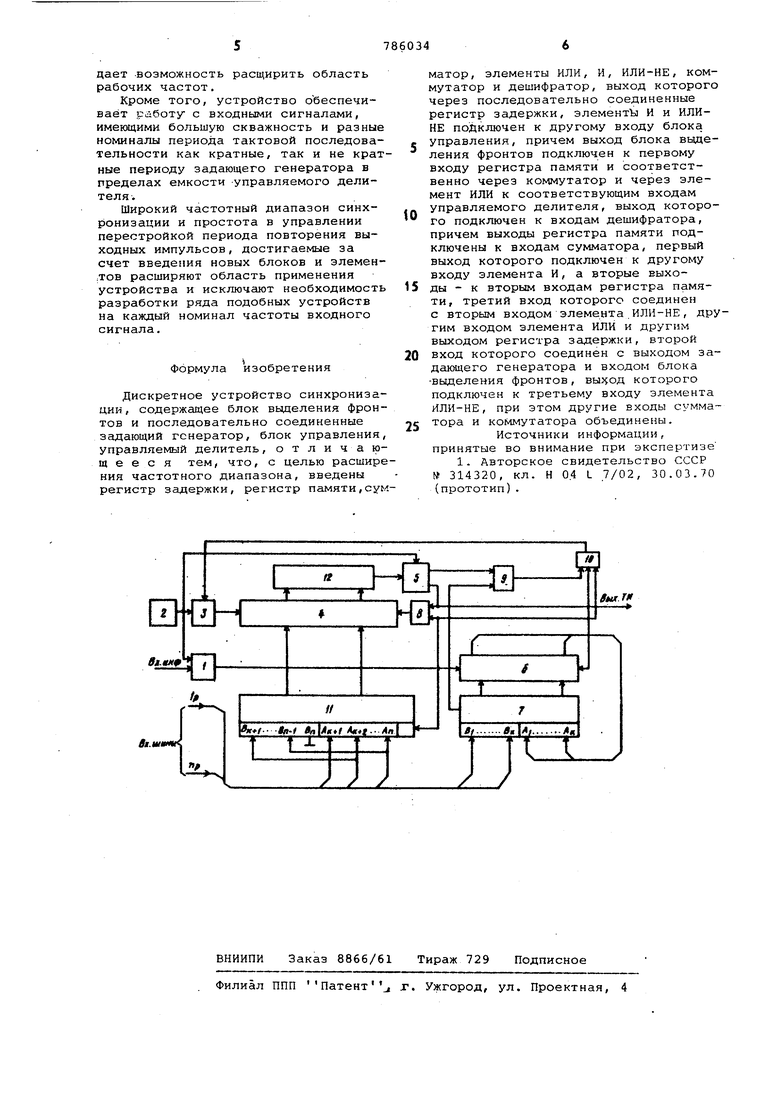

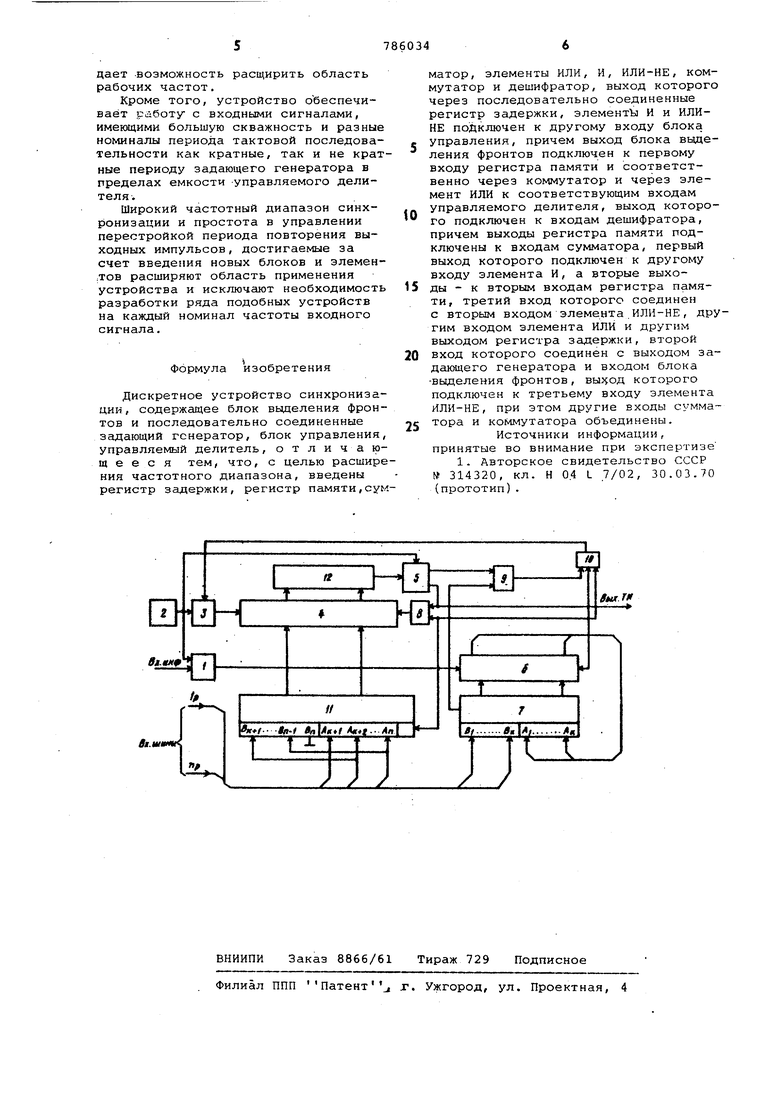

На чертеже приведена функциональ2$ ная электрическая схема предложенного устройства..

Устройство содержит блок вьаделения фронтов 1, задающий генератор 2, блок управления 3, управляемый дели3Q тель 4, регистр задержки 5, регистр

Памяти Ь, сумматор 7, элементы ИЛИ, И и H7IH-HE, 8, 9 и 10, коммутатор 11 и дешифратор 12.

Устройство работает следующим образом.

На входных шинах устанавливается двоичный код периода тактовой последовательности входной информации. Разряды 1... It подключены к одноименным входам В сумматора 7, остальные разряды через одноименные входы К коммутатора 11 с последующей инверсией подключены к информационным входам делителя 4, а через входы В коммутатора 11 эти же разряды подключены со сдвигом на один разряд в сторону младшего.

Входной сигнал с выхода приемника поступает в блок выделения фронто в

I,где осуи ествляется привязка информации к частоте генератора 2, В блоке выделения фронтов 1 формируются импульсы длительностью, равной периоду импульсов генератора 2, и соответствующие переднему и заднему фронтам посылок принимаемого сигнала. Каждый импульс с блока выделения фронтов 1 поступает на вход V коммутатора 11 и производит на время действия переключение величины установленного кода на шинах ( k. + 1) . . .h . При этом на выходе коммутатора 11 устанавливается инверсный код половинного значения периода тактовой последовательности входной информации. Этот же импульс сбрасывает в нуль регистр памяти б и через элемент ИЛИ 8 записывает в делитель 4, установленный на выходе коммутатора

II,код. Одновременно этот же импульс через элемент ИЛИ-НЕ 10 поступает на блок управления 3, где производится исключение одного импульса генератора 2 на входе делителя 4. Таким образом, в делителе 4 устанавливается код, равный разности емкости делителя 4 и инверсного кода половинного значения периода. Далее подсчитывается количество поступающих эталонных импульсов и при достижении в делителе 4 значения кода,равного 11...101 на дешифраторе 12 вырабатывается импульс, который с выхода дешифратора 12 поступает на вход регистра задержки 5. Сдвиг регисогра задержки 5 производится импульсами генератора 2. С выхоДа. первого разряда регистра зajtepжки 5 импульс поступает на выход устройства, этот импульс располржен по времени практически в середине элементарной посылки принимаемой информации, т.е подстройка к частоте производится сразу же в первом периоде. Этот импу.пьс по переднему фронту переписывает значение кода сумматора 7 в регистр памяти б, выходы которого соединены с одноименными входами сумматора 7. При этом на выходе сумматора 7 появится результат сложения остатка, подключенного к входам Ъ , и значения кода, записанного в регистр памяти б. Регистр памяти б выполнен на D-триггерах. Этот же импульс поступает на элемент ИЛИ 8, т.е. производится аналогичная предыдущей запись в делитель 4 установленного на выходе коммутатора 11 кода, но соответствующего уже периоду тактовой последовательности в дискретах генератора 2. Этот же импульс поступает на элемент ИЛИ-НЕ 10, т.е производится исключение одного импульса генератора 2 на входе делителя 4. Импульс с последнего разряда регистра задержки 5 не проходит через элемент И 9, закрытый низким потенциалом с выхода переноса сумматора 7. Поскольку в процессе работы делителя 4 производится исключение импульсов на его входе Кс1ждь1м выходным импульсом и выходной импульс дополнительно задержан на один дискрет генератора 2, дешифратор 12 собран на число 11... 101 и выполнен с помощью ячейки совпсщения на (k + 1)

входов.

Последующие импульсы на .выходе устройства появляются с опережением относительно действительного значения на величину остатка и это рассогласование растет с каждым периодом и когда достигнет или превысит значение дискрета генератора 2, с сумматора 7 поступит сигнал переноса как разрешение на прохождение импульса с последнего разряда регистра 5 задержки через элемент И 9 на элемент ИЛИ-НЕ 10. В результате исключается один импульс генератора 2 на входе делителя 4. При этом обе.спечивается синфазность выходных импульсов . Разрешающий потенциал с выхода переноса держится до появления импульса на выходе устройства, который перепишет значение кода на выходе сумматора 7 как остаток ДЪ в регистр памяти б, и на выходе сумматора 7 после этого появится сумма Л-fc + Д-Ъ и снимается сигнал переноса. Следующее исключение импульса на входе делителя 4 произойдет, когда новая сумма превысит значение дискрета генератора 2. Задержка импульсов относительно выходных импульсов выбирается, исходя из быстродействия работы сумматора 7 и регистра памяти 6.

Таким образом, при использовании предложенного устройства, после начальной установки импульсы на выходе устройства смещаются в сторону опережения относительно действительного значение периода тактовой последовательности на величину не более, чем дискрет задающего генератора. Это дает возможность расщирить область рабочих частот. Кроме того, устройство обеспечиваёт работу с входными сигналами, имеющими большую скважность и разны номиналы периода тактовой последова тельности как кратные, так и не кра ные периоду задающего генератора в пределах емкости управляемого делителя. Широкий частотный диапазон синхронизации и простота в управлении перестройкой периода повторения выходных импульсов, достигаемые за счет введения новых блоков и элемен ,тов расширяют область применения устройства и исключают необходимост разработки ряда подобных устройств на каждый номинал частоты входного сигнала. Формула изобретения Дискретное устройство синхрониз ции, содержащее блок выделения фро тов и последовательно соединенные задающий генератор, блок управлени управляемый делитель, отлича щееся тем, что, с целью расши ния частотного диапазона, введены регистр задержки, регистр памяти,с матор, элементы ИЛИ, И, ИЛИ-НЕ, коммутатор и дешифратор, выход которого через последовательно соединенные регистр задержки, элементЪ И и ИЛИНЕ подключен к другому входу блока управления, причем выход блока выделения фронтов подключен к первому входу регистра памяти и соответственно через коммутатор и через элемент ИЛИ к соответствующим входам управляемого делителя, выход которого подключен к входам дешифратора, причем выходы регистра памяти подключены к входам сумматора, первый выход которого подключен к другому входу элемента И, а вторые выходы - к вторым входам регистра памяти, третий вход которого соединен с вторым входом элемента.ИЛИ-НЕ, другим входом элемента ИЛИ и другим выходом регистра задержки, второй вход которого соединен с выходом задающего генератора и входом блока -выделения фронтов, которого подключен к третьему входу элемента ИЛИ-НЕ, при этом другие входы сумматора и коммутатора объединены. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 314320, кл. Н 0.4 L 7/02, 30.03.70 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискретное устройство синхронизации | 1982 |

|

SU1109928A2 |

| Формирователь сложного сигнала с частотной и частотно-фазовой манипуляцией | 1982 |

|

SU1136323A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Устройство задержки импульсов | 1980 |

|

SU917326A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| Устройство тактовой синхронизациии РЕгЕНЕРАции | 1979 |

|

SU809620A1 |

| Генератор циклов | 1981 |

|

SU995289A1 |

| Устройство синхронизации двоичных сигналов в приемной аппаратуре многоканальной системы связи | 1981 |

|

SU1083389A1 |

| Устройство для дискретной регулировки фазы | 1987 |

|

SU1450079A1 |

Авторы

Даты

1980-12-07—Публикация

1979-01-29—Подача