Изобретение относится к вычислительной технике и может быть использовано при экспериментальном иссле- . довании надежности структурно-избыточных вычислительных систем (ВС), в частности при исследовании аппаратно-программных средств обеспечения надежности и устойчивости функционирования вычислительного процесса.

Цель изобретения - расширение функциональных возможностей устройства за счет выявления кратных неисправностей .

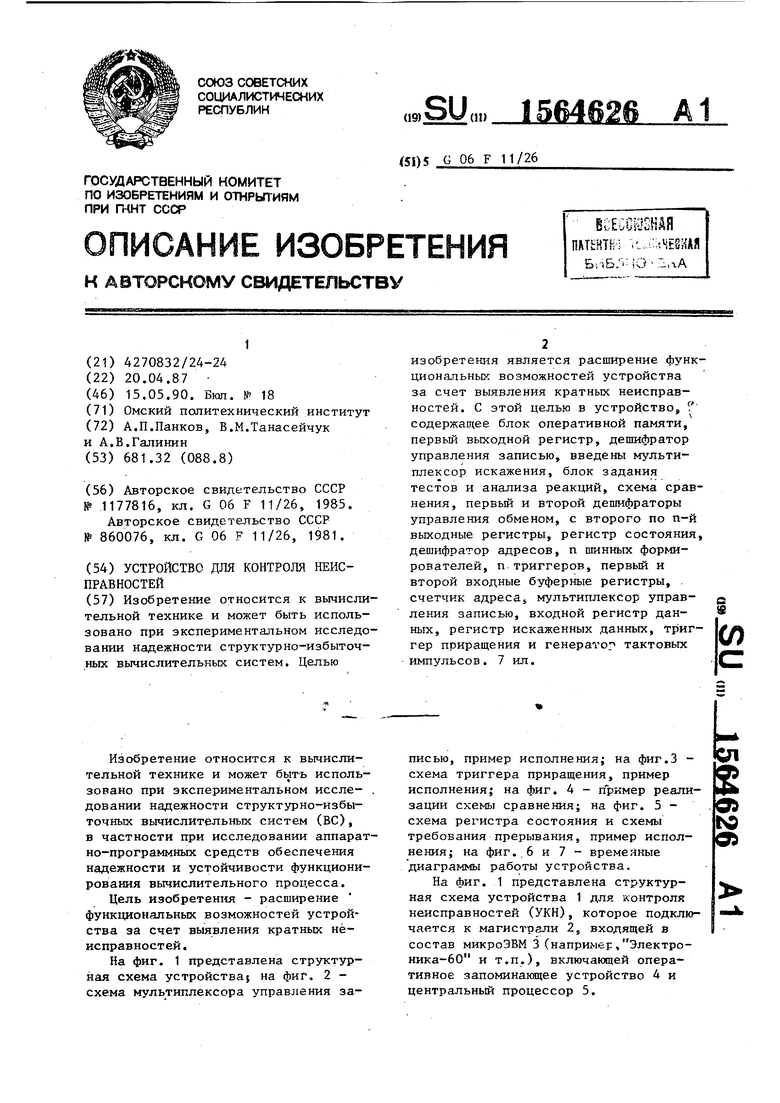

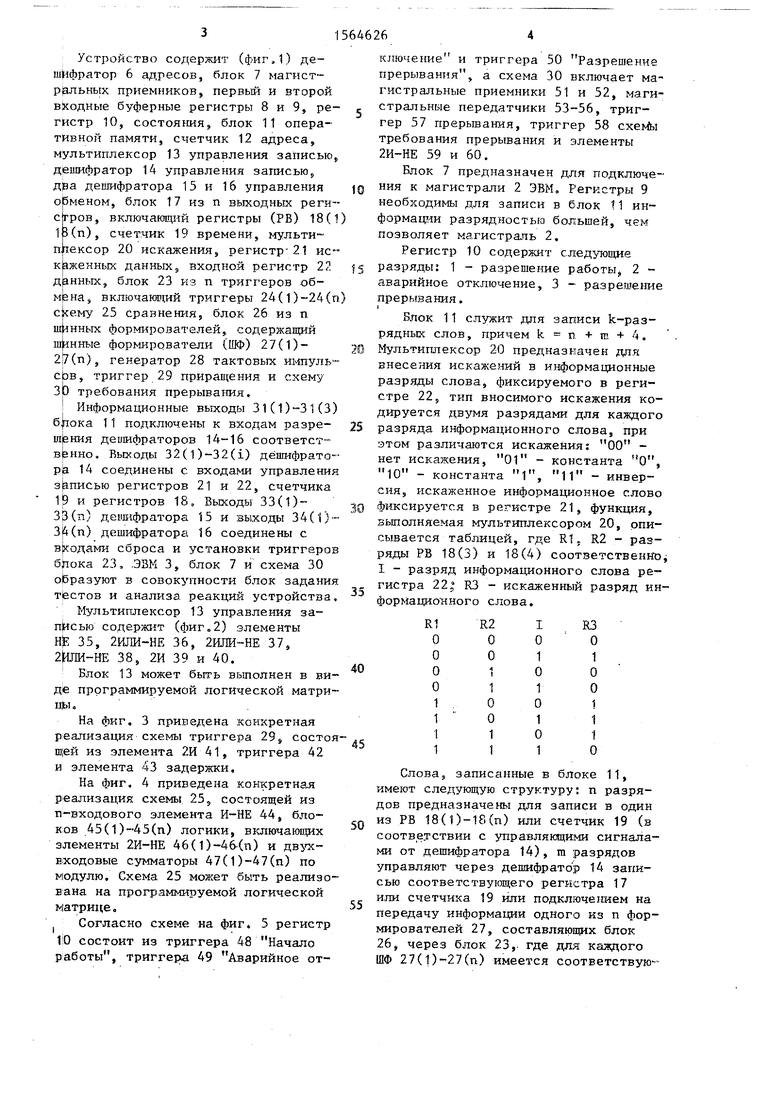

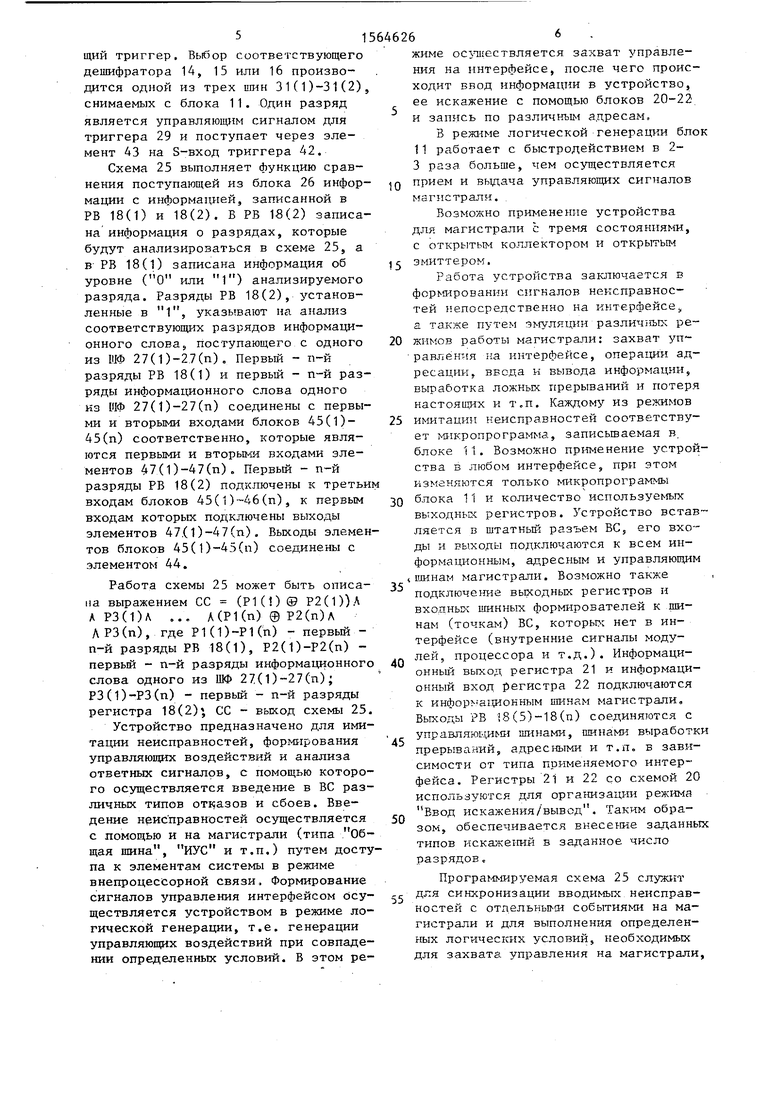

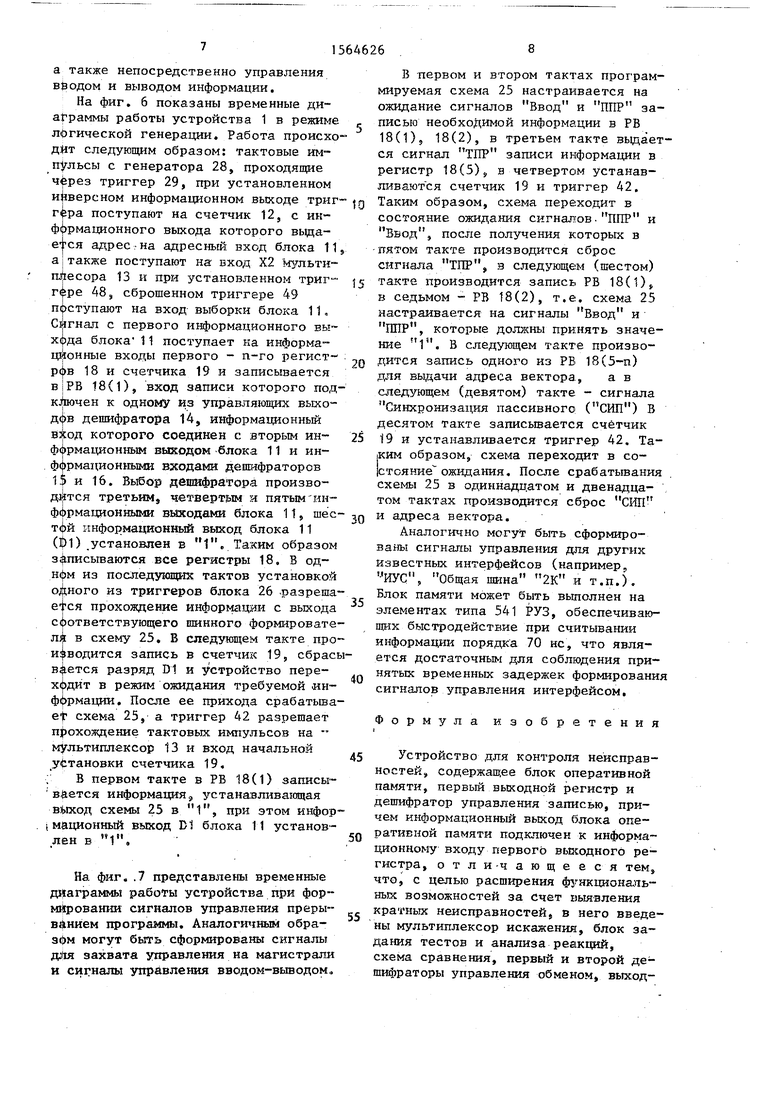

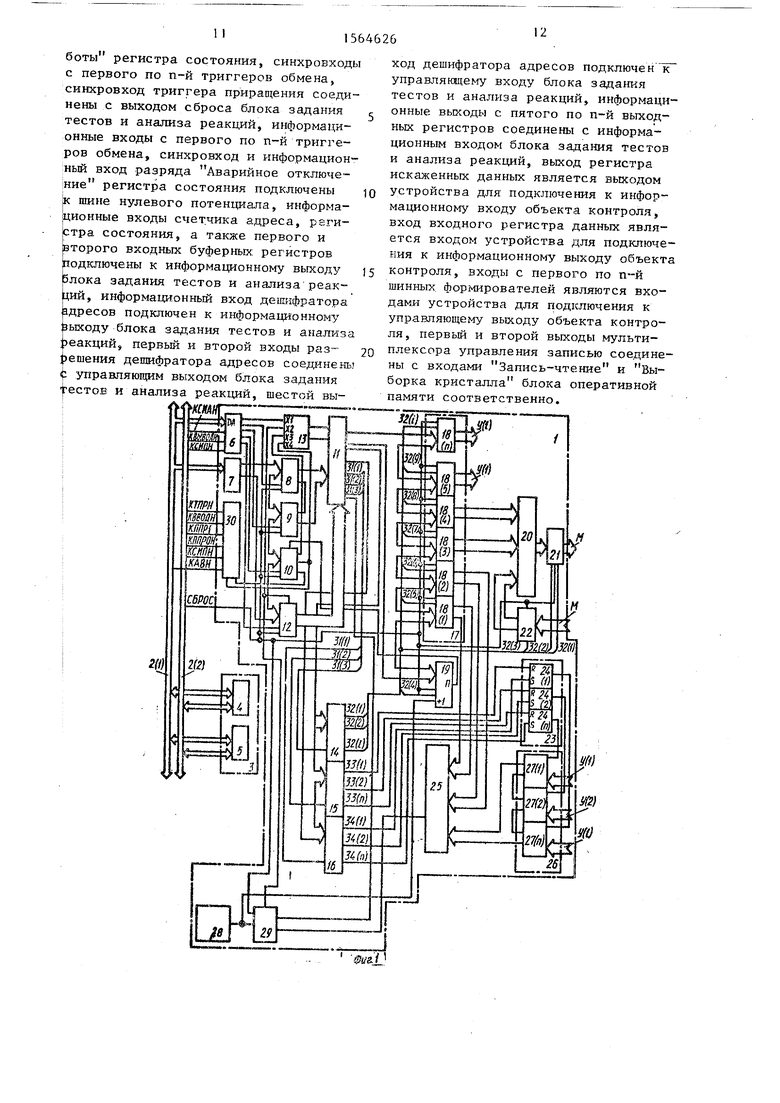

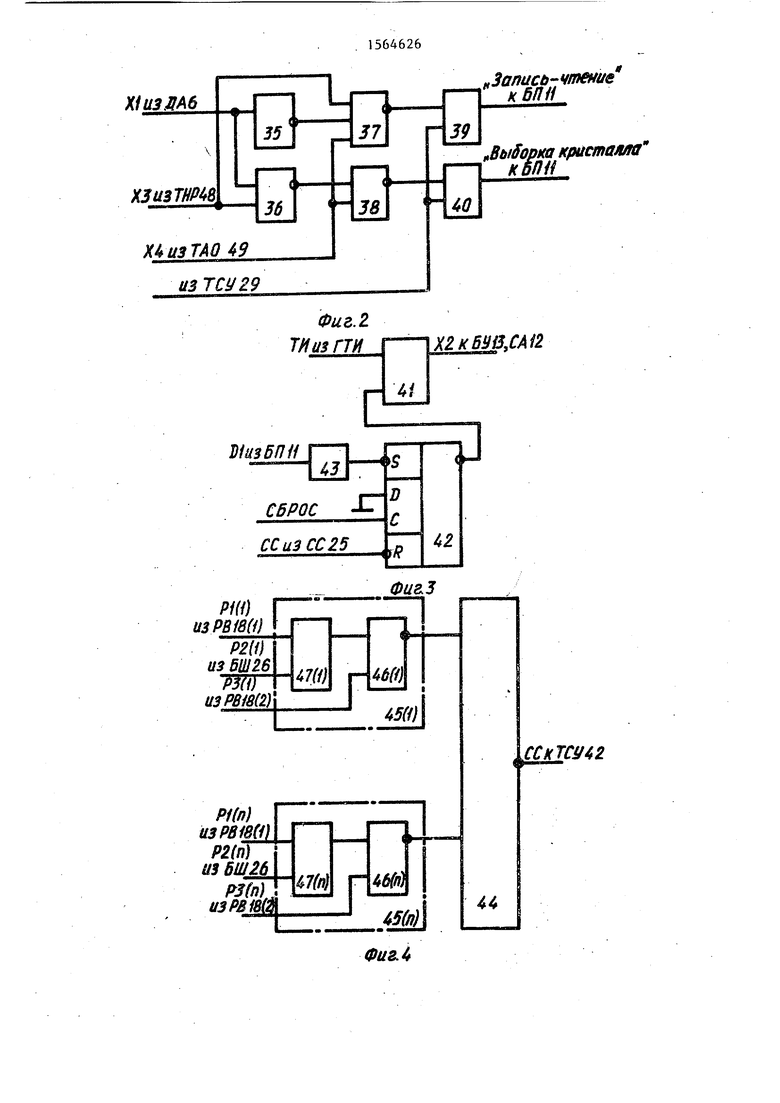

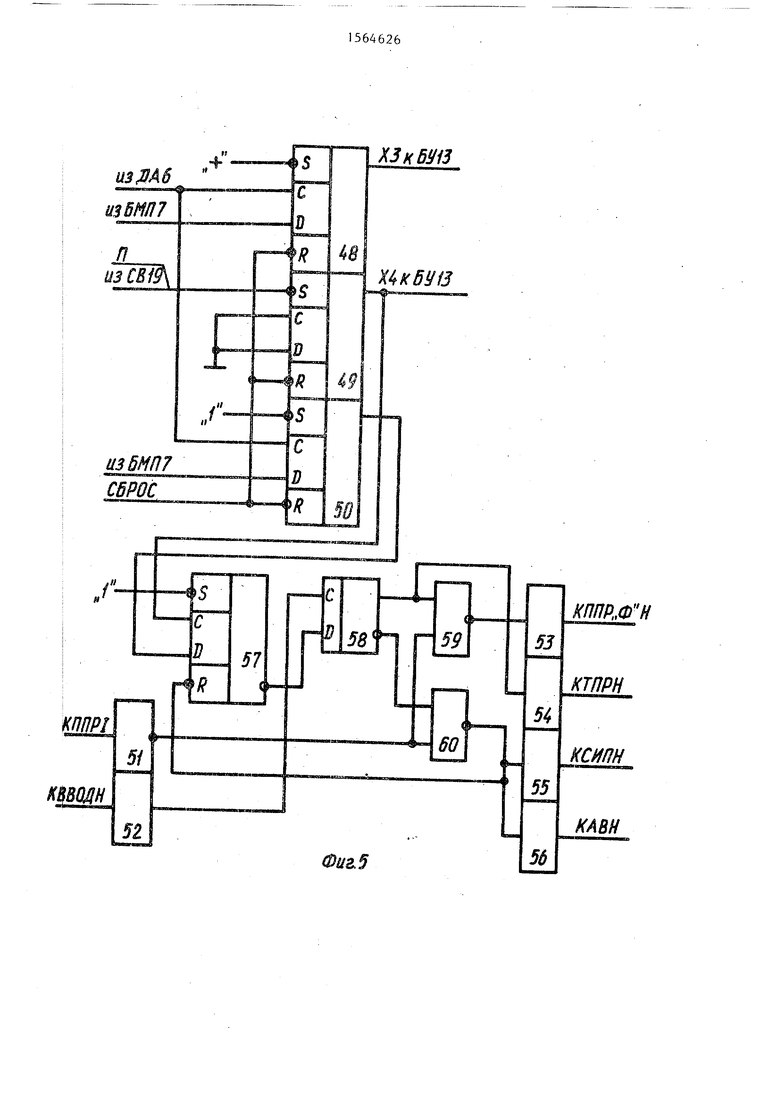

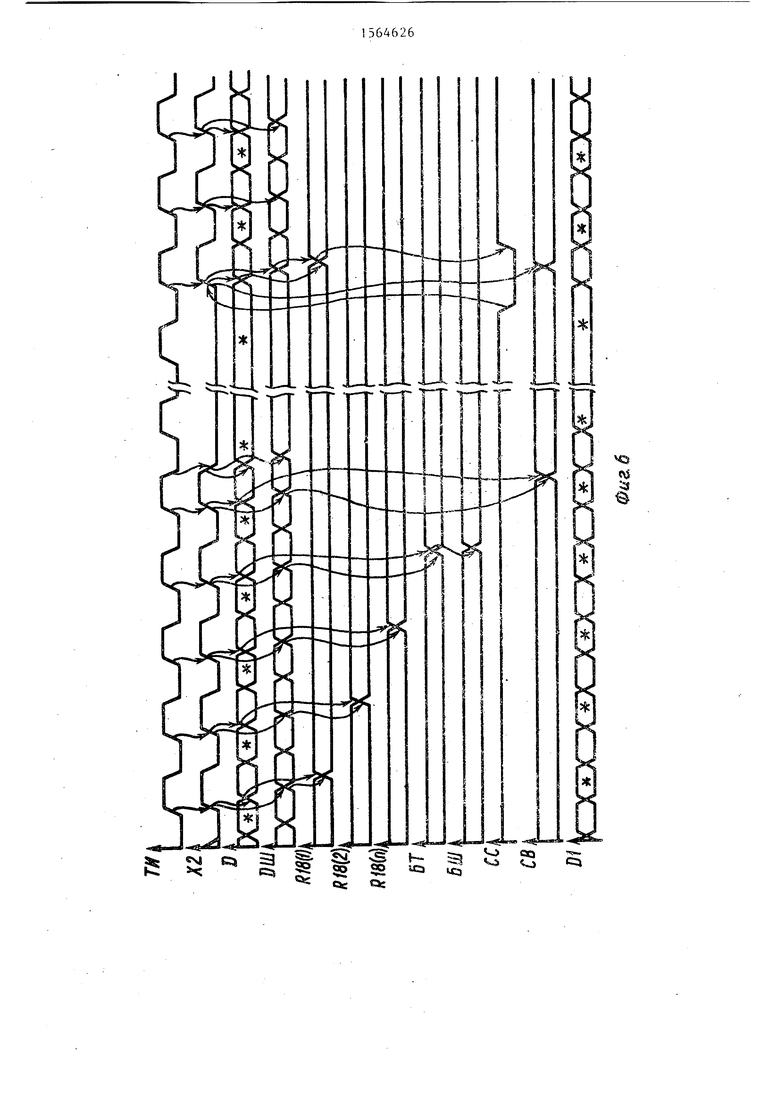

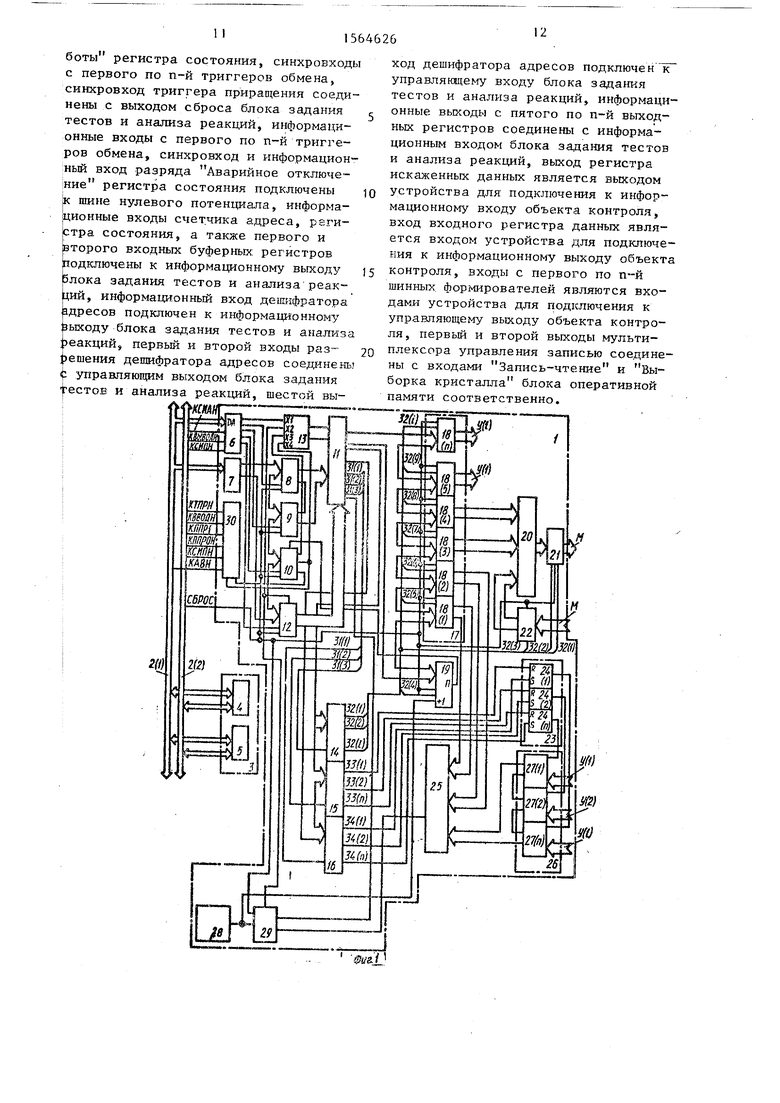

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - схема мультиплексора управления записью, пример исполнения; на фиг.З - схема триггера приращения, пример исполнения; на фиг. 4 - пример реализации схемы сравнения; на фиг. 5 - схема регистра состояния и схемы требования прерывания, пример исполнения; на фиг. 6 и 7 - временные диаграммы работы устройства.

На фиг. 1 представлена структурная схема устройства 1 для контроля неисправностей (УКН), которое подключается к магистрали 2, входящей в состав микроЭВМ 3(например,Электро- ника-60 и т.п.), включающей оперативное запоминающее устройство 4 и центральный процессор 5.

Устройство содержит (фиг,1) дешифратор 6 адресов, блок 7 магистральных приемников, первый и второй входные буферные регистры 8 и 9, регистр 10, состояния, блок 11 оперативной памяти, счетчик 12 адреса, мультиплексор 13 управления записью, дешифратор 14 управления записью,, дра дешифратора 15 и 16 управления обменом, блок 17 из п выходных регистров, включающий регистры (РВ) 18(1 13(п), счетчик 19 времени, мультиплексор 20 искажения, регистр-21 искаженных данных, входной регистр 22 данных, блок 23 из п триггеров об- м|вна, включающий триггеры 24(1)24(п с|кему 25 сравнения, блок 26 из п шинных формирователей, содержащий шинные формирователи (,ШФ) 27(1)- 2(п), генератор 28 тактовых импуль- сЬв, триггер 29 приращения и схему 30 требования прерывания.

Информационные выходы 31(1)-31(3) б|пока 11 подключены к входам разре- ифния дешифраторов 14-16 соответст™ в|знно. Выходы 32(1)-32(i) дешифрато- р|а 14 соединены с входами управления записью регистров 21 и 22, счетчика 19 и регистров 18. Выходы 33(1)- 33(п) дешифратора 15 и выходы 34(1}- 3ft(п) дешифратора 16 соединены с вкодами сброса и установки триггеров бдока 23. ЭВМ 3, блок 7 и схема 30 образуют в совокупности блок задания тестов и анализа реакций устройства.

Мультиплексор 13 управления записью содержит (фиг.2) элементы Hf: 35, 2ИЛИ-НЕ 36, 2ИЛИ-НЕ 37, 2НПИ-НЕ 38, 2И 39 и 40.

Блок 13 может быть выполнен в виде программируемой логической матрицы «

На фиг. 3 приведена конкретная реализация схемы триггера 29 состоя щей из элемента 2И 41, триггера 42 и элемента 43 задержки.

На фиг. 4 приведена конкретная реализация схемы 25, состоящей из п-входового элемента 44 , блоков 45(1)-45(п) логики, включающих элементы 2И-НЕ 46(1)-46-(п) и двух- входовые сумматоры 47(1)-47(п) по модулю. Схема 25 может быть реализована на программируемой логической матрице,

Согласно схеме на фиг. 5 регистр 10 состоит из триггера 48 Начало работы, триггера 49 Аварийное от

0

5

5

ключение и триггера 50 Разрешение прерывания, а схема 30 включает магистральные приемники 51 и 52, магистральные передатчики 53-56, триггер 57 прерывания, триггер 58 схемь требования прерывания и элементы 2И-НЕ 59 и 60.

Блок 7 предназначен для подключения к магистрали 2 ЭВМ. Регистры 9 необходимы для записи в блок 1 информации разрядностью большей, чем позволяет магистраль 2.

Регистр 10 содержит следующие разряды: 1 - разрешение работы, 2 - аварийное отключение, 3 - разрешение прерывания.

Блок 11 служит для записи k-раз- рядных слов, причем k п + то + 4. Мультиплексор 20 предназначен для внесения искажений в информационные разряды слова, фиксируемого в регистре 22s тип вносимого искажения кодируется двумя разрядами для каждого разряда информационного слова, при этом различаются искажения: 00 - нет искажения, 01 - константа О, 10 - константа 1, 11 - инверсия, искаженное информационное слово фиксируется в регистре 21, функция, выполняемая мультиплексором 20, описывается таблицей, где R1„ R2 - разряды РВ 18(3) и 18(4) соответственно, I - разряд информационного слова регистра 22р R3 - искаженный разряд информационного слова.

Слова, записанные в блоке 11, имеют следующую структуру: п разрядов предназначены для записи в один из РВ 18(1)-18(п) или счетчик 19 (в соответствии с управляющими сигналами от дешифратора 14), m разрядов управляют через дешифратор 14 записью соответствующего регистра 17 или счетчика 19 или подключетшем на передачу информации одного кз п формирователей 27, составляющих блок 26, через блок 23, где для каждого ШФ 27(1)-27(п) имеется соответствующий триггер. Выбор соответствующего дешифратора 14, 15 или 16 производится одной из трех шин 31(1)-31(2), снимаемых с блока 11. Один разряд является управляющим сигналом для триггера 29 и поступает через элемент 43 на S-вход триггера 42.

Схема 25 выполняет функцию сравнения поступающей из блока 26 информации с информацией, записанной в РВ 18(1) и 18(2). В РВ 18(2) записана информация о разрядах, которые будут анализироваться в схеме 25, а в РВ 18(1) записана информация об уровне (О или 1) анализируемого разряда. Разряды РВ 18(2), установленные в 1, указывают на анализ соответствующих разрядов информационного слова, поступающего с одного из ШФ 27(1)-27(п). Первый - п-й разряды РВ 18(1) и первый - n-й разряды информационного слова одного из 27(1)-27(п) соединены с первыми и вторыми входами блоков 45(1)- 45(п) соответственно, которые являются первыми и вторыми входами элементов 47(1)-47(п)„ Первый - п-й разряды РВ 18(2) подключены к третьи входам блоков 45(1)46(п), к первым входам которых подключены выходы элементов 47(1)-47(п)„ Выходы элементов блоков 45(1)-45(п) соединены с элементом 44.

Работа схемы 25 может быть описана выражением СС (Р1(1) © Р2(1)).Л А РЗ(1)А ... А(Р1(п) © Р2(п)л ЛРЗ(п), где Р1(1)-Р1(п) - первый - п-й разряды РВ 18(1), Р2(1)-Р2(п) - первый - п-й разряды информационного слова одного из ШФ 27(1)-27(п); Р3(1)-Р3(п) - первый - п-й разряды регистра 18(2) СС - выход схемы 25.

Устройство предназначено для имитации неисправностей, формирования управляющих воздействий и анализа ответных сигналов, с помощью которого осуществляется введение в ВС различных типов отказов и сбоев. Введение неисправностей осуществляется с помощью и на магистрали (типа Общая шина, ИУС и т.п.) путем доступа к элементам системы в режиме внепроцессорной связи. Формирование сигналов управления интерфейсом осуществляется устройством в режиме логической генерации, т.е. генерации управляющих воздействий при совпадении определенных условий. В этом ре0

5

0

5

жиме осуществляется захват управления на интерфейсе, после чего происходит ввод информации в устройство, ее искажение с помощью блоков 20-22 и запись по различным адресам,

В режиме логической генерации блок 11 работает с быстродействием в 2- 3 раза больше, чем осуществляется прием и выдача управляющих сигналов магистрали.

Возможно применение устройства для магистрали с тремя состояниями, с открытым коллектором и открытым эмиттером.

Работа устройства заключается в формировании сигналов неисправностей непосредственно на интерфейсе, а также путем эмуляции различных режимов работы магистрали: захват управления на интерфейсе, операции адресации, ввсца к вывода информации, выработка ложных прерываний и потеря настоящих и т,п. Каждому из режимов имитации неисправностей соответствует микропрограмма, записываемая в блоке 1 I . Возможно применение устройства в любом интерфейсе, при этом изменяются только микропрограммы блока 11 и количество используемых выходных регистров. Устройство вставляется в штатный разъем BCS его входы и выходы подключаются к всем информационным, адресным и управляющим шинам магистрали. Возможно также , подключение выходных регистров и входных шинных формирователей к шинам (точкам) ВС, которых нет в интерфейсе (внутренние сигналы модулей, процессора и т.д.). Информационный выход регистра 21 и информационный вход регистра 22 подключаются к информационным шинам магистрали. Выходы РВ Ш(5)-18(п) соединяются с управляющим шинами, шинами выработки прерываний, адресными и т.п. в зависимости от типа применяемого интерфейса. Регистры 21 и 22 со схемой 20 используются для организации режима Ввод искажения/вывод. Таким образом, обеспечивается внесение заданных типов искажений в заданное число разрядов.

Программируемая схема 25 служит для синхронизации вводимых неисправностей с отдельными событиями на магистрали и для выполнения определенных логических условий, необходимых для захвата управления на магистрали,

0

5

0

5

0

а также непосредственно управления вйодом и выводом информации.

На фиг. 6 показаны временные ди а раммы работы устройства 1 в режиме логической генерации. Работа происходит следующим образом: тактовые импульсы с генератора 28, проходящие через триггер 29, при установленном инверсном информационном выходе триггера поступают на счетчик 12, с информационного выхода которого выдаемся адрес на адресный вход блока 115 а также поступают на вход Х2 мульти- плесора 13 и при установленном триг- 48, сброшенном триггере 49 поступают на вход выборки блока 11. Сигнал с первого информационного выхода блока 11 поступает на информационные входы первого - n-го регист- рфв 18 и счетчика 19 и записывается в РВ 18(1), вход записи которого подключен к одному из управляющих выхо- дфв дешифратора 14, информационный вход которого соединен с вторым информационным выходом блока 11 и информационными входами дешифраторов 1$ и 16. Выбор дешифратора произво- дЖтся третьим, четвертым ч пятым информационными выходами блока 11, шестой информационный выход блока 11 (Й1) установлен в 1. Таким образом записываются все регистры 18, В од- нфм из последующих тактов установкой одного из триггеров блока 26 разрешаемся прохождение информации с выхода соответствующего шинного формирователя в схему 25. В следующем такте про- изводится запись в счетчик 19, сбрасы- веется разряд D1 и устройство пере- в режим ожидания требуемой информации. После ее прихода срабатыва- et схема 25, а триггер 42 разрешает прохождение тактовых импульсов на мультиплексор 13 и вход начальной установки счетчика 19.

В первом такте в РВ 18(1) записывается информация9 устанавливающая В) схемы 25 в 1, при этом инфор i мационный выход В1 блока 11 установлен в

И В

с

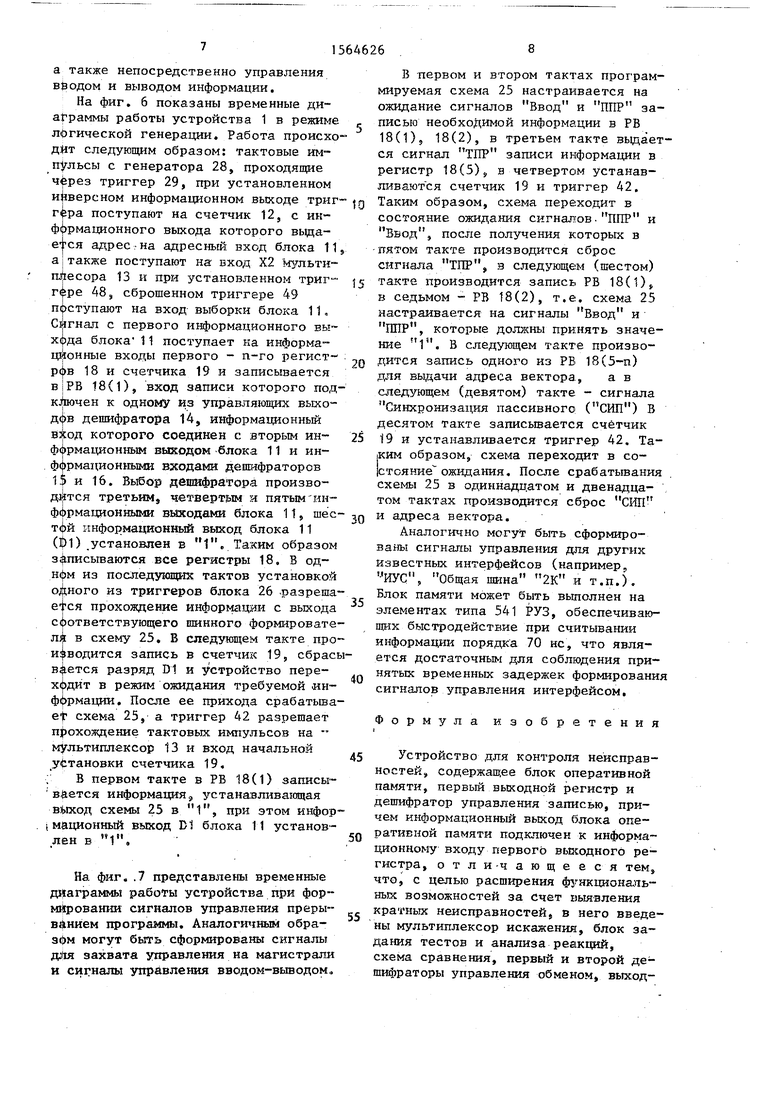

На фиг. .7 представлены временные диаграммы работы устройства при формировании сигналов управления прерыванием программы. Аналогичным обра- 90м могут быть сформированы сигналы для захвата управления на магистрали и сигналы управления вводом-выводом,

0

5

0

5

0

5

0

5

В первом и втором тактах программируемая схема 25 настраивается на ожидание сигналов Ввод и ПНР записью необходимой информации в РВ 18(1), 18(2), в третьем такте выдается сигнал ТПР записи информации в регистр 18(5)„ в четвертом устанавливаются счетчик 19 и триггер 42. Таким образом, схема переходит в состояние ожидания сигналов ППР и Ввод, после получения которых в пятом такте производится сброс сигнала ТПР, в следующем (шестом) такте производится запись РВ 18(1), в седьмом - РВ 18(2), т.е. схема 25 настраивается на сигналы Ввод и ППР, которые должны принять значение 1. В следующем такте производится запись одного из РВ 18(5-п) для выдачи адреса вектора, а в следующем (девятом) такте - сигнала Синхронизация пассивного (СИП) В десятом такте записывается счетчик 19 и устанавливается триггер 42. Та- |ким образом, схема переходит в со- jc т сяние ожидания. После срабатывания схемы 25 в одиннадцатом и двенадцатом тактах производится сброс СИП и адреса вектора.

Аналогично могут быть сформированы сигналы управления для других известных интерфейсов (например, ИУС, Общая шина 2К и т.п.). Блок памяти может быть выполнен на элементах типа 541 РУЗ, обеспечивающих быстродействие при считывании информации порядка 70 не, что является достаточным для соблюдения принятых временных задержек формирования сигналов управления интерфейсом.

Формула изобретения

Устройство для контроля неисправностей, содержащее блок оперативной памяти, первый выходной регистр и дешифратор управления записью, причем информационный выход блока оперативной памяти подключен к информационному входу первого выходного регистра, отличающееся тем, что, с целью расширения функциональных возможностей за счет выявления кратных неисправностей, в него введены мультиплексор искажения, блок задания тестов и анализа реакций, схема сравнения, первый и второй дешифраторы управления обменом, выходные регистры с второго по n-й, ре гистр состояния, дешифратор адресов, п шинных формирователей, п триггеров обмена, первый и второй входные буферные регистры, счетчик адреса, счетчик времени, мультиплексор управления записью, входной регистр данных, регистр искаженных данных, триггер приращения и генератор тактовых импульсов, причем первый информационный выход блока оперативной памяти соединен с информационными входами с второго по п-й выходных регистров и счетчика времени, второй информационный выход блока оперативной памяти подключен к информационным входам дешифратора управления записью, первого и второго дешифраторов управления обменом, третий, четвертый и пятый информационные выходы блока оперативной памяти соединены с входами разрешения соответственно дешифратора управления записью, первого и второго дешифраторов управления обменом, шестой информационный выход блока оперативной памяти подключен к установочному входу триггера приращения, вход сброса которого соединен с выходом схемы сравнения, первый информационный вход которой подключен к информационному выходу первого выходного регистра, второй информационный вход схемы сравнения соединен с информационным выходом второго выходного регистра, третий информационный вход схемы сравнения подключен к информационным выходам с первого по n-й шинных формирователей, входы управления которых соединены с информационными выходами с первого по n-й триггеров обмена, входы сброса которых соединены соответственно с первого по n-й выходами первого дешифратора управления обменом, установочные входы с первого по n-й триггеров обмена соединены с перв ого по n-й выходами второго дешифратора управления обменом, информационные, выходы третьего и четвертого выходных регистров соединены соответственно с первым и вторым информационными входами мультиплексора искажения, управляющий вход которогЬ подключен к информационному выходу входного регистра данных, выход мультиплексора искажения соединен с информационным входом регистра искаженных данных, информационные входы

0

5

0

5

0

5

0

5

0

5

разрядов Разрешение прерывания, Начало работы регистра состояния подключены к информационному входу блока задания тестов и анализа реакций, синхровход регистра состояния соединен с первым выходом дешифратора адресов, второй и третий выходы которого соединены с входами управления записью первого и второго входных буферных регистров соответственно, четвертый и пятый выходы дешифратора адресов подключены к первому информационному входу мультиплексора управления записью и входу управления записью счетчика адреса соответственно, счетный вход которого соединен с выходом триггера приращения и вторым информационным входом мультиплексора управления записью, первый управляющий вход которого соединен с выходом разряда Начало работы регистра состояния, второй управляющий вход мультиплексора управления записью соединен с выходом разряда Аварийное отключение регистра состояния, выходы разрядов Аварийное отключение и Требование прерывания регистра состояния подключены к входу прерывания блока задания тестов и анализа реакций, информационные выходы первого и второго буферных регистров соединены с информационными входами блока оперативной памяти, адресный вход которого подключен к информационному выходу счетчика адреса, входы управления записью с первого но n-й выходных регистров, счетчика времени, первый и второй входы управления записью регистра искаженных данных и вход управления

записью входного регистра данных подключены к выходам с первого по 1-й дешифратора управления записью (где i п + 4), выход переполнения счетчика времени соединен с входом разряда Аварийное отключение регистра состояния, счетный вход счетчика времени соединен с выходом генератора тактовых импульсов и разрешающим входом триггера приращения, входы начальной установки счетчика адреса, счетчика времени, первого и второго входных буферных регистров, с первого по n-й выходы регистров, регистра входных данных, регистра искаженных данных, установочные входы разрядов Аварийное отключение, Разрешение прерывания, Начало работы регистра состояния, синхровходы с первого по n-й триггеров обмена, синхровход триггера приращения соединены с выходом сброса блока задания тестов и анализа реакций, информационные входы с первого по n-й триггеров обмена, синхровход и информационный вход разряда Аварийное отключение регистра состояния подключены к шине нулевого потенциала, информационные входы счетчика адреса, регистра состояния, а также первого и второго входных буферных регистров подключены к информационному выходу 5лока задания тестов и анализа реакций, информационный вход дешифратора адресов подключен к информационному :зыходу блока задания тестов и анализа реакций, первый и второй входы разрешения дешифратора адресов соединены 9 управляющим выходом блока задания рестов и анализа реакций, шестой выход дешифратора адресов подключен к управлявшему входу блока задания тестов и анализа реакций, информационные выходы с пятого по n-й выходных регистров соединены с информационным входом блока задания тестов и анализа реакций, выход регистра искаженных данных является выходом

устройства для подключения к информационному входу объекта контроля, вход входного регистра данных является входом устройства для подключения к информационному выходу объекта

5 контроля, входы с первого по п-й шинных формирователей являются входами устройства для подключения к управляющему выходу объекта контра- выходы мульти- записью соединены с входами Запись-чтение и Выборка кристалла блока оперативной памяти соответственно.

ля, первый и второй Q плексора управления

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля неисправностей | 1991 |

|

SU1798787A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1992 |

|

RU2032938C1 |

| Устройство для сопряжения двух вычислительных машин | 1987 |

|

SU1474665A1 |

| Устройство для сопряжения ЦВМ с абонентами | 1986 |

|

SU1403070A1 |

| Устройство отладки микропрограммных блоков | 1988 |

|

SU1541617A1 |

| Устройство управления процессора | 1988 |

|

SU1670686A1 |

Изобретение относится к вычислительной технике и может быть использовано при экспериментальном исследовании надежности структурно-избыточных вычислительных систем. Целью изобретения является расширение функциональных возможностей устройства за счет выявления кратных неисправностей. С этой целью в устройство, содержащее блок оперативной памяти, первый выходной регистр, дешифратор управления записью, введены мультиплексор искажения, блок задания тестов и анализа реакций, схема сравнения, первый и второй дешифраторы управления обменом, со второго по N-й выходные регистры, регистр состояния, дешифратор адресов, N шинных формирователей, N триггеров, первый и второй входные буферные регистры, счетчик адреса, мультиплексор управления записью, входной регистр данных, регистр искаженных данных, триггер приращения и генератор тактовых импульсов. 7 ил.

X1U3.JA6

35

X3U3THP4B.

36

UU3TAO 49

из Т СУ 29

Фиг.2. ТИизГТИ IЩкбУ&СА 12

„Запись-чтение хбПН

37

39

tBbiffopKo кристалла КВПН

38

40

ФиаЗ

s

С

С V

57

и ff

WEI

51

Фи&5

КППР„Ф Н

58

59

53

KWPH

54

60

ксипи

КАВИ

56

(VS S

| Устройство для имитации неисправностей ЭВМ | 1984 |

|

SU1177816A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отладки тестов | 1979 |

|

SU860076A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-15—Публикация

1987-04-20—Подача