выходных шин 16-1 ... 1б-п аналоговых гармонических сигналов.

Преобразователь работает следующим образом.

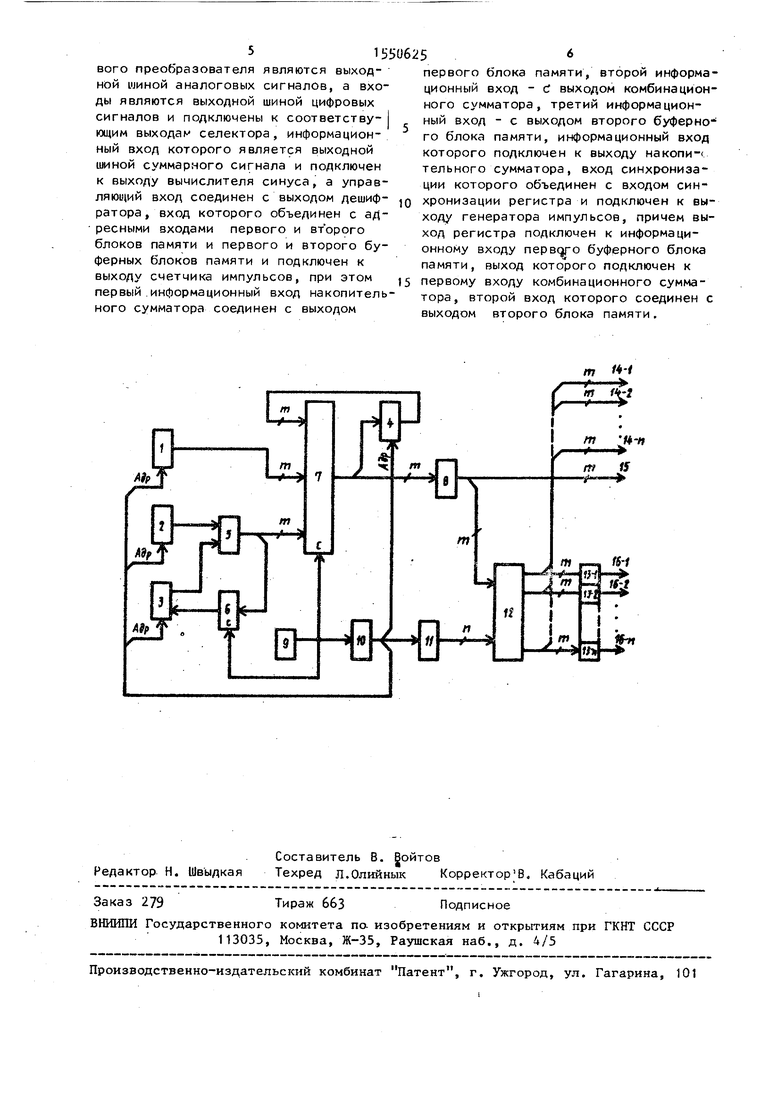

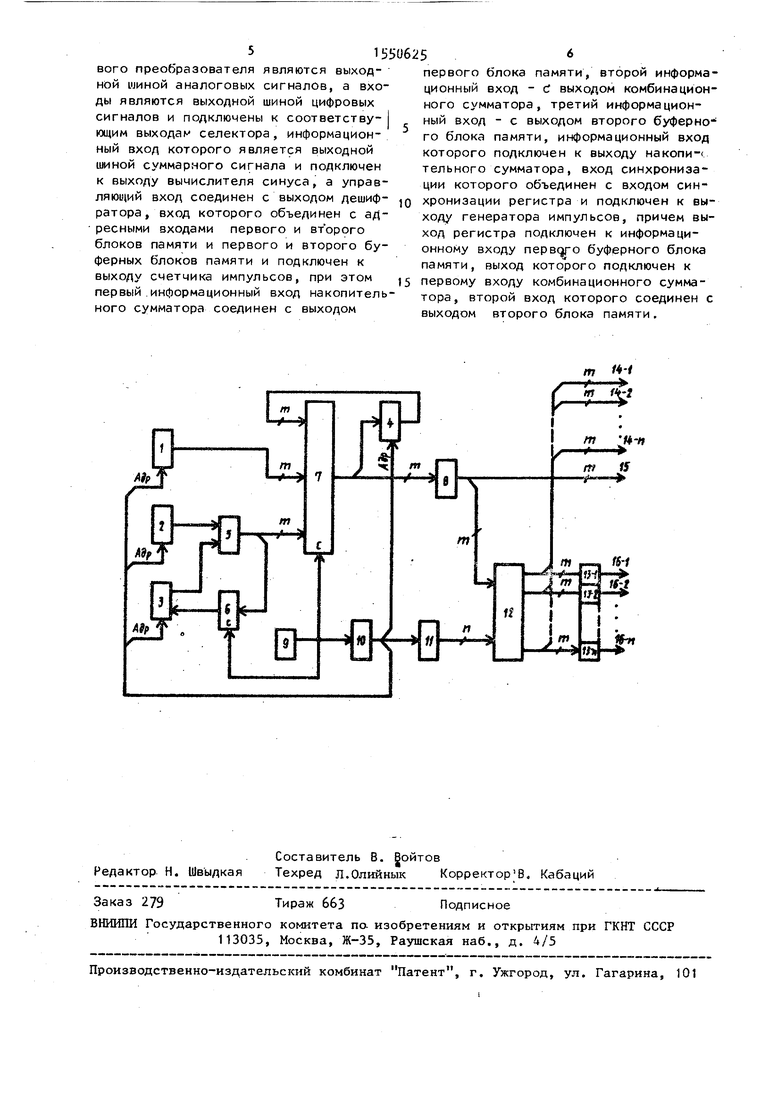

В блок 1 памяти предварительно записываются п произвольных т-разрядны значений приращений фазы, определяющих величины постоянных частот формируемых выходных гармонических сигналов. В блок 2 памяти предварительно записываются п произвольных т-разрядных значений приращений фазы, преобразуемых в процессе работы с помощью комбинационного сумматора 5 регистра 6 и первого буферного блока 3 памяти в значения, определяющие изменения частот формируемых выходных гармонических сигналов. Тактовые импульцифровой сигнал, включающий в себя информацию off n автономных гармонических сигналах, два смежных значения каждого в котором разделены интервалом в (п-1) тактов генератора 9. Разделение суммарного выходного сигнала по отдельным каналам осуществляется с помощью селектора 12, на

информационный вход которого с выхода вычислителя 8 синуса поступает суммарный сигнал. Управление селектором 12 осуществляется сигналами, поступающими на его управляющие вхоr ды с п выходов дешифратора 11, на вход которого поступают сигналы с разрядных выходов счетчика 10. На каждом из п выходов селектора 12 формируются m-разрядные цифровые зна

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ГЕНЕРАТОР ДЛЯ ЦИФРОВЫХ СЛЕДЯЩИХ СИСТЕМ КОРРЕЛЯЦИОННОЙ ОБРАБОТКИ СИГНАЛОВ | 2000 |

|

RU2180125C1 |

| Цифровой синтезатор сигналов | 1988 |

|

SU1626314A1 |

| ПРИЕМНИК СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2000 |

|

RU2178894C1 |

| Цифровой генератор синусоидальных сигналов | 1984 |

|

SU1223328A1 |

| Преобразователь код-частота гармонического сигнала | 1984 |

|

SU1195449A2 |

| Цифровой фазовый модулятор | 1983 |

|

SU1184081A1 |

| Цифровой функциональный генератор | 1985 |

|

SU1285452A1 |

| Устройство для отображения информации на экране цветного телевизионного индикатора | 1986 |

|

SU1387038A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1525916A1 |

| Обратимый преобразователь координат | 1982 |

|

SU1035617A1 |

Изобретение относится к вычислительной технике и предназначено для использования в качестве программно-перестраиваемого генератора гармонических сигналов. Цель изобретения - расширение области применения за счет формирования N параллельных гармонических сигналов переменной частоты в цифровой и аналоговой формах. Работа преобразователя основана на последовательном вычислении цифровых значений N автономных приращений фаз в накопительном сумматоре путем суммирования их предыдущих значений с приращениями, поступающими из блока памяти и с выхода комбинационного сумматора. С помощью совокупности комбинационного сумматора, регистра и буферного блока памяти в преобразователе формируется приращение фазы, позволяющее формировать выходной гармонический сигнал переменной частоты. В вычислителе синуса последовательные значения суммируемых фаз преобразуются в соответствующие значения амплитуд, изменяющиеся по закону синуса, причем два смежных значения каждого из N формируемых гармонических сигналов разделены интервалом в /N-1/ тактов генератора импульсов. Селектор разделяет суммарный цифровой гармонический сигнал по N каналам. Информация с N выходов селектора поспупает на выходы N цифро-аналоговых преобразователей, формирующих соответствующие гармонические сигналы в аналоговой форме и передающих их на выходы преобразователя. 1 ил.

25

сы с выхода генератора 9 поступают нэ2о чения гармонического сигнала с частотой, зависящей от значений соответствующих фазовых приращений, записанных в блоках 1 и 2 памяти. Информация с выходов селектора 12 поступает на выходные шины И цифровых гармонических сигналов и на входы п циф- роаналоговых преобразователей 13, формирующих соответствующие гармонические сигналы в аналоговой форме и передающих их на соответствующие выходные шины 16 преобразователя.

Применяя блоки 1 и 2 памяти с раздельными схемами записи и считывания, можно изменять начальные условия Формирования гармонических сигналов, не прерывая процесс их генерации .

синхровходы регистра 6 и накопительного сумматора 7 а также на счетный вход счетчика 10, на разрядных выходах которого формируются значения ад- 1ресов считывания информации из блоков 1 и 2 памяти и буферных блоков 3 и памяти. С выхода блока 1 памяти п значений каждого приращения фазы последовательно поступают на первый вход накопительного сумматора 7, с выхода блока 2 памяти значения приращения фазы аналогично поступают на первый вход комбинационного сумматора 5, с выхода которого информация поступает на второй вход накопительного сумматора 7 и в регистр 6, с выхода (которого она поступает в первый буферный блок 3 памяти, откуда информация, записанная в предыдущем такте, передается на второй вход комбинационного сумматора 5, суммируясь с начальным значением приращения . Информация с выхода накопительного сумматора 7 поступает во второй буферный блок k памяти, откуда значение накопления фазы, записанное в предыдущем такте, поступает на третий вход накопительного сумматора 7. Кроме того, информация о накопленном изменении фазы с вывода накопительного сумматора 7 поступает на вход вычислителя 8 синуса, выполненного в виде постоянного запоминающего устройства с предварительно записанным в нем значениями амплитуды, изменяющимися по закону синуса в зависимости от значения приращения фазы, поданного на его адресные входы. С выхода вычислителя 8 синуса на выходную шину 15 поступает суммарный

30

35

40

45

Формула изобретения

Преобразователь код - частота гармонического сигнала, содержащий регистр, информационный вход которого подключен к выходу комбинационного сумматора, вычислитель синуса, вход которого подключен к выходу накопительного сумматора, цифроаналоговый преобразователь, генератор импульсов, выход которого соединен с входом счетчика импульсов, отличающийся тем, что, с целью расширения области применения за счет формирования п параллельных гармонических сигналов переменной частоты в цифровой и аналоговой формах, в него , введены первый и второй блоки памяти, первый и второй буферные блоки памяти , дешифратор, селектор и () цифроа налоговых преобразователей, выходы которых и выход первого цифроаналого50

Формула изобретения

Преобразователь код - частота гармонического сигнала, содержащий регистр, информационный вход которого подключен к выходу комбинационного сумматора, вычислитель синуса, вход которого подключен к выходу накопительного сумматора, цифроаналоговый преобразователь, генератор импульсов, выход которого соединен с входом счетчика импульсов, отличающийся тем, что, с целью расширения области применения за счет формирования п параллельных гармонических сигналов переменной частоты в цифровой и аналоговой формах, в него введены первый и второй блоки памяти, первый и второй буферные блоки памяти , дешифратор, селектор и () цифроа налоговых преобразователей, выходы которых и выход первого цифроаналого

вого преобразователя являются выходной шиной аналоговых сигналов, а входы являются выходной шиной цифровых сигналов и подключены к соответствующим выходам селектора, информационный вход которого является выходной шиной суммарного сигнала и подключен к выходу вычислителя синуса, а управляющий вход соединен с выходом дешифратора, вход которого объединен с адресными входами первого и второго блоков памяти и первого и второго буферных блоков памяти и подключен к выходу счетчика импульсов, при этом первый информационный вход накопительного сумматора соединен с выходом

первого блока памяти, второй информационный вход - с выходом комбинационного сумматора, третий информационный вход - с выходом второго буферно го блока памяти, информационный вход которого подключен к выходу накопи- тельного сумматора, вход синхронизации которого объединен с входом синхронизации регистра и подключен к выходу генератора импульсов, причем выход регистра подключен к информационному входу первого буферного блока памяти, выход которого подключен к

5 первому входу комбинационного сумматора, второй вход которого соединен с выходом второго блока памяти .

Авторы

Даты

1990-03-15—Публикация

1988-05-19—Подача