Изобретение относится к цифровой вычислительной технике и может использоваться для целей контроля аппаратуры обработки информации.

Цель изобретения - расширение функциональных возможностей цифрового функционального генератора за счет обеспечения изменения частот членов гармонического ряда, представляющего генерируемый сигнал.

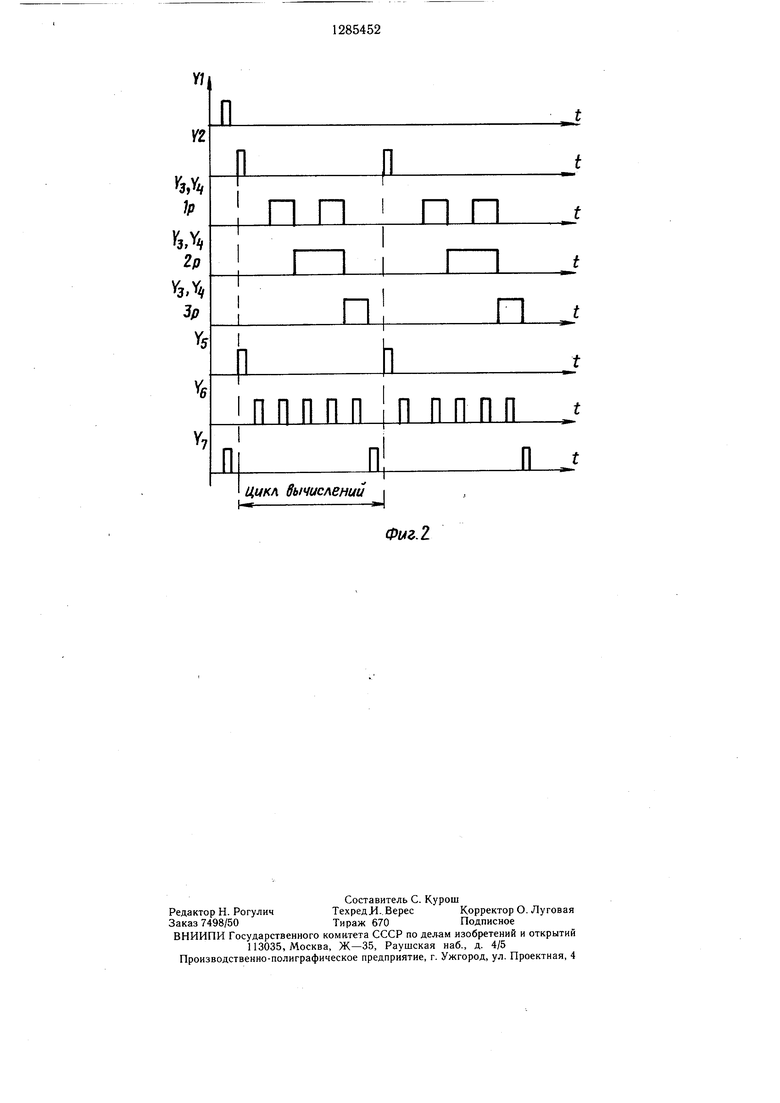

Цифровой функциональный генератор содержит Л сумматоров 1, N регистров 2, коммутатор 3, блок 4 памяти синусов, умножитель 5, накапливающий сумматор 6, блок 7 памяти весовых коэффициентов, регистр 8 буферный, блок 9 синхронизации.

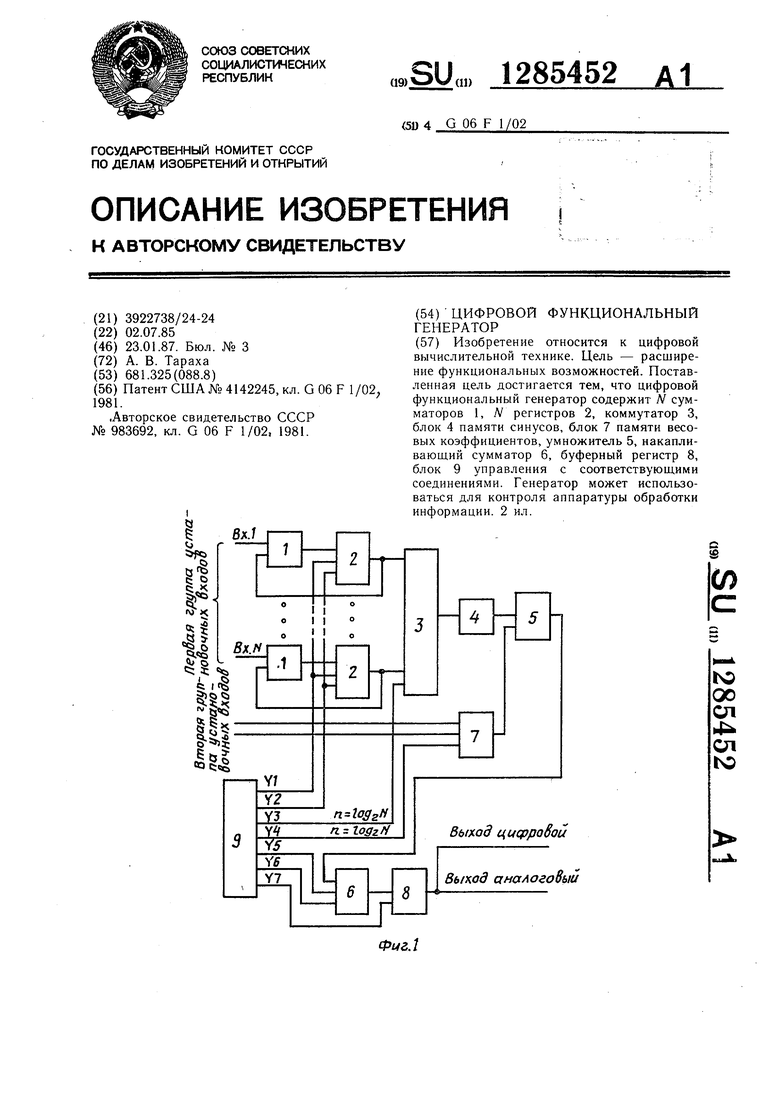

На фиг. 1 представлена функциональная схема предлагаемого генератора; на фиг. 2- временная диаграмма устройства управления для .

Своими выходами блок 9 синхронизации

соединен с входами установки нуля регист- 20 тельности операций к выходу коммутатора 3

ров 2 памяти, с входами синхронизации этих же регистров, с управляющими входами коммутатора 3, адресными входами блока 7 памяти весовых коэффициентов, с установочным входом накапливающего сумматора бис входами синхронизации накапливающего сумматора 6 и буферного регистра 8.

Принцип действия устройства основан на том, что любой сложный сигнал ограниченной длительности и с ограниченным спектром можно приближенно представить в виде конечного тригонометрического полинома

U(iM} Uo+ Dismti)fL-&.t,(1)

где j 1, 2, 3, ..., 1;

у 1, 2, ..., Л - номер гармоники; со/ - частота /-и гармоники; Dj - амплитуда /-и гармоники; А/ - интервал дискретизации сигнала по времени.

Как следует из выражения (1), для синтеза такого сигнала достаточно задать jV значений амплитуд гармоник, их частоты to/ и интервал дискретизации АЛ

Устройство работает следующим образом.

Перед началом работы на входах первой группы устанавливаются коды A.XI, ..., А.:, в блок 7 памяти весовых коэффициентов, переведенный при помощи управляющего входа в режим записи, вводятся значения DJ, регистры 2 памяти обнуляются импульсом, поступающим из блока 9 синхронизации.

После начала первого цикла вычислений блок 9 устанавливает накапливающий сумматор 6 в исходное состояние, при этом на его выходе фиксируется код хо- По окончании этого процесса в схеме генератора устанавливаются следующие коды: на выходах регистров 2 памяти - нули во всех разрядах, на адресном входе блоки 7 памяти весовых коэффициентов - нули во всех разрядах, на его выходе - код коэффициента

25

30

подключается его второй вход и изменяется на единицу код на адресном входе блока 7 памяти весовых коэффициентов, вследствие чего на его выходе появляется код амплитуды D2- Вся последовательность операций повторяется, после чего на выходе накапливающего сумматора 6 фиксируется код

Хо + DisinAAJi -)- D2SinAA:2.

Перечисленные операции повторяются N раз, после чего на выходе накапливающего сумматора 6 появляется код

Хо + SD/sinAx/.

(2)

Первый цикл вычислений закончится за- 5г писью по сигналу от блока 9 синхронизации кода, определяемого выражением (2) в буферный регистр 8. Одновременно с записью в буферный регистр 8 к выходу коммутатора 3 подключается его первый вход, на адресный вход блока 7 памяти весовых коэф- 40 фициентов подаются нули во всех разрядах, а на входы синхронизации регистров 2 памяти - импульсы, в результате чего на выходах регистров появляются коды 2Axi, 2Ал:2 и т. д. до 2AA iv. Начинается второй цикл вычислений, по окончании которого на выходе буферного регистра 8 фиксируется код

л Хо + .SD/sin2A;c/.

В результате повторения циклов вычис- CQ ления на выходе буферного регистра 8 последовательно сменяются коды

к Хо + .2 /sin3Ax/;

J 1

N

Хо + SD,-sin4Ax,- и т. д. }-i

45

55

Иными словами на цифровом выходе генератора формируется последовательность кодов

DI, на управляющем входе коммутатора 3 - нули во всех разрядах. При этом к выходу коммутатора 3 подключен его первый вход. На выходе первого сумматора 1 присутствует код Axi на выходе второго сумматора 1 - код Ах2 и т. д.

Импульсом с второго выхода блока 9 код Дх записывается в первый регистр 2, код Ax2 - во второй регистр 2 и т. д. Теперь на выходе коммутатора 3 присутствует код Х, на выходе блока 4 памяти синусов - код sinAxi, на выходе умножителя 5 - код DisinAxi, который поступает на вход накапливающего сумматора 6. В накапливающем сумматоре 6 вырабатывается сумма хо + -J- Dism&.xi, которая фиксируется в нем импульсом, поступающим на его вход синхронизации из блока 9 и появляется после этого на его выходе.

После выполнения указанной последова

подключается его второй вход и изменяется на единицу код на адресном входе блока 7 памяти весовых коэффициентов, вследствие чего на его выходе появляется код амплитуды D2- Вся последовательность операций повторяется, после чего на выходе накапливающего сумматора 6 фиксируется код

Хо + DisinAAJi -)- D2SinAA:2.

Перечисленные операции повторяются N раз, после чего на выходе накапливающего сумматора 6 появляется код

Хо + SD/sinAx/.

(2)

Первый цикл вычислений закончится за- г писью по сигналу от блока 9 синхронизации кода, определяемого выражением (2) в буферный регистр 8. Одновременно с записью в буферный регистр 8 к выходу коммутатора 3 подключается его первый вход, на адресный вход блока 7 памяти весовых коэф- 0 фициентов подаются нули во всех разрядах, а на входы синхронизации регистров 2 памяти - импульсы, в результате чего на выходах регистров появляются коды 2Axi, 2Ал:2 и т. д. до 2AA iv. Начинается второй цикл вычислений, по окончании которого на выходе буферного регистра 8 фиксируется код

л Хо + .SD/sin2A;c/.

В результате повторения циклов вычис- Q ления на выходе буферного регистра 8 последовательно сменяются коды

к Хо + .2 /sin3Ax/;

J 1

N

Хо + SD,-sin4Ax,- и т. д. }-i

5

5

Иными словами на цифровом выходе генератора формируется последовательность кодов

хо .I:DiSm(i&.Xj),

где/ 1, 2, 3, ..., 1 - номер цикла вычислений.

Частота смены этих кодов и соответствующих им напряжений равна частоте повторения циклов вычисления.

Периодам гармонии 51п(гАл;/) соответствует 2 значений аргументов Х, где k - разрядность кодов аргументов при условии, что разрядности всех Л кодов равны. Таким образом, период каждой /-и гармоники определяется выражением

(2-1)Д/ Axj

(3)

где А/ - период повторения циклов вычислений;

десятичный эквивалент кода Ах,-.

Частота каждой /-и гармоники определяется выражением

А.)С;

Т; ()А/

20 циональных возможностей за счет обеспечения изменения частот членов гармонического ряда, представляющего генерируемую функцию, в него введены jV сумматоров, N регистров, умножитель, блок памяти весовых коэффициентов, причем первые инПериод повторения циклов вычисления, а он является для гармоник интервалом дискретизации, ограничен по минимуму сум- 25 форГационныГвходы всех сумматоров марным временем задержки всех узлов схемы. Он может быть выбран, исходя из данного числа гармоник и их частот, и заложен в блок 9 синхронизации. Практически период дискретизации гармоник определяется, исходя из теоремы Котельникова

д , мин(7у)

А (5)

При выбранном периоде дискретизации задают, исходя из требуемых частот гармоник, коды приращения аргументов Axi,

..., А.Х от единицы младшего разряда до значения

подключены к группе входов приращения аргумента генератора, группа входов загрузки амплитуд гармоник которого подключена к группе информационных входов блока

3Q памяти весовых коэффициентов, адресный вход которого подключен к первому выходу блока синхронизации, выход /-го сумматора (/ 1-/V) подключен к информационному входу /-ГО регистра, выход которого подключен к f-му информационному входу комму35 татора и второму информационному входу одноименного сумматора, входы сброса регистров подключены к второму выходу блока синхронизации, третий, четвертый и пятый выходы синхроимпульсов которого подключены к входам синхронизации регистров, накапливающего сумматора и буферного регистра соответственно, вход начальной установки накапливающего сумматора подключен к шестому выходу блока синхронизации, седьмой выход которого подключен к управляющему входу коммутатора, выход блока памяти синусов подключен к первому информационному входу умножителя, второй информационный вход которого подключен к выходу блока памяти весовых коэффициентов, выход умножителя подключен

Ах/макс

(2-1)А

/ ;мнн

Как следует из приведенных рассужде- НИИ, на выходе буферного регистра 8 формируется последовательность кодов, определяемая выр,ажением

5(/ А/) xo+ lDiS,m(2nfiiM),

где fj определяется выражением (4).

Выражение (7) адекватно выражению (1).

Таким образом, на выходе буферного регистра 8 генерируется в виде последовательности кодов заданный сложный сигнал с ограниченными спектром и длительностью.

Для изменения гармонического состава генерируемой функции (сложного сигнала) достаточно изменить значения кодов Ajci, ..., Ax|/. Для изменения амплитуд D/ гармоник необходимо перевести блок 7 памяти весовых коэффициентов в режим записи и ввести в него новые значения амплитуд (весовых коэффициентов).

10

Формула изобретения

Цифровой функциональный генератор, содержащий коммутатор, блок памяти синусов, блок синхронизации, накапливающий

J5 сумматор и буферный регистр, причем выход коммутатора подключен к адресному входу блока памяти синусов, выход накапливающего сумматора подключен к информационному входу буферного регистра, отличающийся тем, что, с целью расщирения функ20 циональных возможностей за счет обеспечения изменения частот членов гармонического ряда, представляющего генерируемую функцию, в него введены jV сумматоров, N регистров, умножитель, блок памяти весовых коэффициентов, причем первые ин25 форГационныГвходы всех сумматоров 25 форГационныГвходы всех сумматоров

подключены к группе входов приращения аргумента генератора, группа входов загрузки амплитуд гармоник которого подключена к группе информационных входов блока

3Q памяти весовых коэффициентов, адресный вход которого подключен к первому выходу блока синхронизации, выход /-го сумматора (/ 1-/V) подключен к информационному входу /-ГО регистра, выход которого подключен к f-му информационному входу комму35 татора и второму информационному входу одноименного сумматора, входы сброса регистров подключены к второму выходу блока синхронизации, третий, четвертый и пятый выходы синхроимпульсов которого подключены к входам синхронизации регистров, накапливающего сумматора и буферного регистра соответственно, вход начальной установки накапливающего сумматора подключен к шестому выходу блока синхронизации, седьмой выход которого подключен к управляющему входу коммутатора, выход блока памяти синусов подключен к первому информационному входу умножителя, второй информационный вход которого подключен к выходу блока памяти весовых коэффициентов, выход умножителя подключен

50 к информационному входу накапливающего сумматора, выход буферного регистра является выходом генератора.

45

Фмг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1278886A1 |

| Генератор случайного процесса (его варианты) | 1983 |

|

SU1125624A1 |

| Генератор случайного процесса | 1985 |

|

SU1739374A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Генератор случайного процесса | 1982 |

|

SU1068936A1 |

| Устройство для реализации быстрого преобразования Фурье | 1989 |

|

SU1672469A1 |

| Устройство для вычисления функций | 1987 |

|

SU1472901A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для цифровой фильтрации | 1988 |

|

SU1596347A1 |

Изобретение относится к цифровой вычислительной технике. Цель - расширение функциональных возможностей. Поставленная цель достигается тем, что цифровой функциональный генератор содержит N сумматоров 1, Л регистров 2, коммутатор 3, блок 4 памяти синусов, блок 7 намяти весовых коэффициентов, умножитель 5, накапливающий сумматор 6, буферный регистр 8, блок 9 управления с соответствующими соединениями. Генератор может использоваться для контроля аппаратуры обработки информации. 2 ил. (Л to СХ) сд 4 сл ю Вымд цисрробой Вымд аналоговый

| Патент США № 4142245, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор сигналов сложной формы | 1980 |

|

SU983692A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-23—Публикация

1985-07-02—Подача