сп ел ю

со

О5

со

Изобретение относится к импульсной технике и может быть использовано для согласования работы п однотипных устройств, например, для синхронизации п процессоров.

Четь изобретения - повышение надежности с одновременным повышением быстродействия за счет асинхронного Формирования взаимоисключающих последовательностей импульсов.

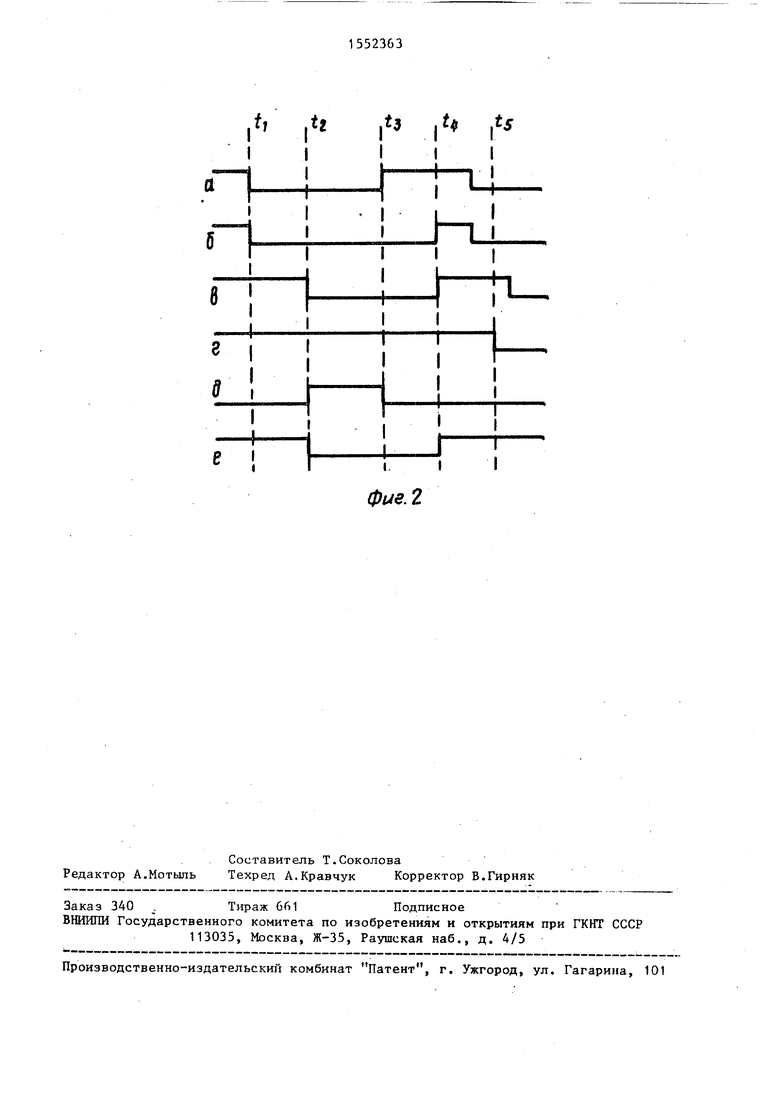

На фиг. 1 приведена электрическая функциональная схема устройства; на фиг. 2 - временные диаграммы, пояе- нпющие его работу.

Формирователь сигналов управления содержит два идентичных канала 1 и 2, каждый из которых содержит соответственно D-триггер 3.1, 3.2, элемент И 4.1, 4.2, элемент 11ЛИ-НЕ 5.1, 5.2, выход которого соединен с С-входом D-триггера 3.1, 3.2, входы - с соответствующими входными шинами 6.1-б.п, 7.1-7.П и с соответствующими входами элемента И 4.1, 4.2, дополнительный вход -- с прямым выходом D-триггера 3.1, 3.2 другого канала, D-вход D-триггсра 3.1, 3.2 соединен с шиной 8 блокировки, R-вход-с выходом элемента И 4.1, 4.2, инверсный выход - с выходной иинои 9.1, 9.2.

Формирователь сигналов управления „работает следующим образом.

В исходном состоянии ка все входы устройства по шинам 6.1-б.п, 7.1-У.п поступают сигналы с уровнем логической епиницы. При этом триггеры 3.1 и 3.2 сброшены, а на шинах 9.1 и 9.2 установлен уровень логической единицы. Пусть в момент времени t на одном до из входов канала 1 появляется сигнал с уровнем логического нуля (фиг. 2а). При этом уровень логического нуля устанавливается на входе элемента

уровнем логической единицы. По переднему Фронту этого сигнала ipurrep 3.1 взводится, на его инверсном выходе (Фиг. 2е) Лорнируется передний Фронт отрицательного впхо тного импульса, а сигнал с уровнем логической единицы с прямого выхода поступает на дополнительный вход элемента 5.2

IQ другого канала, заппещая срабатывание триггера 3.2 до гех пор, пока не 6vnei сброшен триггер 3.1.

Пусть в момент времени t« на одном из входов канала 1 устлиявлинарт15 ся уровень логической единицы. При этом сигнал логической единицы снимается с входа синхронизации триггера 3.1, однако его состояние при этом не меняется. Триггер 3.1 сбрасывает2Q ся в момент времени Ц, когда уровень логической единицы устанавливается на всех входах канала 1. При этом устройство приходит в исходное состояние, а на шине 9.1 Формируется задний фронг выходного импуаьса (Фиг. 2е). второй канал работает аналогично.

При наличии сигнала блокировки с уровнем логического нуля на входах канала 1 появляется сигнал с уровнем логического нуля Ј Фиг. а). При ом уровень логического нуля устанавливается на входе элемента 4.1, тем самым снимается сигнал логической единицы с входа сброса триггера 3.1 (фиг. 2б).

35 После того, как все сигналы, поступающие в этот канал по шинам 6.1- б.п, принимают значение логического i нуля, т.е. уровень логического НУЛЯ

устанавливается на последнем из п входов ( фиг. 2б) при условии, что триггер 3.2 второго канала сброшен и на его прямом входе присутствует уровень логического нуля, а на шине 8

25

30

4.1, тем самым снимается сигнал логи- 45 иг. 2г) установлен сигнал с уровнем

о

уровнем логической единицы. По переднему Фронту этого сигнала ipurrep 3.1 взводится, на его инверсном выходе (Фиг. 2е) Лорнируется передний Фронт отрицательного впхо тного импульса, а сигнал с уровнем логической единицы с прямого выхода поступает на дополнительный вход элемента 5.2

Q другого канала, заппещая срабатывание триггера 3.2 до гех пор, пока не 6vnei сброшен триггер 3.1.

Пусть в момент времени t« на одном из входов канала 1 устлиявлинарт5 ся уровень логической единицы. При этом сигнал логической единицы снимается с входа синхронизации триггера 3.1, однако его состояние при этом не меняется. Триггер 3.1 сбрасываетQ ся в момент времени Ц, когда уровень логической единицы устанавливается на всех входах канала 1. При этом устройство приходит в исходное состояние, а на шине 9.1 Формируется задний фронг выходного импуаьса (Фиг. 2е). второй канал работает аналогично.

При наличии сигнала блокировки с уровнем логического нуля на входах канала 1 появляется сигнал с уровнем логического нуля Ј Фиг. а). При ом уровень логического нуля устанавливается на входе элемента 4.1, тем самым снимается сигнал логической единицы с входа сброса триггера 3.1 (фиг. 2б).

5 После того, как все сигналы, поступающие в этот канал по шинам 6.1- б.п, принимают значение логического i нуля, т.е. уровень логического НУЛЯ

устанавливается на последнем из п входов ( фиг. 2б) при условии, что триггер 3.2 второго канала сброшен и на его прямом входе присутствует уровень логического нуля, а на шине 8

5

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотный дискриминатор | 1987 |

|

SU1448404A1 |

| Счетное устройство с исправлением сбоев | 1986 |

|

SU1422402A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1348815A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1983 |

|

SU1181140A1 |

| Счетчик импульсов | 1985 |

|

SU1261112A1 |

| Устройство для LU-разложения матриц | 1987 |

|

SU1509933A1 |

| Устройство приоритетного доступа к магистрали | 1990 |

|

SU1839249A1 |

| Измеритель длительности одиночных радиоимпульсов | 1985 |

|

SU1273844A1 |

| ПЕРЕСЧЕТНОЕ УСТРОЙСТВО С КОНТРОЛЕМ | 2003 |

|

RU2264031C2 |

| Многоканальный анализатор логических состояний | 1985 |

|

SU1298896A1 |

Изобретение относится к импульсной технике и может быть использовано для согласования работы N однофазных устройств, например для синхронизации N процессоров. Цель изобретения - повышение надежности с одновременным повышением быстродействия путем асинхронного формирования взаимоисключающих последовательностей импульссов - достигается введением в каждый канал элементов И 4.1, 4.2, соответственно, элементов ИЛИ-НЕ 5.1, 5.2 соответственно, шины 8 блокировки и (N - 1) входных шин 6.1...6N и 7.2...7N соответственно. В устройстве также имеются два идентичных канала 1 и 2, каждый из которых содержит D-триггер 3.1 и 3.2 соответственно, входные шины 6.1 и 7.1 соответственно и выходную шину 9.1. 2 ил.

ческой единицы с входа сброса триггера 3.1 ( Фиг. 26). После того, как все сигналы, поступающие в этот канал по шинам 6.1-б.п, принимают значение логического нуля, т.е. уровень логического нуля устанавливается на последнем из п входов (фиг. 2G) при условии, что триггер 3.2 второго канала сброшен и на его прямом входе появляется уровень логического нуля, а ка шине 8 ( Фиг. 2г) установлен сигнал с уровнем логической единицы, в момент времени tt на выходе элемента 4.1 ( Фиг. 2д) Формируется сигнал с

0

5

логическон единицы, в момент времени t на выходе элемента 4.1 (Фиг. 2д) формируется сигнал с уровнем логической единицы. По переднему Фронту этого сигнала триггер 3.1 выводится, на его инверсном выходе ( Фиг. 2е) Формируется передний Фронт отрииател FO- го выходного импульса, а сигнал с уровнем логической единицы t прямого выхода поступает на дополнительный вход элемента 5.2 другого канада, запрещая срабатывание триггера 3.2 до гех пор, пока не будет сброшен триггер 3.1.

Ц на одном

Пусть Р момент времени из входов канала 1 устанардцнлется уровень логическое единицы. При этом сигнал логической единицы снимается с входа синхронизации триггера 3.1, однако его состояние при этом не меняется. Триггер 3.1 сбрасывается в момент времени t, когда уровень логической единицы устанавливается на всех входах канала 1. При этом устройство приходит D исходное состояние, а на шине 9.1 формируется задний Лронт выходного импульса. ( бит. 2е). Второй канал работает аналогично.

При наличии сигнала блокировки с уровнем логического нуля (после момента времени tg) триггеры 3.1 и 3.2 не взводятся и выходные импульсные последовательности не Лормиругэт- ся даже при наличии сигналов с уровнем логического нуля на всех входах одного из каналов.

Таким образом, каждый канал Функционирует в соответствии с характеристическим уравнением

К xmiVXmzV... V

V(XW(vXmV...

«K-IJ ук-1Xrm Xmi i Хтм

где Y

- сигнал на выходе дан- о ного канала на данном такте;

(

Л

D

КY

k-

сигналы на входах канала на данном гакте; сигнал на входе блокировки на предыдущем такте;

сигнал на выходе другого канала на преды- дущем такте; сигнал на выходе данного канала на предыдущем такте. ол тактом в дайном случае поиик-1

мается интервал времени t

К-И

в течение которого входные сигналы ик1

Х(. . .Х остаются неизменным.

Формула изобретения

Формирователь сигналов управления, содержащий два идентичных канала, каждый из которых содержит D-триггер, инверсный выход которого соединен с выходной шиной, входную пину, о гл и ч а ю щ и и с я тем, что, с

целью повышения надежности с одновременным повышением быстродействия, в каждый канал введены элемент И и элемент ИЛИ-НЕ, шина блокировки и п-1

входные шины, которые соединены с соответствующими входами элемента И и с соответствующим входом элемента ИЛИ-НЕ, дополнительный вход которого соединен с прямым выходом D-триггера

другого канала, выход - с С-входом D-триггера, R-вход которого соединен с выходом элемента И, D-вход - с шиной блокировки.

фие.2

| Авторское свидетельство СССР | |||

| Устройство для синхронизации импульсных последовательностей | 1979 |

|

SU864521A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для синхронизации случайныхиМпульСОВ | 1979 |

|

SU839027A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-03-23—Публикация

1988-01-04—Подача