дополнительного элемента И, и с соответствующими входами предыдущих шифраторов, а выход и-го дополнительного элемента И подключен к входу второго счетчика, выходы кото рого являются выходньми шинами по наименьшему основанию, выходы t1-2

1181140

шифраторов подключены к соответствующим входам соответствующих сумматоров по модулям других оснований системы остаточных классов, выходы Которых являются выходными шинами по соответствующим основаниям.

| название | год | авторы | номер документа |

|---|---|---|---|

| Модулярный измерительный преобразователь | 2016 |

|

RU2619831C1 |

| Преобразователь напряжения в код системы остаточных классов | 1983 |

|

SU1181139A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1991 |

|

SU1797158A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2010 |

|

RU2433527C1 |

| Преобразователь кода системы остаточных классов в напряжение | 1983 |

|

SU1175034A1 |

| Аналого-цифровой преобразователь в системе остаточных классов | 1986 |

|

SU1372620A1 |

| Обратимый преобразователь двоичных кодов в код системы остаточных классов | 1983 |

|

SU1141398A1 |

| Устройство обработки сигналов электромузыкальных инструментов | 1990 |

|

SU1746400A1 |

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| Преобразователь кода системы остаточных классов в двоичный код | 1983 |

|

SU1133669A1 |

АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ Б КОД СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ, содержащий первый блок вычитания, первый вход которого объединен с первым входом первого компаратора и является входной шиной преобразователя, второй вход подключен к первому выходу первого цифроаналогового преобразователя, второй выход которого подключен к второму входу первого компаратора, а входы - к . соответствующим выходам первого счетчика импульсов, второй счетчик импульсов, выходы которого подключены к соответствующим входам второго ЦАП, выход которого подключен к первому входу второго компаратора, RS-триггер, 5 -вход которого является шиной Запуск, выход подключен к первому входу элемента И, второй .вход которого является шиной тактовых импульсов, первый шифратор, выходы которого подключены к соответствующим входам сумматора по мо дулю наибольшего основания, выходы которого являются выходными шинами преобразователя по наибольшему основанию, отличающийся тем, что, с целью повьш1ения быстродействия, в него введены по числу оснований системы остаточных классов И инверторов, ц-2 шифратора, 11-2 сумматора по модулям других оснований системы остаточньк классов, кроме наименьшего, И дополнительных элементов И, М-2 счетчика импульсов,

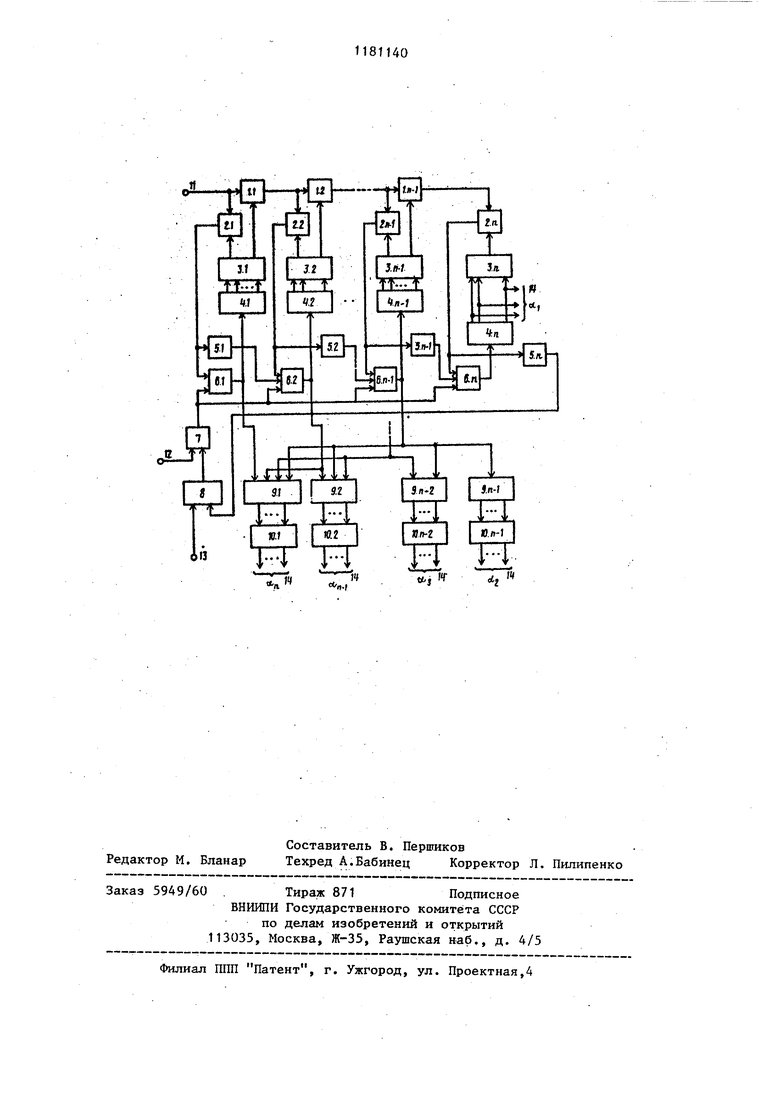

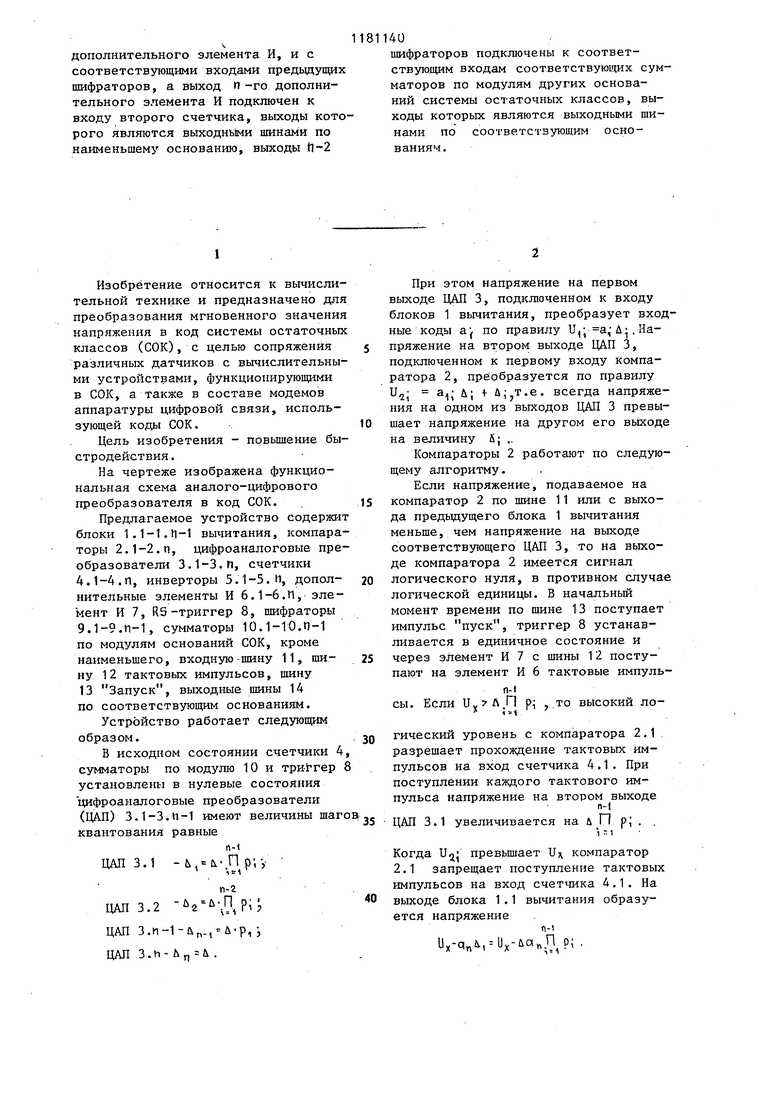

Изобретение относится к вычисли тельной технике и предназначено дл преобразования мгновенного значени напряжения в код системы остаточны классов (сок), с целью сопряжения различных датчиков с вычислительны ми устройствами, фyнкциoниpyюш ми в СОК, а также в составе модемов аппаратуры цифровой связи, использующей коды СОК. Цель изобретения - првьш1ение бы стродействия. На чертеже изображена функциональная схема аналого-цифрового преобразователя в код СОК. Предлагаемое устройство содержи блоки 1.1-1.11-1 вычитания, компара торы 2.1-2. п, цифроаналоговые пре образователи 3.1-З.И, счетчики 4.1-4.л, инверторы 5.1-5.11, дополнительные элементы И 6.1-6.П, элемент И 7, RS-триггер 8, шифраторы 9.1-9.П-1, сумматоры 10.1-10.П-1 по модулям оснований СОК, кроме наименьшего, входную-шину 11, шину 12 тактовых импульсов, шину 13 Запуск, выходные шины 14 по соответствующим основаниям. Устройство работает следующим образом. В исходном состоянии счетчики 4 сумматоры по модулю 10 и три-ггер установлены в нулевые состояния цифроаналоговые преобразователи (ЦАП) 3.1-З.П-1 имеют величины шаг квантования равные ЦАП 3.1 - Ci, И-.П р; V ЦАП 3.2 Р; J ЦАП 3.n-1-u -,-u-p,i ЦАП з.и- n ь . При этом напряжение на первом выходе ЦАП 3, подключенном к входу блоков 1 вычитания, преобразует входные коды а по правилу U,,-й . Напряжение на втором выходе ЦАП 3, подключенном к первому входу компаратора 2, преобразуется по правилу 21 ii i А;,т.е. всегда напряжения на одном из выходов ЦАП 3 превышает напряжение на другом его выходе на величину &j .. Компараторы 2 работают по следующему алгоритму. Если напряжение, подаваемое на компаратор 2 по шине 11 или с выхода предьщущего блока 1 вычитания меньше, чем напряжение на выходе соответствующего ЦАП 3, то на выходе компаратора 2 имеется сигнал логического нуля, в противном случае логической единицы. В начальный момент времени по шине 13 поступает импульс пуск, триггер 8 устанавливается в единичное состояние и через элемент И 7 с шины 12 поступают на элемент И 6 тактовые импульсы. Если и.,Л П Pi , то высокий логический уровень с компаратора 2.1 разрешает прохождение тактовых импульсов на вход счетчика 4.1. При поступлении каждого тактового импульса напряжение на втором выходе ЦАП 3.1 увеличивается на д П р; . Когда U.J превьш1ает U компаратор 2.1 запрещает поступление тактовых импульсов на вход счетчика 4,1. На выходе блока 1.1 вычитания образуется напряжение Чх-Чп х- Л/ 3 За время счета счетчика 4.1 на вход шифратора 9.1 поступает а„ импульсов. При этом каждьй раз на выходе шифратора 9.1 появляется код / 1 П р; Рп . Например, для СОК с i1 основаниями р, 5, рг 7, р 11 поступает код (57)mod . Таким образом, с поступлением каждого импульса на вход шифратора 9.1 содержимое сумматора по моду лю 10.1 увеличивается на величину 1 П р; ) modр.В момент окончания сч 1 / та счетчика 4.1 составляет величину , п-1 пЯ р;ро РпЕсли в исходном состоянии (/X Л П р то выходной сигнал логи1 1ческого нуля с компаратора 2.1 чере инвертор 5.1 разрешает прохождение тактовых импульсов через элемент И 6.2 и запрещает через элемент И 6. Таким образом, а, 0. Во втором цикле преобразования (если U -dnui ug выходе элемента И 6.1 появляется а,., импуль сов. При этом на выходах шифратора 9.1 появляются коды. (Пр; mojp и для приведенного примера (5) mod . А на выходах шифратора 9. ( появляются коды П Р;| fnoj р„.. и i.:l I для примера (5) mod . Следовательно по окончании поступления импульсов с выхода элемента И 6.2 в сумматоре 10.1 оказывается величина/ п-г n-f 1 а„.,-Пр,апЛ р;Uodpn; а в сумма 5Г1 Ч /. I/ 10.2 величина|(с1 п-1.П pipot Рпм Дальнейшая работа устройства продолжается до тех пор, пока на все сумматоры 10.1-10.П-1 через шифраторы 9.1-9.И-г1 поступит а, импульсов с выхода элемента И 6.и При этом сумма напряжений на выходах ЦАП 3.1-З.Ц равна величине йЛ. Нулевой выходной уровень с компаратора 2. VI через инвертор 5. h устанавливает триггер 8 в нулевое состояние. В сумматорах 10.1-10.h-1 оказываются величины остатков уot э ,,,.j(tnj содержимое счетчика A.tt соответствует об,. На этом процесс преобразования напряжения U, в цифровой код А заканчивается и коды остатков v.:, ..,oij,no шинам 14 выводятся из устройства .

oS-Jl

rt.f

| Гитис Э.И | |||

| Преобразователи информации для электронных цифровых вьмислительных устройств | |||

| - М.: Энергия, 1970, с | |||

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1034170A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ч | |||

Авторы

Даты

1985-09-23—Публикация

1983-04-29—Подача