Изобретение относится к цифровой технике и может быть использовано для контроля цифровых устройств.

Цель изобретения - расширение функциональных возможностей, заключающихся в обеспечении контроля цифровых устройств, имеющих три состояния выходных сигналов.

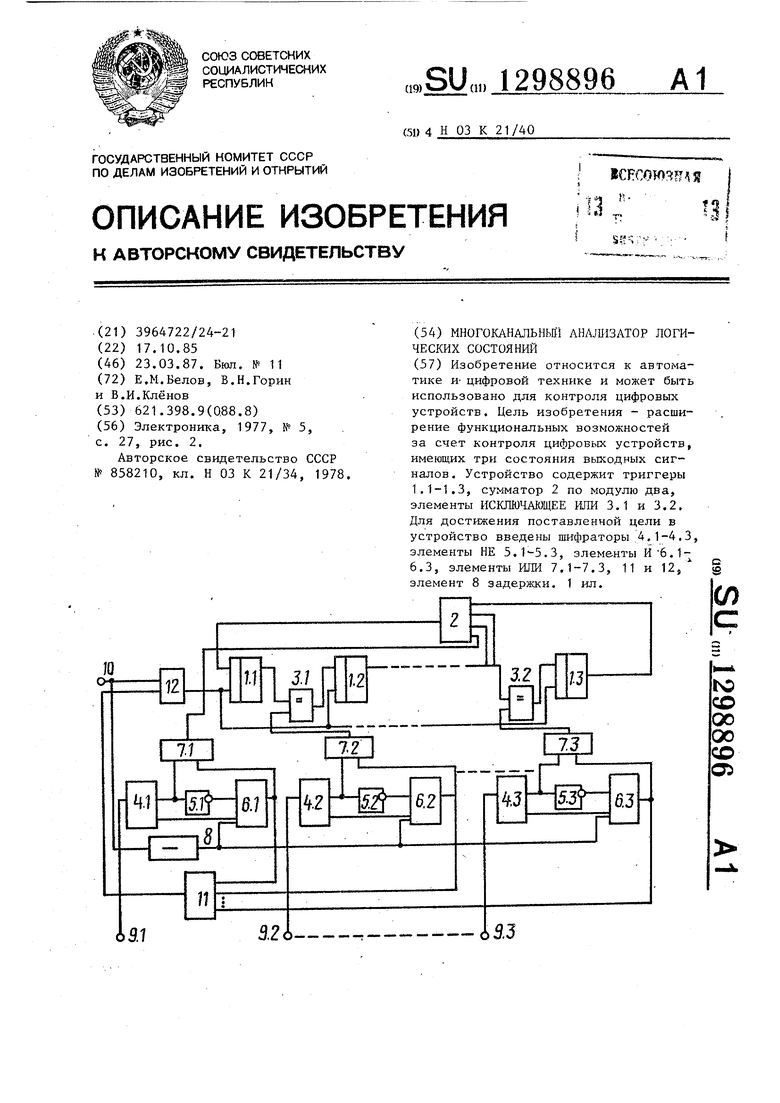

На чертеже приведена структурная схема многоканального анализатора логических состояний.

Анализатор содержит триггеры 1,1- 1,3, сумматор 2 по модулю два, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 3.1 и 3.2, шифраторы 4,1-4,3, элементы НЕ 5,1-5.3, элементы И 6,1-6,3, элементы ИЛИ 7,1- 7,3, элемент 8 задержки, информационные шины 9,.1-9,3, входную.шину 10, элементы ИЛИ 11 и 12,

Информационные входы триггеров 1,1 1.3 соединены соответственно с выходами сумматора 2 по, модулю два и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3,1 и Зо2, первые входы которых соединены соответственно с прямыми выходами тригге ров 1,1 и 1,2, входы сумматора 2 по модулю два соединены с прямыми выхо- дами триггеров 1,2 и 1,3, дополнитель ный вход сумматора 2 по модулю два и вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3,1 и-3,2 соединены соответственно с выходами элементов ИЛИ 7.1-7.,3, информационные шины 9,1-9.3 соединены соответственно с входами шифраторов 4,1-4,3, первые выходы которых соединены соответственно с входами элементов НЕ 5.1-5,3, выходы которых соединены соответственно с первыми входами элементов И 6,1-6,3, выходы которых соединены соответственно с первыми входами элементов ИЛИ 7,1- 7.3, вторые входы которых соединены соответственно с первыми выходами шифраторов 4,1-4,3, вторые выходы которых соединены соответственно с вторыми входами элементов И 6.1-6.3, третьи входы которых соединены с выходом элемента 8 задержки, вход которого соединен с входной шиной 10 и с первым входом элемента ИЛИ 12, выход которого соединен с тактовыми входами триггеров 1.1-1,3, второй вход элемента ИЛИ 12 соединен с выходом элемента ИЛИ 11, входы которого соединены с выходами элементов И 6,1-6.3,

Каждый из шифраторов 4,1-4.3 кодирует информацию, поступающую по

5

0

5

0

5

0

5

0

5

соответствующей информационной шине. 9,1-9.3,

При поступлении, например, по шине 9,1 сигнала логической единицы на первом и втором выходах шифратора присутствует код 11, при поступлении логического нуля - код 00, а при поступлении сигнала Z (где Z - третье состояние сигнала контролируемого бита) - код 01,

Каждый из шифраторов 4.1-4.3 может

быть выполнен, например, на первом и втором компараторах напряжения, первые входы которых соединены с входом шифратора, а вторые - с шинами опорных напряжений, соответствующих сигналам логической единицы и логического нуля. Выходы первого и второго компараторов напряжений соединены соответственно с первым и вторым выходами шифратора.

Многоканальный анализатор логических состояний работает следующим образом.

Очередной код импульсной последовательности с проверяемого цифрового устройства поступает на информационные шины 9.1-9,3 в такт с синхроимпульсами по шине 10, Если, например, на информационную шину 9.2 поступает логическая единица или логический ноль, на выходе элемента ИЛИ 7,2 будет соответственно сигнал логической единицы или логического нуля, при этом элемент И 6,2 закрыт либо по первому, либо по второму входу. На элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 3,1 происходит суммирование по модулю два сигнала с выхода элемента ИЛИ 7,2 и сигнала с выхода триггера 1.1, результат суммирования по модулю два фиксируется триггером 1,2 по приходу: тактового импульса по шине 10,

Б триггере 1,1 фиксируется результат суммирования по модулю два сигналов с выходов триггеров 1,2 и 1,3 ;и с выхода элемента ИЛИ 7,1,

При приходе, например, на шину 9,2 сигнала Z суммирование по модулю два с фиксацией результата в триггере 1,2 происходит дважды: первый раз сигнал логического нуля суммируется по модулю два с сигналом с выхода тригге- ра 1,1 и результат фиксируется в триггере 1.2 по приходу тактового импульса по шине 10. Второй раз суммируется по модулю два сигнал логической единицы с выхода элемента ИЛИ 7,2

и сигнал с выхода триггера 1. 1. Результат фиксируется в триггере 1.2 по прихрду задержанного элементом 8 задержки тактового импульса по шине 10, так как элемент И 6.2 в этом слу- чае оказывается открытым.

По окончании цикла поступления входной информации по шинам 9.1-9.3 на триггерах 1.1-1.3 устанавливается число, которое характеризует содержание, входной информации контролируемого цифрового устройства. Правильность работы контролируемого устройства может быть определена путем сравнения полученного результата с результатом, полученным ранее с заведомо исправного такого же устройства или полученным на ЭВМ.

Число, полученное после поступления контролируемой последовательности и хранящееся на триггерах, может быть вьшедено на индикатор (не показан) .

25

Форм у л а изобретения

Многоканальный анализатор логических состояний, содержащий входную шину ц п разрядов, первый из которых содержит информационную шину, триг- 30 выходом второго элемента ИЛИ, входы

дов, в каждом из которых информацио ный вход триггера соединен с выходом элемента ИСКЛЮЧАМЦЕЕ ШШ, первый вхо которого соединен с прямым выходом триггера предыдущего разряда, тактовый вход триггера первого разряда соединен с тактовыми входами тригге ров остальных разрядов, отличающийся тем, что, с целью расширения функциональньк возможноетей, в него введены два элемента ИЛИ элемент, задержки, а в каждый ра ряд введен элемент НЕ, элемент ИЛИ,--, шифратор и элемент И, выход и первый вход которого соединены соответственно с первым входом элемента ИЛИ и с выходом элемента НЕ, вход которого соединен с вторым входом элемента ШШ и с первым выходом шифратора, вход и второй выход которого со.единены соответственно с информационной шиной и вторым входом элемента И, третий вход которого соединен с выходом элемента задержки, вход которого соединен с входной шиной и первым входом первого элемента ИЛИ, выход и второй вход которого со единены соответственно с тактовым входом триггера первого разряда н с

гер и сумматор по модулю два, каждый из остальных разрядов содержит информационную шину, триггер и элемент ИСКПЮЧА11ХЦЕЕ ИЛИ, в первом разряде информационный вход триггера соединен с выходом сумматора по модулю два, входы которого соединены с прямыми выходами триггеров остальных разряСоставитель В.Ранов Редактор А.Козориз Техред Л,Сердюкова ; Корректор А.Зимокосов

Заказ 897/58 Тираж 902 Подписное ВНИИГШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие,- г.Ужгород, ул. Проектная, 4,

5

0 5

0

5

0 выходом второго элемента ИЛИ, входы

дов, в каждом из которых информационный вход триггера соединен с выходом элемента ИСКЛЮЧАМЦЕЕ ШШ, первый вход которого соединен с прямым выходом триггера предыдущего разряда, тактовый вход триггера первого разряда соединен с тактовыми входами триггеров остальных разрядов, отличающийся тем, что, с целью расширения функциональньк возможное тей, в него введены два элемента ИЛИ, элемент, задержки, а в каждый разряд введен элемент НЕ, элемент ИЛИ,--, шифратор и элемент И, выход и первый вход которого соединены соответственно с первым входом элемента ИЛИ и с выходом элемента НЕ, вход которого соединен с вторым входом элемента ШШ и с первым выходом шифратора, вход и второй выход которого со.единены соответственно с информационной шиной и вторым входом элемента И, третий вход которого соединен с выходом элемента задержки, вход которого соединен с входной шиной и первым входом первого элемента ИЛИ, выход и второй вход которого соединены соответственно с тактовым входом триггера первого разряда н с

которого соединены с выходами элементов И разрядов, в каждом из которых, кроме первого, выход элемента ИЛИ соединен с вторым входом элемента ИС КЛЮЧАЮЩЕЕ ИЛИ, в первом разряде выход элемента ШШ соединен с дополнительным входом сумматора по модулю два.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь информации | 1986 |

|

SU1322476A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Аналого-цифровой преобразователь в системе остаточных классов | 1986 |

|

SU1372620A1 |

| Цифровой измеритель длительности одиночных импульсов | 1986 |

|

SU1318986A1 |

| Обратимый преобразователь двоичных кодов в код системы остаточных классов | 1983 |

|

SU1141398A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для умножения | 1982 |

|

SU1156064A1 |

| Устройство для селекции изображений объектов | 1986 |

|

SU1464183A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

Изобретение относится к автоматике и- цифровой технике и может быть использовано для контроля цифровых устройств. Цель изобретения - расширение функциональных возможностей за счет контроля цифровых устройств, имеющих три состояния выходных сигналов. Устройство содержит триггеры 1.1-1.3, сумматор 2 по модулю два, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 3.1 и 3.2. Для достижения поставленной цели в устройство введены шифраторы 4.1-4.3, элементы НЕ 5.1-5.3, элементы Й 6.1- 6.3, элементы ИЛИ 7.1-7.3, 11 и 12/ элемент 8 задержки. 1 ил. с S (Л ГС со 00 сю со О)

| Электроника, 1977, № 5, с | |||

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многоканальный анализатор логических состояний | 1978 |

|

SU858210A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-03-23—Публикация

1985-10-17—Подача