Изобретение относится к измерительной технике и может быть использовано при создают быстродействующих цифровых фазометров повышенной точности, а также высокоточных преобразователей фаза-код для управляющих цифровых вычислительных систем.

Цель изобретения - увеличение диапазона частот входных сигналов при сохранении точности измерения сдви- на фаз для заданной разрядной сетки.

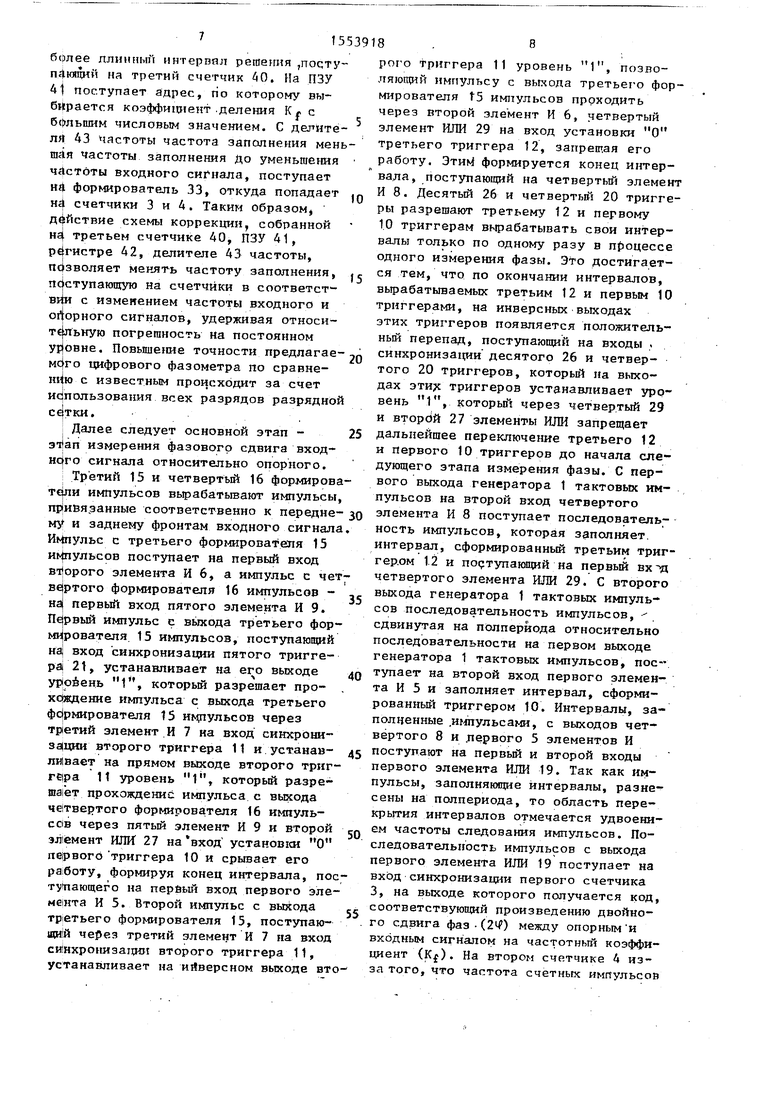

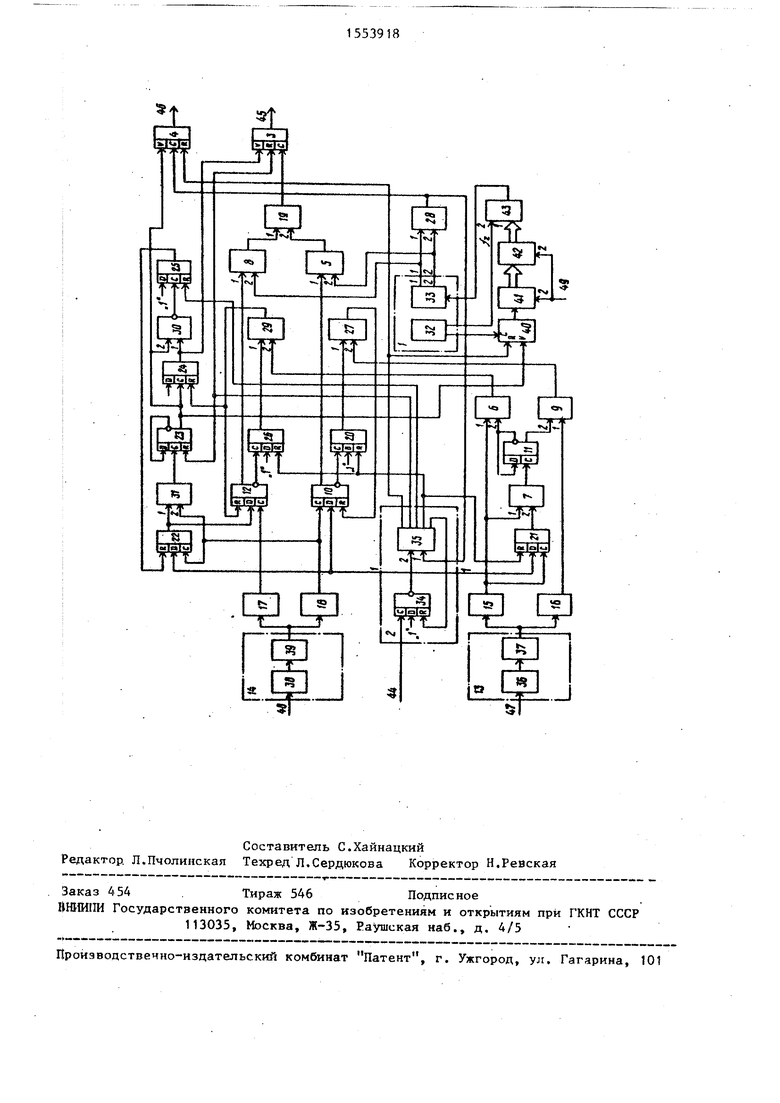

На чертеже показана блок-схема цифрового фазометра.

Цифровой фазометр содержит генератор 1 тактовых импульсов, блок 2 синхронизации, первый 3 и второй 4 счетчики, первый 5, второй 6, третий 7, четертый 8 и пятый 9 элементы И, первый 10, второй 11 и третий 12 триггеры, первый 13, второй 14, третий 15, четвертый 16, пятый 17 и шестой 18 формирователи импульсов, первый элемент ИЛИ 19, четвертый 20, пятый 21, шестой 22, седьмой 23, восьмой 24, девятый 25 и десятый 26 триггеры, второй 27, третий 28 и четвертый 29 элементы ИЛИ, элемент ИЛИ-НЕ 30, шестой элемент И 31, генератор 32 импульсов, седьмой формирователь 33 импульсов, одиннадцатый триггер 34, распределитель 35 импульсов, первый усилитель- ограничитель 36, первый компаратор 37, второй усилитель-ограничитель 38, второй компаратор 39, третий счетчик 40, постоянное запоминающее устройство (ПЗУ) 41, регистр 42 и делитель 43 частоты, причем первый выход генератора 1 тактовых импульсов соединен с вторым входом четвертого элемента И 8 и первым входом третьего элемента ИЛИ 28, второй вход которого соединен с вторым входом первого элемента И 5 и вторым выходом генератора 1 тактовых импульсов, третий выход коOi

СЛ СО СО

00

ю

1

торого соединен с тактовым входом третьего счетчика 40, четвертый выход генератора 1 тактовых импульсов подключен к второму входу лелитепя A3 частоты, первый выход блока 2 синхронизации подсоединен к информационным входам триггеров 10, 21 и 22, второй выход - к входу установки О счетчиков 4 и АО, третий выход - к входам установки О седьмого триггера 23 и первого счетчика 3, четвертый выход - к входу установки О девятого триггера 25, пятый выход - к входам установки О триггеров 20, j 21 и 26, вход синхронизации одиннадцатого триггера 34 является входом блока 2 синхронизации и третьим входом 44 цифрового фазометра, его инверсный выход является первым выходом блока 2

2синхронизации и соединен с вторым входом распределителя 35 импульсов, первый, второй, третий, четвертый выходы которого являются соответственно вторым, третьим, четвертым и пятым 2 выходами блока 2 синхронизации, пятый выход распределителя 35 импульсов соединен с входом установки О одиннадцатого триггера 34, информационный вход которого подключен к шине с уров-зд нем 1, первый вход распределителя

35 импульсов соединен с выходом третьего элемента ИЛИ 28 и входом синхронизации второго счетчика 4, выход первого элемента ИЛИ 19 соединен с входом синхронизации первого счетчика 3, вход разрешения которого подключен к прямому выходу восьмого триггера 24 и первому входу элемента ИЛИ-НЕ 30, вход разрешения второго счетчика 4 соединен с прямым выходом седьмого триггера 23, входом разрешения третьего счетчика 40, входом синхронизации восьмого триггера 24, вторым входом элемента ИЛИ-НЕ 30, выходы первого

3и второго 4 счетчиков являются соответственно первым 45 и вторым 46 выходами цифрового фазометра, прямой выход первого триггера 10 соединен с первым входом первого элемента И 5, выход которого соединен с вторым входом первого элемента ИЛИ 19, первый вход второго элемента И 6 соединен с выходом третьего формирователя 15, входом синхронизации пятого триггера 21, первым входом третьего элемента

И 7, информационный вход второго триггера 11 соединен со своим инверсным выходом и вторым входом второго эле3

4

4

5

5

0

0

5

0

5

0

5

мента И 6, выход которого соединен с вторым входом четвертого элемента ИЛИ 29, выход пятого триггера 21 соединен с вторым входом третьего эле мента И 7, выход которого подключен к входу синхронизации второго триггера 11, прямой выход третьего триггера 12 подключен к первому входу четвертого элемента И 8, выход которого соединен с первым входом первого элемента ИЛИ 19s, второй вход пятого элемента И 9 соединен с прямым выходом второго триггера 11, выход четвертого формирователя 16 импульсов подключен к первому входу пятого элемента И 9, выход которого соединен с вторым входом второго элемента ИЛИ 27, выход шестого формирователя 18 импульсов соединен с вторым входом шестого элемента И 31 и входами синхронизации первого 10 и шестого 22 триггеров, выход второго элемента ИЛИ 27 соединен с входом установки О первого триггера 10, инверсный выход которого соединен с входом синхронизации четвертого триггера 20, прямой выход шестого триггера 22 подключен к первому входу шестого элемента И 31 и информационному входу третьего триггера 12, выход установки О которого соединен с входом установки О, восьмого триггера 24 и выходом четвертого элемента ИЛИ 29, выход пятого формирователя 17 импульсов соединен с входом синхронизации третьего триггера 12, инверсный выход которого связан с входом синхронизации десятого триггера 26, первый усилитель- ограничитель 36 соединен с входом первого компаратора 37, выход которого подключен к входам третьего 15 и четвертого 16 формирователей импульсов, выход второго усилителя-ограничителя 38 соединен с входом второго компаратора 39, выход которого подключен к входам пятого 17 и шестого 18 формирователей импульсов, входы первого 36 и второго 38 усилителей-ограничителей являются входами первого 13 и второго 14 формирователей импульсов и соответственно первым 47 и вторым 48 входами цифрового фазометра, прямые выходы четвертого 20 и десятого 26 триггеров соответственно подключены к первым входам второго 27 и четвертого 29 элементов ИЛИ, прямой, выход девятого триггера 25 соединен с входом установки О шестого триг515

гера 22, информационный вход седьмого триггера 23 подключен к своему инверсному выходу, первый и второй выходы седьмого формирователя 33 являются соответственно первым и вторым выходами генератора 1 тактовых импульсов, первый и второй выходы генератор 32 импульсов являются соответственно третьим и четвертым выходами генера- тора 1 тактовых импульсов, выход третьего счетчика 40 соединен с первым входом постоянного запоминающего устройства 41, второй вход которого соединен с вторым входом регистра 42 и является четвертым входом 49 (Режим цифрового фазометра, выход постоянного запоминающего устройства соединен с первым входом регистра 42, выход которого соединен с первым входом дели- теля частоты 43, вход седьмого формирователя 33 импульсов является входом генератора 1 тактовых импульсов и соединен с выходом делителя 43 частоты, выход шестого элемента И 31 соединен с входом синхронизации седьмого триггера 23, выход элемента ИПИ-НЕ 30 соединен с входом синхронизации девятого триггера 25, к информационным входам четвертого 20, восьмого 24, девятого 25, десятого 26 триггеров подключена шина с уровнем 1.

Цифровой фазометр работает следующим образом.

Синусоидальные или прямоугольные напряжения подаются па первый 47 и второй 48 входы цифрового фазометра, причем напряжение по вдоу 47 являет- crt информационным сигналом. Входные сигналы, пройдя через первый 36 и второй 38 усилители-ограничители, усиливаются и симметрично ограничиваются по амплитуде. С помощью первого 37 и второго 39 компараторов входные сигналы преобразуются в напряжение пря- моугольной формы с уровнями, совместимыми с уровнями используемой серии микросхем. Пятый 7 и иестой 18 формирователи импульсов вырабатывают импульсы, привязанные соответственно к заднему и переднему фронтам опорного сигнала.

В начальный период работы схемы происходит запуск одиннадцатого триггера 34 импульсов с входа 44. Один- иадцатый триггер 34 вырабатывает интервал с уровнем О, который снимает запрет с второго входа распределителя 35 импульсon, в результате чего на

186

выходах тин прднего вырабатываете погледонлтольнгсть импульсов. При тактогшо ИМПУЛЬСЫ с выхода третьего элемента ИЛИ 28 поступают на первый вход распределителя 35 импульсов, на выходах которого начинает вырабатываться последовательность импульсов.

Импульсом с первого выхода обнуляется второй 4 и третий 40 счетчики, а импульсом с второго выхода - седьмой триггер 23 и первый счетчик 3. Импульс с третьего выхода обнуляет девятый триггер 25, импульс с четвертого выхода - четвертый 20, пятый 21 и десятый 26 триггеры. Импульсы с пятого выхода распределителя 35 им пульсов на выходе одиннадцатого триггера 34 устанавливается уровень 1, срывающий работу распределителя 35 импульсов и поступающий на информационные входы пятого 21, первого 10 и шестого 22 триггеров.

Процесс измерения сдвига фаз проходит в два этапа. На первом этапе в зависимости от частоты входного сигнала определяется частота заполнения интервалов разрешения счетчиков. На втором этапе происходит измерение фазового сдвига входного сигнала и периода опорного сигнала.

Первый этап. После обнуления третьего счетчика 40 на его вход разрешения поступает интервал с прямого выхода седьмого триггера 23, соответствующий периоду опорного сигнала. На тактовый вход третьего счетчика 40 поступает частота f,, на выходе которого вырабатывается, цифровой код, соответствующий периоду опорного сигнала. Этот код в качестве адреса поступает на первый вход ПЗУ 41. По команде Режим с четвертого входа 49 цифрового фазометра по этому адресу выбирается коэффициент деления К| и переписывается в регистр 42. С выхода регистра 42 коэффициент деления поступает на первый вход делителя 43 частоты, на второй вход которого поступает частота f с генератора 32 импульсов. В делителе 43 частоты частота f делится на коэффициент К, Поделенная частота поступает не вход формирователя 33 в качестве опорной частоты.

Если частота входного сигнале уменьшается, т.е. увеличивается период входного сигнала, частота fj с генератора 32 импульсов заполняет

5

10

более длинный интервал решения ,гтосту- п4ющии на третий счетчик 40. На ПЗУ 41 поступает адрес, по которому выбирается коэффициент деления Kf с большим числовым значением. С делителя 43 частоты частота заполнения меньшая частоты заполнения До уменьшения чистоты входного сигнала, поступает ни формирователь 33, откуда попадает на счетчики 3 и 4. Таким образом действие схемы коррекции, собранной НЦ третьем счетчике 40, ПЗУ 41t регистре 42, делителе 43 частоты, позволяет менять частоту заполнения, поступающую на счетчики в соответст- с измеиением частоты входного и опорного сигналов, удерживая относи- тфтьную погрешность на постоянном уровне. Повышение точности предлагав- п цифрового фазометра по сравнению с известным происходит за счет использования всех разрядов разрядной сфгки.

Далее следует основной этап - 25 измерения фазового сдвига вход- н0го сигнала относительно опорного.

Третий 15 и четвертый 16 формирователи импульсов вырабатывают импульсы,

15539188

рог о триггера 11 уровень 1, позволяющий импульсу с выхода третьего формирователя импульсов проходить через второй элемент И 6, четвертый элемент ИЛИ 29 на вход установки О третьего триггера 12, запрещая его работу. ЭтиМ формируется конец интервала, поступающий на четвертый элемент И 8. Десятый 26 и четвертый 20 триггеры разрешают третьему 12 и первому 10 триггерам вырабатывать свои интервалы только по одному разу в процессе одного измерения фазы. Это достигается тем, что по окончании интервалов, вырабатываемых третьим 12 и первым 10 триггерами, на инверсных выходах этих триггеров появляется положительный перепад, поступающий на входы синхронизации десятого 26 и четвертого 20 триггеров, который на выходах этих триггеров устанавливает уровень 1, который через четвертый 29 и второй 27 элементы ИЛИ запрещает дальнейшее переключение третьего 12 и первого 10 триггеров до начала следующего этапа измерения фазы. С первого выхода генератора 1 тактовых импульсов на второй вход четвертого

J5

привязанные соответственно к передне- зо элемента И 8 поступает последователь- му и заднему фронтам входного сигнала. Импульс с третьего формирователя 15 имлульсов поступает на первый вход второго элемента И 6, а импульс с четвёртого формирователя 16 импульсов - ,, на) первый вход пятого элемента И 9.

ность импульсов, которая заполняет интервал, сформированный третьим триггером 12 и поступающий на первый вх д четвертого элемента ИЛИ 29. С второго выхода генератора 1 тактовых импульсов последовательность импульсов, - сдвинутая на полперйода относительно последовательности на первом выходе генератора 1 тактовых импульсов, поступает на второй вход первого элемента И 5 и заполняет интервал, сформированный триггером 10. Интервалы, заполненные импульсами, с выходов четвертого 8 и первого 5 элементов И поступают на первый и второй входы первого элемента ИЛИ 19. Так как импульсы, заполняющие интервалы, разнесены на полпериода, то область перекрытия интервалов отмечается удвоением частоты следования импульсов. Последовательность импульсов с выхода первого элемента ИЛИ 19 поступает на вход синхронизации первого счетчика 3, на выходе которого получается код, соответствующий произведению двойного сдвига фаз (2) между опорным и входным сигналом на частотный коэффициент (Kf). На втором счетчике 4 из- за того, что частота счетных импульсов

Первый импульс с выхода третьего формирователя 15 импульсов, поступающий на, вход синхронизации пятого триггера 21, устанавливает на его выходе уровень 1, который разрешает прохождение импульса с выхода третьего формирователя 15 импульсов через третий элемент И 7 на вход синхрони- за(ции второго триггера 11 и устанавливает на прямом выходе второго триггера 11 уровень 1, который разре- maieT прохождение импульса с выхода четвертого формирователя 16 импульсов через пятый элемент И 9 и второй элемент ИЛИ 27 на вход установки О первого триггера 10 и срывает его работу, формируя конец интервала, поступающего на первый вход первого элемента И 5. Второй импульс с выхода третьего формирователя 15, поступающий через третий элемент И 7 на вход синхронизации второго триггера 11, устанавливает на ийверсном выходе вто

элемента И 8 поступает последователь-

ность импульсов, которая заполняет интервал, сформированный третьим триггером 12 и поступающий на первый вх д четвертого элемента ИЛИ 29. С второго выхода генератора 1 тактовых импульсов последовательность импульсов, - сдвинутая на полперйода относительно последовательности на первом выходе генератора 1 тактовых импульсов, поступает на второй вход первого элемента И 5 и заполняет интервал, сформированный триггером 10. Интервалы, заполненные импульсами, с выходов четвертого 8 и первого 5 элементов И поступают на первый и второй входы первого элемента ИЛИ 19. Так как импульсы, заполняющие интервалы, разнесены на полпериода, то область перекрытия интервалов отмечается удвоением частоты следования импульсов. Последовательность импульсов с выхода первого элемента ИЛИ 19 поступает на вход синхронизации первого счетчика 3, на выходе которого получается код, соответствующий произведению двойного сдвига фаз (2) между опорным и входным сигналом на частотный коэффициент (Kf). На втором счетчике 4 из- за того, что частота счетных импульсов

в два раза выше, чем при счете фазы, формируется код, соответствующий произведению двойного периода (2Р) опорного сигнала на частотный коэффициент (К-). Полученные коды 2уКс и 2Р-К ,, соответственно с первого и второго выходов цифрового фазометра поступают в устройство, которое вычисляет угол (V1), соответствующий фазовому сдвигу между опорным и входным сигналом

Щш Таким образом, из данной формулы видно, что ц( зависит только от у и Р и не зависит от частоты входного сигнала, так как коэффициент Кр,зависящий от частоты входного сигнала, сокращается. Следовательно, точность определения определяется только разрядной сеткой счетчика, а она постоянна для всех частот входных сигналов. Формула изобретения

Цифровой фазометр по авт. св. № 1406515, отличающийся

Q

5

0 5

тем, что, с целью увеличения диапачана частот входных сигналов при сохранении точности измерения сдвига фаз для заданной разрядной сетки счетчиков в него введены счетчик, постоянное запоминающее устройство, регистр, делитель частоты, причем выход седьмого триггера соединен с входом разрешения счетчика, второй выход блока синхронизации соединен с входом сброса счетчика, тактовый вход которого подключен к третьему входу генератора тактовых импульсов, четвертый выход генератора тактовых импульсов соединен с вторым входом делителя частоты, выход счетчика соединен с первым входом постоянного запоминающего устройства, выход которого соединен с первым входом регистра, второй вход которого соединен с вторым входом постоянного запоминактщего устройства и является четвертым входом цифрового фазометра, выход регистра соединен с первым входом делителя частоты, выход которого соединен с входом генератора тактовых импульсов.

IS-ЫУI

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1986 |

|

SU1368807A1 |

| Цифровой фазометр | 1988 |

|

SU1511706A1 |

| Цифровой фазометр | 1986 |

|

SU1406515A1 |

| Цифровой фазометр | 1982 |

|

SU1092430A1 |

| Цифровой фазометр | 1980 |

|

SU938197A1 |

| Многоканальный фазометр | 1989 |

|

SU1720028A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Цифровой фазометр для определения фазы дисбаланса ротора | 1990 |

|

SU1793389A1 |

| Фазометр | 1991 |

|

SU1817037A1 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1829115A1 |

Изобретение относится к измерительной технике и может быть использовано при создании быстродействующих цифровых фазометров повышенной точности, а также высокоточных преобразователей фаза-код для управляющих цифровых вычислительных систем. Цель изобретения - увеличение диапазона частот входных сигналов при сохранении точности измерения сдвига фаз для заданной разрядной сетки счетчиков. Поставленная цель достигается введением в устройство по авт.св. N 1406515 третьего счетчика, постоянного запоминающего устройства, регистра и делителя частоты. 1 ил.

| Способ защиты от разрушения железных защитных трубок термопар, измеряющих температуру в ванных печах, от электролитической коррозии | 1957 |

|

SU113340A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой фазометр | 1986 |

|

SU1406515A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-03-30—Публикация

1988-07-07—Подача