ел

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелометр | 1980 |

|

SU1062717A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 2022 |

|

RU2785274C1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1506570A1 |

| Цифровой адаптивный синхронизатор | 1980 |

|

SU922708A1 |

| Устройство синхронизации | 1984 |

|

SU1223390A1 |

| Многоканальное устройство тестового контроля логических узлов | 1990 |

|

SU1837295A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1370643A2 |

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1718215A1 |

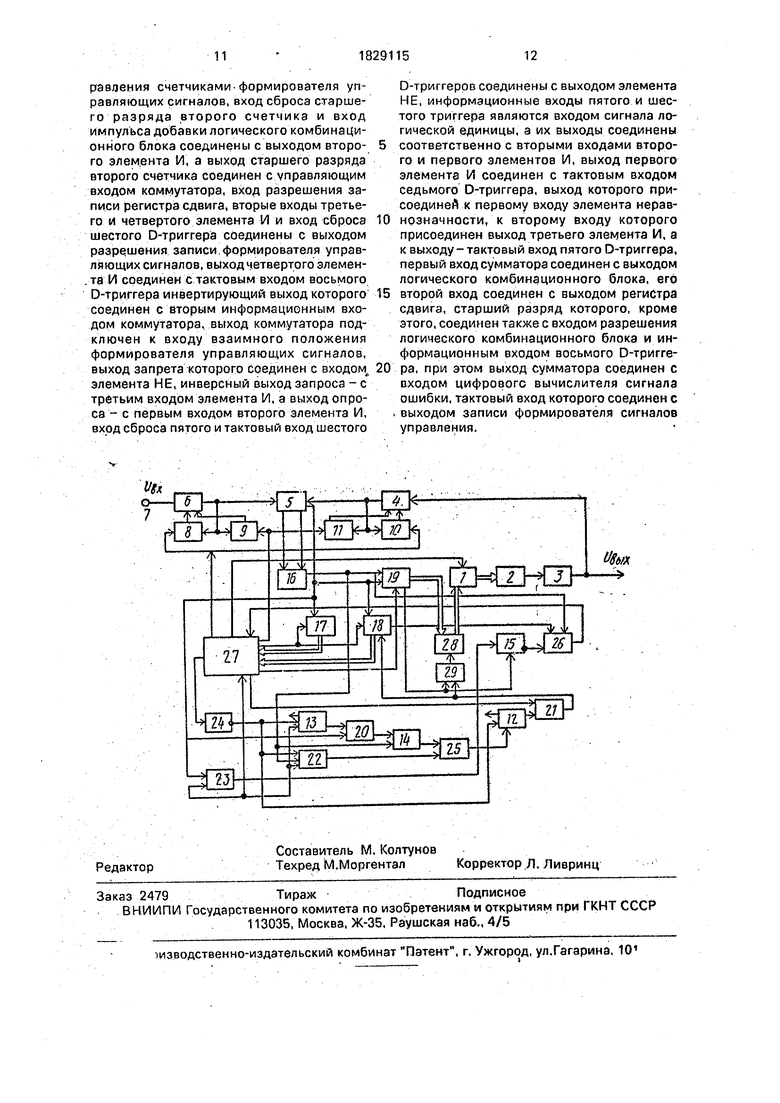

Использование: техника связи, устройства авторегулирования частоты и фазы сигналов. Сущность изобретения: устройство фазовой автоподстройки частоты содержит цифровой вычислитель 1 сигнала ошибки, цифроаналоговый преобразователь 2. управляемый генератор 3, первый 4 и второй 6 усилители частоты с переменным коэффициентом деления, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой D-триггеры 8-15, RS-триггеры 16. первый и второй счетчики 17 и 18, регистр сдвига 19, первый, второй, третий и четвертый элементы И 20-23, элемент НЕ 24, элемент неравнозначности 25, коммутатор 26, формирователь 27 управляющих сигналов, сумматор 28 и логический комбинационный блок 29. В устройстве достигается повышение точности синхронизации.1 ил.

Изобретение относится к технике связи и может быть использовано в устройствах авторегулирования частоты и фазы сигналов.

Цель изобретения заключается в уменьшении величины фазовой ошибки синхронизации и расширении полосы захвата за счет использования дихотомического принципа опроса взаимного положения значащих моментов входного и выходного сигналов.

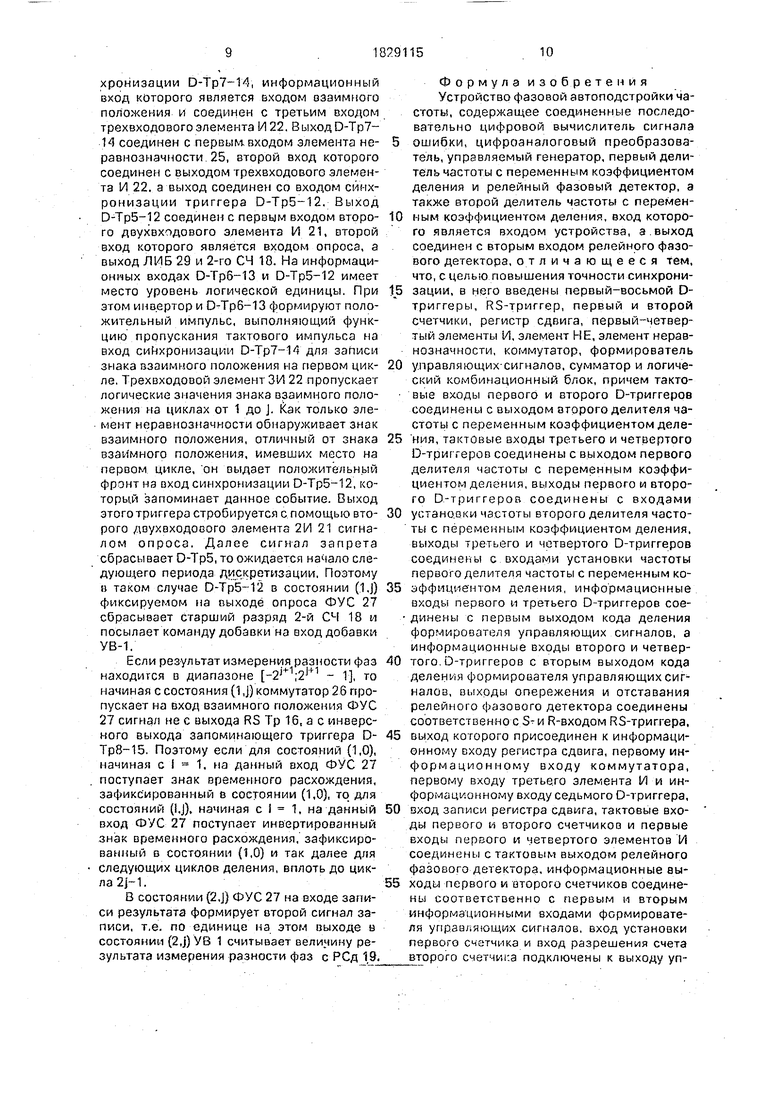

На чертеже представлена блок-схема устройства.

Устройство фазовой автоподстройки частоты содержит соединенные последовательно цифровой вычислитель 1 (ЦВ) сигнала ошибки, цифроаналоговый преобразователь 2, управляемый генератор 3, первый делитель 4 частоты с переменным коэффициентом деления и релейный фазовый детектор 5, а также второй делитель 6 частоты с переменным коэффициентом, вход которого является входом 7 устройства, а выход соединен с вторым входом релейного фазового детектора 5.

Устройство содержит также первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой D-триггеры 8, 9, 10, 11, 12, 13, 14, 15 (DTp), RS-триггер 16 (RSTp), первый и второй счетчики 17 и 18 (СЧ), регистр сдвига 19 (PC), первый, второй, третий и четвертый элементы И 20, 21, 22 и 23, элемент НЕ 24, элемент неравнозначности 25. коммутатор 26, формирователь 27 управляющих сигналов (ФУС), сумматор 28 и логический комбинационный блок 29.

Тактовые входы первого и второго D- триггеров 8 и 9 соединены с выходом второго делителя 6 частоты с переменным коэффициентом деления, тактовые входы

ел

третьего и четвертого D-триггеров 10 и 11 соединены с выходом первого делителя 4 частоты с переменным коэффициентом деления (ДПКД), выходы первого и второго D-триггеров 8 и 9 соединены с входами ус- тановки частоты второго делителя 6 частоты с переменным коэффициентом деления. Выходы третьего и четвертого D-триггеров 10 и 11 соединены с входами установки частоты первого делителя 4 с переменным ко- эффициентом деления, информационные входы первого и третьего D-триггеров 8 и 10 соединены с первым выходом кода деления формирователя 27 управляющих сигналов, а информационные входы второго и четвер- того D-триггеров 9 и 11 с вторым выходом кода деления формирователя 27 управляющих сигналов. Выходы опережения и отставания релейного фазового детектора 5 соединены соответственно с $- и R-входами RS-триггера 16, выход которого присоединен к информационному входу регистра сдвига 19, первому информационному входу коммутатора 26. первому входу третьего элемента И 22 и информационному седьмо- го Ь-триггера 14. Вход записи регистра 19 сдвига, тактовые входы первого и второго счетчиков 17 и 1.8, первые входы первого и четвертого элементов И 20 и 2.3 соединены с тактовым выходом релейного фазового де- тектора 5 (РФД). Информационные выходы первого и второго счетчиков 17 и 18 соединены соответственно с первым и вторым информационным входами формирователя 27 управляющих сигналов, вход установки пер- вого счетчика 17 и вход разрешения счета второго счетчика 18 подключен к выходу управления счетчиками формирователя 27 управляющих сигналов. Вход сброса старшего разряда второго счетчика 18 и вход импульса добавки логического комбинаци- онного блока 29 (ЛКБ) соединены с выходом второго элемента И 21, а выход старшего разряда второго счетчика 18 соединен с управляющим входом коммутато- ра 26. Вход разрешения записи регистра 19 сдвига, вторые входы третьего и четвертого элементов И 22 и 23 и вход сброса шестого D-триггера 13 соединены с выходом, раэре- ; шения записи формирователя 27 управляю- щих сигналов. Выход четвертого элемента Л 23 соединен с тактовым, входом восьмого D-триггера 15, инвертирующий выход которого соединен с вторым информационным входом коммутатора 26, а выход коммутато- ра 26 подключен к входу взаимного положе- ния формирователя 27 управляющих сигналов выход запрета которого соединен с входом элемента НЕ 24, инверсный выход запроса - с входом третьего элемента И 22,

а выход опроса - с первым входом второго элемента И 21, Вход сброса пятого и тактовый вход шестого D-триггеров 12 и 13 соединены с выходом элемента НЕ 24, информационные входы пятого и шестого триггера 12 и 13 являются входом сигнала логической единицы, а их выходы соединены соответственно с вторыми входами второго и первого элементов I/I 21 и 20. Выход первого элемента И 20 соединен с тактовым входом седьмого D-триггера 14, выход которого присоединен к первому входу элемента 25 неравнозначности, к второму входу которого присоединен выход третьего элемента И 22, а к выходу - тактовый вход пятого D-триггера 12, Первый вход сумматора 28 соединен с выходом логического комбинационного блока 29, его второй вход соединен с выходом регистра сдвига 19 (РСд), старший разряд которого кроме этого соединен также с входом разрешения логического комбинационного блока 29 и информационным входом восьмого D-триггера 15. Выход сумматора 28 соединен с входом цифрового вычислителя 1 сигнала ошибки, тактовый вход которого соединен с выходом записи формирователя 27 сигналов управления..

Принцип работы устройства заключается в следующем.

Пусть номинальные значения частоты и периода сигнала UBx на выходе раины соответственно fi и Ti, а номинальные значения .частоты и периода сигнала Увых, на выходе равны соответственно f. и Та. Если временно считать f 1 и fz целыми числами, соответственно равными значениям частот сигналов UBX и ивых.. выраженным в некоторой системе единиц, то величина Q равная отношению наибольшего общего делителя чисел fi и fe к их произведению и выраженная в соответствующих единицах времени, имеет смысл минимального интервала времени, до которого можно свести временное расхождение между значащими моментами на входах импульсов РФД 5 путем выборов этих значащих моментов, т.е. использования ДПКД 4 и 6. Пусть Тт Mi Q, а Та -М2 О, тогда временное расхождение в начале и а конце интервала MiMz Q МиТа -MaTi, одинаково. По смыслу величины Qсуществуют числа Кп и Kiz, такие что

. Q

(1)

Тогда существует и пара дополнительных коэффициентов Кц, Kiz таких что

К1ГГ1-К12 Т2 -Q,

(2)

причем

Kif + .

K12 + .

Имея первые пары прямых и дополнительных коэффициентов, можно получить соответствующие вторые пары коэффициентов; умножив их на два и взяв по модулю М (для первого сигнала с периодом Т т) или Mi (для периода Та):

K21tl

( j)modM2 :(2Ki2+(rmodMi.

При этом:

К21+Т1 - К22+Т2 2 Q

K2fTi-K22 T2 -2Q

Аналогично могут быть, получены пары прямых и дополнительных коэффициентов: Кл и К|2 со следующими свойствами:

Кц+Т1 - Ki2+T2 - 2м Q

KifTi-Kr2-T2 М2

М2 /:.

Ки) (2K(M)/i4MmodM2 )(2K(i-i) VodMi.

В связи с этими соотношениями может быть предложена следующая процедура измерения разности фаз. В начале процесса измерения фиксируется знак временного расхождения между значащими моментами импульсов на входах РФД 5, который посылается сразу же в VB 1. Для первого цикла деления выбирается та прямая или дополнительная j-ая пара коэффициентов К)ч и при установке которой временное расхождение будет меньше.

Пусть в начале измерения разности фаз значащий момент сигнала на первом входе РФД 5 отстает от значащего момента сигнала на втором входе РФД 5 на величину А, т.е. его фаза меньше. В этом случае следует выбрать дополнительную l-ую пару коэффициентов, при которых:

- - -2jH Q

05).

Знак временного расхождения после первого цикла деления с коэффициентами j-ой пары показывает вес (0 или 1) с которым следует брать -ый по старшинству разряд результата измерения. Для следующего цикла деления выбирается та прямая или

5

0

5

дополнительная (1-1) пара коэффициентов KO-tp и К0-1)2 , при установке которой временное расхождение будет меньше.

Знак временного расхождения после 5 второго цикла деления с коэффициентами )-ой пары показывает вес (0,1), с которым следует брать (|-1)-ый по старшенству разряд результата измерения.

После окончания j циклов деления, ко- 0 эффициенты которых выбираются по вышеописанным правилам, результат измерения величины разности фаз может быть представлен в виде параллельного кода, старший разряд которого представляет собой знак временного расхождения после первого цикла деления, а младший - знак временного расхождения после последнего j-oro цикла деления,

Однако после j циклов деления следует провести еще J циклов с коэффициентами, дополняющими соответствующий коэффициенты в первой фазе измерения (если в первом цикле была прямая пара, то в (J+1)- ой должна быть дополнительная, и наоборот, аналогично для 2-ого и (+2}-ого цикла и т.д.

С точки зрения реализации вышеописанного алгоритма коэффициенты не являются непосредственно коэффициентами деления .первого и второго ДПКД б и 4, а строятся из различного числа четырех базовых коэффициентов деления ДПКД Ki,t(2), К2,1(2), Кз.1(2), К4,1(2), взятых в различной последовательности. Базовые коэффициенты деления характеризуются двумя основными свойствами,.

Во-первых, если

Кп+() Посл(К11,К21,Кз1,К11),

. где Посл(...)- определенная последовательность базовых коэффициентов, то

K. ПОСЛ(К12,К22,К32,К42)

Данное свойство позволяет сделать управление коэффициентами деления общим для первого и второго ДПКД 6 и 4,

Во-вторых для Ki,i{2) и Ki,i(2} первые базовые коэффициенты последовательностей совпадают.

Данное свойство позволяет начинать каждый цикл деления независимо от знакового индекса коэффициента Ki,i(2) .

Таким образом, интервал дискретизации в заявляемом УФАПЧ, т.е. интервал времени, на котором производится одно измерение разности фаз и вычисление величины измерения частоты УГ 1, причем вход результата измерения разности фаз содер0

5

0

5

0

5

жит J разрядов, состоит из 2 циклов деления, каждый из которых в свою очередь состоит из определенного числа (|) делений с одним из базовых коэффициентов деления, взятого го модулю J, т.е. без стар- шего разряда и знака временного расхождения значащих моментов импульсов на входах РФД 5 (при номере цикла не большем J; число (|) зависит от номера цикла деления).

Возможность .неограниченного расширения диапазона измеряемой величины разности фаз, заключается в том, что если достигнута граница диапазона, т.е. все разряды результата измерений одинаковы, ин- тервал дискретизации может быть прерван после 8 циклов и начат сначала без возвращения к начальному взаимному положению значащих моментов импульсов на входах РФД 5.

Рассмотрим теперь принцип работы УФАПЧ (фиг.1) с точки зрения взаимодействия элементов его структурной схемы, К моменту завершения некоторого интервала дискретизации первый счетчик СЧ 17 уста- новлен в единицу, а второй СЧ 18 в нуль. Приняв эту информацию на своих соответственно первых и вторых информационных входах ФУС 27 по переднему фронту сигнала на тактовом выходе, РФД 5 уста- навливает двухбитовый код первой пары коэффициентов деления на выходах ДТр 1,3-8,10 и ДТр 2; 4-9,11. Для каждого цикла деления первая пара базовых коэффициентов не зависит от знака временного расхож- дения одновременно ГФВП фиксирует знак временного расхождения в начале первого цикла деления.

На выходе разрешения записи ФУС 27 единица имеется в тех случаях, когда на его первых и вторых информационных входах содержится пара (Т,). Поэтому во время де ления (1,0) по заднему фронту тёктового сиг- нала с выхода РФД 5 записывается в младший разряд РСд 19 содержимое RS Тр 19, которое имеет смысл разности фаз, измеряемой в данном интервале дискретизации. «

По переднему фронту следующего им- пульса на тактовом выходе РФД 5 первый Сч 1.7 уста на вливается в состояние 2, поэто- му это.деление можно обозначить символами (2,0). Используя информацию на входе взаимного положения, ФУС 27 уже к пере- днему фронту этого импульса подготавливает код коэффициентов для второго деления, который записывается на выходах первого 8 и третьего 10 также по переднему Фронту.;

В состоянии (2,0) ФУС 27 также выдает первый сигнал на вход записи ЦВ 1 с выхода записи результата. ЦВ 1, считав содержимое РСд 19, запоминает младший разряд в качестве знака результата измерений.

По переднему фронту каждого из следующих импульсов на тактовом выходе РФД5 состояние 1-го СЧ 17 увеличивается на единицу. моментам ФУС 27 подготавливают код базовых коэффициентов деления. Этот процесс продолжается до деления (1,0), которое в соответствии с номером цикла и содержимым ФУС 27 является последним в данном цикле. При этом на выходе последнего деления ФУС 27 появляется единица. Эта единица поступает на вход разрешения параллельной установки в единицу с 1-го СЧ 17 и на вход разрешения счета 2-го СЧ 18, так что по переднему фронту следующего импульса на тактовом выходе РФД 5 возникает состояние (1,1).

Перейдем теперь к состоянию (1J-1). По заднему фронту импульса на тактовом выходе РФД 5 в этом состоянии на выходах РФД 19 содержатся знак (старший разряд) и J-1 старших разрядов результата измерения разности фаз.

Поэтому в состоянии (1J) по заднему фронту импульса на тактовом выходе РФД 5 в РСд 19 содержится уже весь код величины результата измерения разности фаз, а по D-Tp8-15 знак той величины.

Начиная с состояния (2.J) и до конца интервала дискретизации (если 2-ой СЧ 18 не сбрасывается в нуль) на выходе запрета ФУС 27 появляется единица, которая через схему НЕ 24 запрещает 3 и 22. ДТ 6-13,1-го элемента 1Л 20 и элемента неравнозначности 25 анализировать данные с RS-Tp 16. Если до состояния (1,j) включительно элемент неравнозначности 25 не зафиксировал хотя бы одного изменения знака на выходе RS-Tp 16 с помощью схем 13, 20,14 и 22. это означает, что измеряемая разность выходит за границы диапазона измерений + 1; - 1, и следует начать следующий интервал дискретизации без возвращения к начальному временному расхождению, сделав соответствующую добавку в ЦВ 1. Вход инвертора 24 является входом запрета и соединен с первым входом трехвходового элемента И 22, а выход инвертора соединен со входом синхронизации D-Tp6-13 и со входом установки в нуль D-Tp5-12. Вход установки в нуль О-Трб-13 является входом разрешения записи и соединен со вторым входом элемента И 22. Выход D- Трб-13 соединен со вторым входом первого СЧ 20, первый вход которого является тактовым, а выход.ссединен со входом синхронизации D-Tp7-14, информационный вход которого является входом взаимного положения и соединен с третьим входом трехвходового элемента И 22. ВыходО-Тр7- 14 соединен с первым, входом элемента неравнозначности. 25, второй вход которого соединен с выходом трехвходового элемента И 22. а выход соединен со входом синхронизации триггера 0-Тр5-12. Выход D-Tp5-12 соединен с первым входом второго двухвходового элемента И 21, второй вход которого является входом опроса, а выход ЛИБ 29 и 2-го СЧ 18. На информационных входах 0-Трб-13 и D-Tp5-12 имеет место уровень логической единицы. При этом инвертор и О-Трб-13 формируют положительный импульс, выполняющий функцию пропускания тактового импульса на вход синхронизации D-Tp7-14 для записи знака взаимного положения на первом цикле. Трехвходовой элемент ЗИ 22 пропускает логические значения знака взаимного положения на циклах от 1 до J. Јак только элемент неравнозначности обнаруживает знак взаимного положения, отличный от знака взаимного положения, имевших место на первом цикле, он выдает положительный фронт на вход синхронизации D-Tp5-12, который запоминает данное событие. Выход этого триггера стробируется с помощью второго двухвходового элемента 21/1 21 сигналом опроса. Далее сигнал запрета сбрасывает О-Тр5, то ожидается начало следующего периода дискретизации, Поэтому в таком случае D-Tp5-12 в состоянии (1,j) фиксируемом на выходе опроса ФУС 27 сбрасывает старший разряд 2-й СЧ 18 и посылает команду добавки на вход добавки УВ-1.

Если результат измерения разности фаз находится в диапазоне -2 +1;2 1 - 1, то начиная с состояния (1 ,j) коммутатор 26 пропускает на вход взаимного положения ФУС 27 сигнал не с выхода RS Тр 1.6, а с инверсного выхода запоминающего триггера D- Тр8-15. Поэтому если для состояний (1,0), начиная с I 1, на данный вход ФУС 27 поступает знак временного расхождения, зафиксированный в состоянии (1,0), то для состояний (I,J), начиная с I 1, на данный вход ФУС 27 поступает инвертированный знак временного расхождения, зафиксированный в состоянии (1,0) и так далее для следующих циклов деления, вплоть до цикла 2J-1.

В состоянии (2.J) ФУС 27 на входе записи результата формирует второй сигнал записи, т.е. по единице на этом выходе в состоянии (2J) УВ 1 считывает величину результата измерения разности фаз с РСд 19.

Формула изобретения Устройство фазовой автоподстройки частоты, содержащее соединенные последовательно цифровой вычислитель сигнала 5 ошибки, цифроаналоговый преобразователь, управляемый генератор, первый делитель частоты с переменным коэффициентом деления и релейный фазовый детектор, а также второй делитель частоты с перемен0 ным коэффициентом деления, вход которого является входом устройства, а.выход соединен с вторым входом релейного фазового детектора, от личающееся тем, что, с целью повышения точности синхрони5 зации, в него введены первый-восьмой D- триггеры, RS-триггер, первый и второй счетчики, регистр сдвига, первый-четвер- тый элементы И, элемент НЕ, элемент неравнозначности, коммутатор, формирователь

0 управляющих-сигналов, сумматор и логический комбинационный блок, причем такто- вые входы первого и второго D-триггеров соединены с выходом второго делителя частоты с переменным коэффициентом деле5 ния, тактовые входы третьего и четвертого D-тригтеров соединены с выходом первого делителя частоты с переменным коэффициентом деления, выходы первого и второго D-триггеров соединены с входами

0 установки частоты второго делителя часто ты с переменным коэффициентом деления.

выходы третьего и четвертого D-триггеров

соединены с входами установки частоты

первого делителя частоты с переменным ко5 эффициентом деления, информационные

входы первого и третьего D-триггеров сое динены с первым выходом кода деления

формирователя управляющих сигналов, а

информационные входы второго и четвер0 того. D-триггеров с вторым выходом кода деления формирователя управляющих сигналов, выходы опережения и отставания релейного фазового детектора соединены соответственное 3-й R-входом RS-триггера,

5 выход которого присоединен к информационному входу регистра сдвига, первому ин- формационному входу коммутатора, первому входу третьего элемента 1/1 и информационному входу седьмого D-триггера,

0 сход записи регистра сдвига, тактовые входы первого и второго счетчиков и первые входы первого и четвертого элементов Л соединены с тактовым выходом релейного фазового детектора, информационные вы5 ходы первого и второго счетчиков соединены соответственно с первым и вторым информационными входами формирователя управляющих сигналов, вход установки первого счетчика и вход разрешения счета второго счетчика подключены к выходу управнения счетчиками.формирователя управляющих сигналов, вход сброса старшего разряда второго счетчика и вход импульса добавки логического комбинационного блока соединены с выходом второго элемента И, а выход старшего разряда второго счетчика соединен с управляющим входом коммутатора, вход разрешения записи регистра сдвига вторые входы третьего и четвертого элемента VI и вход сброса шестого D-триггера соединены с выходом разрешения записи.формирователя управляющих сигналов, выход четвертого элемен- .та И соединен с тактовым входом восьмого D-триггера инвертирующий выход которого соединен с вторым информационным входом коммутатора, выход коммутатора подключен к входу взаимного положения формирователя управляющих сигналов, выход запрета которого соединен с входом элемента HEt инверсный выход запроса - с третьим входом элемента И, а выход опроса - с первым входом второго элемента И, вход сброса пятого и тактовый вход шестого

D-триггеррв соединены с выходом элемента НЕ, информационные входы пятого и шестого триггера являются входом сигнала логической единицы, а их выходы соединены соответственное вторыми входами второго и первого элементов И, выход первого элемента И соединен с тактовым входом седьмого D-триггера, выход которого при- соединей к первому входу элемента нерав0 нозначности, к второму входу которого присоединен выход третьего элемента И, а к выходу-та кто вы и вход пятого D-триггера, первый вход сумматора соединен с выходом логического комбинационного блока, его

5 второй вход соединен с выходом регистра сдвига, старший разряд которого, кроме этого, соединен также с входом разрешения логического комбинационного блока и информационным входом восьмого D-тригге0 ра, при этом выход сумматора соединен с

входом цифрового вычислителя сигнала

ошибки, тактовый вход которого соединен с

. выходом записи формирователя сигналов

управления.

| Устройство фазовой автоподстройки частоты | 1986 |

|

SU1443173A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-07-23—Публикация

1990-05-31—Подача